### GPGPU

#### General Purpose Graphics Processing Unit

Thomas Swift Sean Brennan Andrew Wong

# Outline

- GPGPU Overview

- Terminology

- Graphics Pipeline

- CPU vs GPU

- CUDA

- NVIDIA's Kepler & AMD's GCN Architectures

- PTask

# **GPUs in Action**

(product placement)

# **Graphics Processing Unit**

- Traditionally used for 3D rendering, but now also used for large computations

- Originally special function units with specialized HW & ISAs

- Good at applying same operation to large number of independent elements, in parallel

- Why GPUs?

- High performance/throughput for massively parallel computations

- Much higher arithmetic capability and memory bandwidth than even high-end CPUs

# Terminology

Streaming Processor abstraction

- Programming model designed to abstract away all graphics terminology of GPU

- Stream

- Ordered set of data

- Kernel

- Function applied element-wise to a set of streams and that outputs one or more streams

- SIMD Single Instruction, Multiple Data

SPMD Single Program, Multiple Data

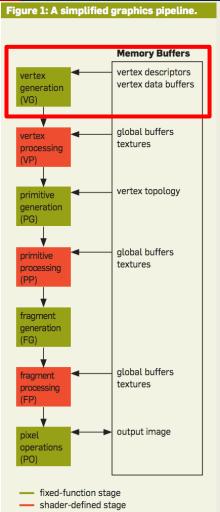

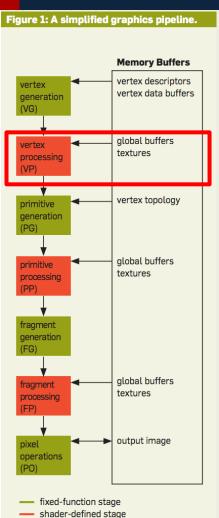

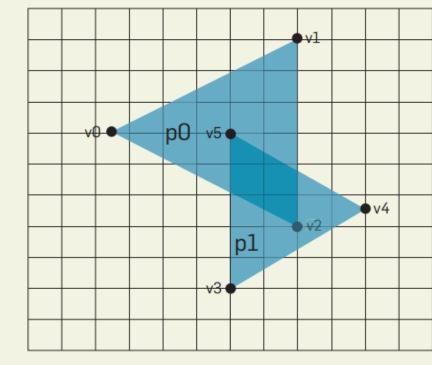

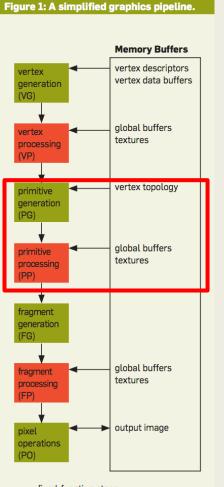

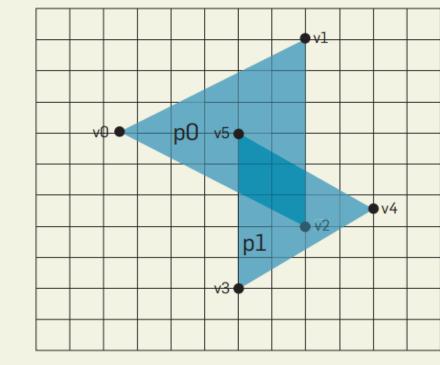

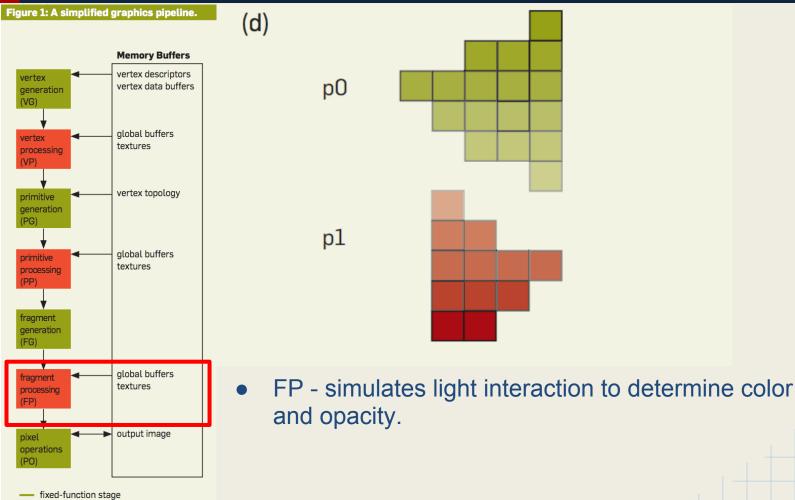

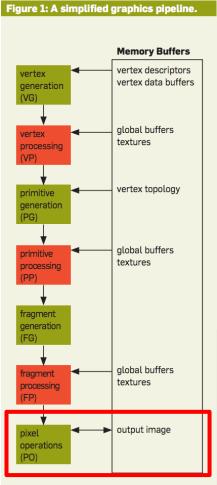

# **Graphics Pipeline**

- A series of generation and processing stages

- Connected by stream-entities

- Processing stages are programmable

- Shader functions used to alter appearance of graphical output.

Figure 1: A simplified graphics pipeline.

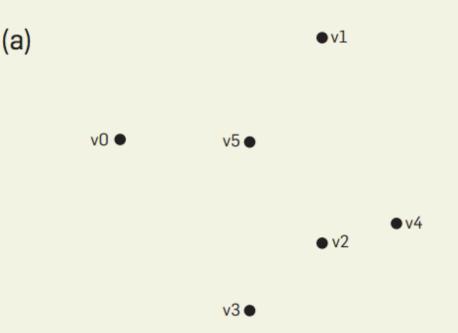

## Vertex Generation

VG - prefetches vertex and texture data from memory and constructs a stream of vertex data.

## **Vertex Processing**

(b)

• VP - programmable operation on each vertex (e. g. computing projection from 3D space to screen).

# Primitive Generation Primitive Processing

(b)

- PG groups vertices into ordered streams of primitives

- PP Produces zero or more output primitives.

fixed-function stage

shader-defined stage

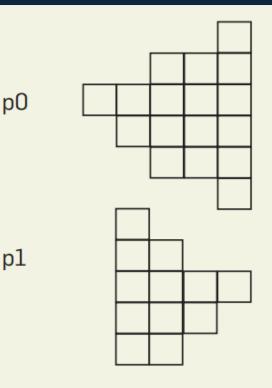

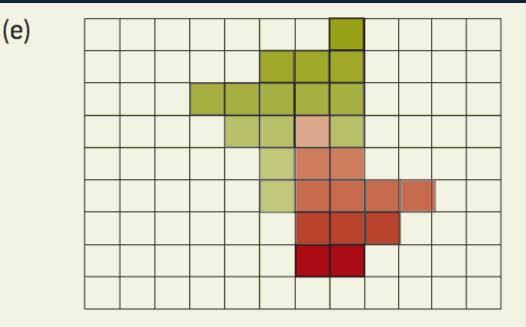

# **Fragment Generation**

(c)

fixed-function stage

shader-defined stage

FG - performs rasterization through sampling. Distance from camera and other parameters are saved

## **Fragment Processing**

shader-defined stage

# **Pixel Operations**

fixed-function stage

shader-defined stage

• PO - calculates image pixel values based on distance and obstructions.

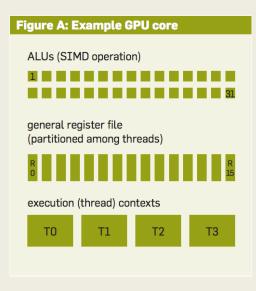

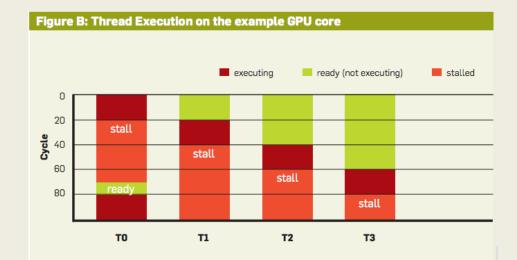

# Hardware Multithreading

- Threads stall due to memory accesses

- Hardware contains multiple execution units to perform instructions from other threads when a thread stalls.

# CPU vs GPU

#### <u>CPUs</u>

- Parallelism through time multiplexing

- Emphasis on low memory latency

- Allows wide range of control flows + control flow optimizations

- Low-latency caches that allow performant out-of-order execution

- Very high clock speeds

#### <u>GPUs</u>

- Parallelism through space multiplexing

- Emphasis on high memory throughput

- Very control flow restricted

- High-latency caches that tend to be read-only

- Mid-tempo clock speeds

#### Other GPU Points

- Power efficient for large parallel operations

- Inexpensive on a TFLOP basis

- Difficult to program but getting better!

# CUDA

- Compute Unified Device Architecture

- Platform and programming model by Nvidia

- Introduced in 2006 w/ GeForce 8800 GTX

- First architecture targeted at general purpose use

- CUDA C provides high-level language familiar to most programmers

- ALUs built for more general types of computation

- Unified Shader Model improves use of GPU resources

### **Unified Shader Models**

- Unified Shader Architecture: all GPU units designed to handle any shader

- Unified Shader Model: all shaders have similar instruction set

- Unified *Model* does NOT require Unified *Architecture*!

- Advantages over "classical" model:

- more dynamic and flexible use of GPU resources

- open to different workflows

- both of these make USA/USM well-suited to GPGPU programming

# Programming in CUDA

- CUDA C: good old C + a few new functions, structs, and primitives

- Kernel functions: \_\_global\_\_ and \_\_device\_

- global : code executed on GPU from CPU

- \_\_\_\_\_device\_\_\_: code executed on GPU from other GPU functions

- Grid abstraction: spatial multiplexing

- $\circ \quad \text{grid} \rightarrow \text{blocks} \rightarrow \text{threads}$

- $\circ$  grid (2D) + block (3D) = 5 degrees of indexing freedom

- SIMD paradigm: Single Instruction Multiple Data

- well-suited to data-parallel tasks

- conditionals are costly and should be avoided

# CUDA Workflow

1. allocate data in main memory and on GPU

- 15 // allocate arrays on host 16 a\_h = (float \*)malloc(size); 17 b\_h = (float \*)malloc(size); 18 19 // allocate array on device 20 cudaMalloc((void \*\*) &a\_d, size);

- 2. move data from  $26 \\ 27 \\ MM \rightarrow GPU$  // copy data from host to device cudaMemcpy(a\_d, a\_h, sizeof(float) \* N, cudaMemcpyHostToDevice);

3. issue kernel over given block + thread count

// Part 2 of 2. Call incrementArrayOnDevice kernel

incrementArrayOnDevice <<< nBlocks, blockSize >>> (a\_d, N);

# CUDA Workflow

37 38

- 4. kernels execute in parallel

5. copy data from  $GPU \rightarrow MM$

// Retrieve result from device and store in b\_h

cudaMemcpy(b\_h, a\_d, sizeof(float) \* N, cudaMemcpyDeviceToHost);

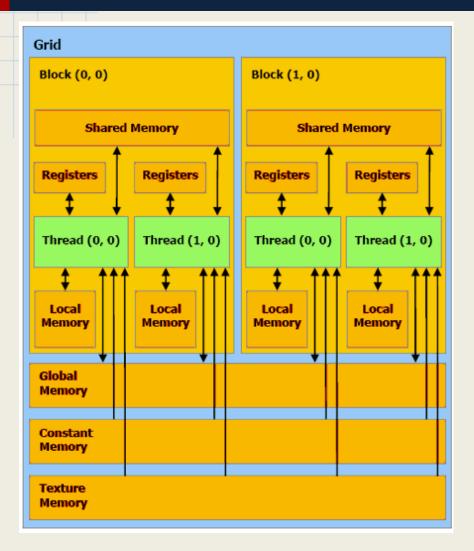

# **CUDA Memory Layout**

- Per-thread registers

Very fast: lifetime of

- Very fast; lifetime of thread

- Per-block shared memory

- Very fast; lifetime of block

- All-block global memory

- ~100x slower than shmem

- high throughput achieved through coalescing

- Per-thread local memory

- o gotcha! as slow as global

- All-block constant memory

- half-warp broadcast reduces bandwidth

- All-block texture memory

- useful when exploiting spatial locality

## **CUDA Global Memory**

- Global memory achieves high throughput through *coalescing*

- Works under certain global memory access patterns

- Half-warp coalescing: accesses by all threads in a half-warp (16 threads) are coalesced

- threads must access 32, 64, or 128-bit data types

- data accessed must be properly word-aligned

- threads must access words of coalesced access in sequence

- Responsibility is placed upon CUDA programmer

- no coalescing → huge hit to memory throughput

- Can use CUDA Profiler to track amount of coalesced/non-coalesced accesses

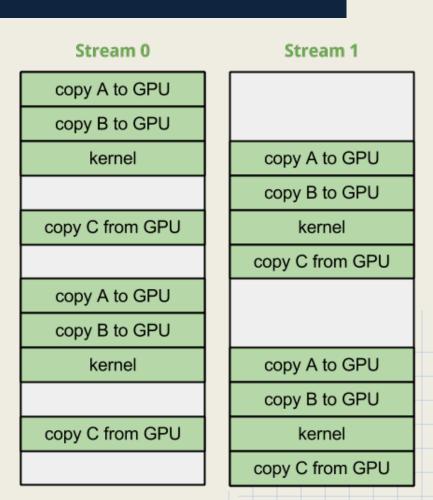

# **CUDA** Streaming

- Task parallelism can be achieved through *streaming*

- stream: queue of tasks to be performed on GPU

- asynchronous copies hide latency of memory movement

- requires page-locked ("pinned") memory

- ruins virtual memory abstraction

lime

- steps on other processes' toes

- later versions support two streaming memory accesses

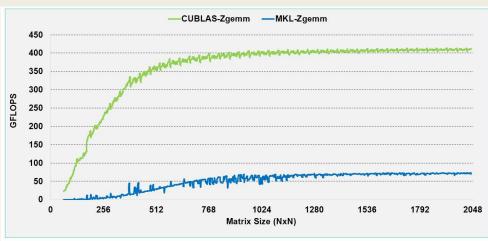

# **CUDA** Applications

- CUBLAS: CUDA Basic Linear Algebra Subprograms

- Adapted from well-known FORTRAN BLAS package

- Three tiers of routines

- level 1: vector scaling, inner product

- level 2: matrix-vector products, matrix triangularization

- level 3: matrix-matrix multiplication

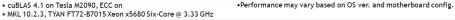

- CUFFT: CUDA Fast Fourier Transforms

- 1D, 2D, and 3D transforms for real-valued and complex data

# NVIDIA Kepler GK 110 Architecture

#### • Dynamic Parallelism

- Without ANY CPU help, GPU can

- dynamically create new worker threads

- synchronize among thread results

- schedule worker threads

- Advantages:

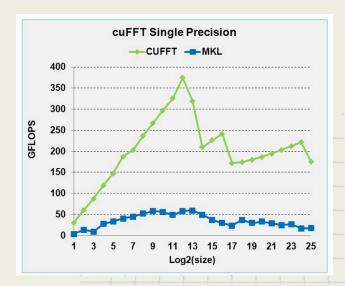

- GPU can adapt to varying amounts and types of parallel workloads (choose optimal # threads and program parameters)

- CPU can perform other tasks in the meanwhile

- avoids CPU-GPU data transfers

### Dynamic Parallelism Example

#### Dynamic Parallelism Makes GPU Computing Easier & Broadens Reach

### Kepler: New Features Cont'd

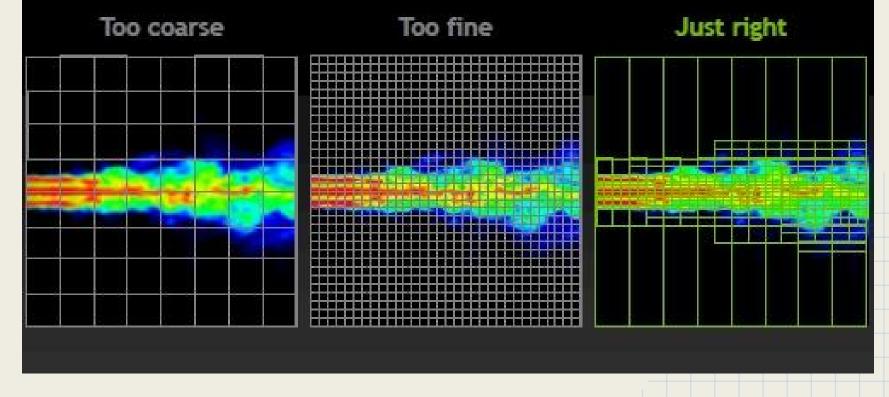

#### • Hyper-Q

- Multiple streams (cores/threads/processes) can run work on a single GPU at the same time, using separate HW work queues

- Prevents streams from blocking each other due to false dependencies

- GPUDirect

- Allows multiple GPUs on the same machine/network to share data directly without using the CPU or main memory

- RDMA feature allows third-party devices such as SSDs to directly access GPU memory

- Greatly improves message passing performance

# Hyper-Q Example

Each stream receives its own work queue

Left: only (C,P) and (R,X) can run concurrently Right: all 3 streams can run concurrently

# Kepler Full Chip Diagram

15 SMX Units (Streaming Multiprocessors)

#### +

### 6 64-bit memory controllers

# SMX Unit

- 192 single-precision CUDA cores

- 64 double-precision CUDA cores

- 32 special function units (SFU)

- 32 load/store units (LD/ST)

- 4 warp schedulers,

2 instruction

dispatch units each

- 64KB memory

- 48KB read-only data cache

| SMX                                                            |        |       |                   |      |      |      |                   |           |        |        |                   |        |                                                                                                                |      |      |      |          |       |        |

|----------------------------------------------------------------|--------|-------|-------------------|------|------|------|-------------------|-----------|--------|--------|-------------------|--------|----------------------------------------------------------------------------------------------------------------|------|------|------|----------|-------|--------|

| Instruction Cache Warp Scheduler Warp Scheduler Warp Scheduler |        |       |                   |      |      |      |                   |           |        |        |                   |        |                                                                                                                |      |      |      |          |       |        |

| Dispatch Dispatch                                              |        |       | Dispatch Dispatch |      |      |      | Dispatch Dispatch |           |        |        | Dispatch Dispatch |        |                                                                                                                |      |      |      |          |       |        |

|                                                                | -      |       | +                 |      |      | *    |                   |           | 102.0  |        | +                 |        | The state of the                                                                                               |      |      | +    |          |       | Const. |

|                                                                |        |       |                   |      |      |      | Regi              | ster i    | -ne (i | 55,53  | 6 X 3             | 2-Dit) |                                                                                                                |      |      |      | •        |       |        |

| 1110                                                           |        | Core  | DP-Line           | Core | Gore | Core | DP Unit           | 10.97     | SFU    | Core   | Core              |        | the second s | Gore |      |      | DP Linit | LOST  | SFU    |

| Core Co                                                        | an (   | Com   | DP Unit           | Cale | Germ | Com  | OP Unit           | LDIST     | SFU    | Core   | Gore              | Core   | OP Unit                                                                                                        | Core | Com  | Care | TIP Unit | LDIST | sru    |

| Core Co                                                        | an l   | Core  | DP Unit           | Com  | Core | Com  | DP Line           | LOST      | SFU    | Core   | Core              | Core   | OP Unit                                                                                                        | Care | Care | Core | DP Um    | LOST  | SFU    |

|                                                                | om 1   | Com   | DP Unit           | Cate | Core | Core | OP LINE           | LOST      | SFU    | Core   | Core              | Core   | OP Unit                                                                                                        | Care | Core | Com  | CIP Unit | LOIST | SFU    |

|                                                                | -      |       |                   |      |      |      |                   | TROUTS    |        |        |                   |        | -                                                                                                              |      |      |      |          |       |        |

|                                                                |        | Care  | DP Unit           | Core |      | Core | SIP Unit          | LDST      | SFU    |        | Core              |        | -                                                                                                              | Core |      | Com  | DP Unit  | LOIST | SFU    |

| Core Co                                                        | ansi ( | Com   | DP Unit           | Core | Core | Core | DP UNE            | LDIST     | SFU    | Core   | Core              | Core   | DP Unit.                                                                                                       | Gore | Core | Cont | DP-Unit  | LOIST | SFU    |

| Core Co                                                        | in (   | Core  | DP Unit           | Core | Com  | Corn | OP Link           | LDIST     | SFU    | Com    | Core              | Core   | OP Unit                                                                                                        | Core | Core | Cone | DP Unit  | LOIST | SFU    |

| Core Co                                                        | ana (  | Core  | DP Unit           | Core | Core | Core | OP Line           | 10/81     | SFU    | Sore   | Core              | Cote   | OP Unit                                                                                                        | Gare | Core | Com  | OP-Unit  | LINET | SFU    |

| Core Co                                                        | one (  | Care  | DP UNIT           | Core | Core | Core | DP Unit           | 10.87     | SFU    | Core   | Core              | Core   | DP Unit                                                                                                        | Care | Core | Core | OP Unit  | LOUBT | SFU    |

| Core Co                                                        | ore (  | Core  | OP UNIX           | Core | Core | Core | OP Unit           | 10191     | SFU    | Coru   | Gore              | Core   | DP-Unit                                                                                                        | Core | Core | Core | OP Unit  | LOIST | SFU    |

| Core: Co                                                       | one (  | Core  | DP Unit           | Core | Core | Core | OP LINE           | 10:81     | SFU    | Som    | Gore              | Con    | OP Unit                                                                                                        | Core | Core | Core | OP Unit  | LOUBT | SFU    |

| Core Co                                                        | on 1   | Core  | DP UNT            | Core | Core | Core | OP Unit           | LOST      | SFU    | Born   | Core              | Core   | DP Unit                                                                                                        | Core | Care | Com  | DP LINE  | LOTT  | SFU    |

| Core Co                                                        | one i  | Core  | DP Unit           | Com  | Core | Core | OP Line           | LDIST     | SFU    | Core   | Core              | Core   | OP-Unit                                                                                                        | Care | Core | Com  | DP UHI   | LDIST | SFU    |

|                                                                |        | Core  | DP Lines          |      | Core | Core | OP Line           | 1081      | SFU    |        | Core              |        | DP UNIT                                                                                                        | Core |      | Core | OP Linit | LOVET | SFU    |

|                                                                | -      |       | _                 |      |      |      | _                 |           |        |        |                   |        | _                                                                                                              |      |      |      | -        | 1000  |        |

|                                                                | -      | Corre | DP Unit           |      |      | -    | OP Unit           | -         | sru.   |        |                   | Core   | _                                                                                                              | Core |      | -    | DP Umi   | LOVET | SFU    |

| Core Co                                                        | one (  | Com   | DP Unit           | Core | Core | Core | OP Usit           | a Streets | SFU    |        | 1000              | Core   | DP Unit                                                                                                        | Core | Core | Core | OP.Unit  | LOST  | SFU    |

|                                                                |        |       |                   |      |      |      | 64 KB             |           |        | en Nel |                   | Cac    | he                                                                                                             |      |      |      |          |       |        |

|                                                                |        |       |                   |      |      |      |                   | B Re      |        |        |                   |        |                                                                                                                |      |      |      |          |       |        |

| Tex Tex                                                        |        |       | Tex               |      |      | Tex  |                   | Tex       |        | Tex    |                   | Tex    |                                                                                                                |      | Tex  |      |          |       |        |

| Tex                                                            |        |       | Tex               |      | Tex  |      |                   | Tex       |        |        | Tex               |        | Төх                                                                                                            |      | Tex  |      |          | Tex   |        |

## **SMX Core Architecture**

- Quad Warp Scheduler

- 32 threads / warp and 2 instruction dispatch units / warp scheduler

- 4 warps can be executed concurrently; 2 instructions at a time

- 255 registers per thread

- Shuffle Instruction

- Allows any thread in a warp to read registers of any other thread in the same warp in a single step, instead of going through shared memory with separate LD/ST insts.

- 64KB memory split between shared memory & L1 cache

- 48KB read-only cache for constant data

- can be managed automatically by the compiler, or manually by the programmer

### AMD GCN Architecture

#### • Tighter CPU-GPU integration

- Virtual Memory: supports 4KB pages

- could allow CPU & GPU to share single address space in the future

- GCN includes I/O MMU, which maps GPU addresses to CPU addresses

- 64B cache lines

- Cache Coherency: data shared between cores through L2 cache, instead of having to synchronize by flushing to memory

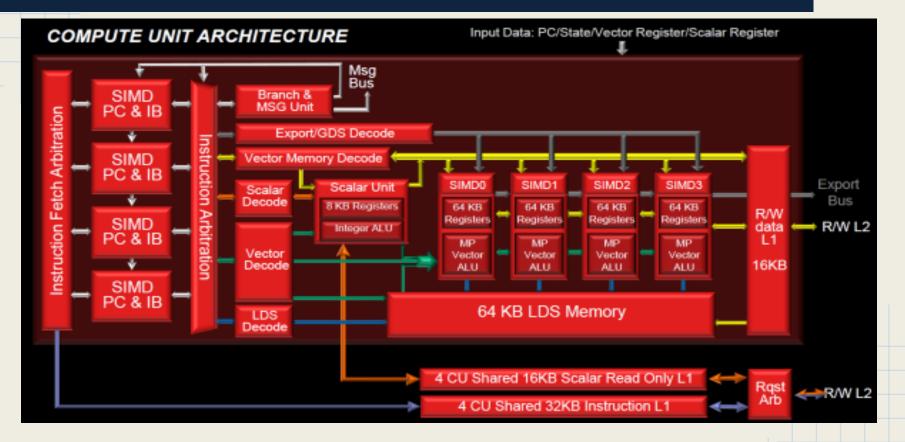

# **Compute Unit Architecture**

4 SIMD Units (10 wavefronts each), 16KB R/W L1-D cache, 32KB L1-I cache per 4 CU's, 64KB Local Data Share (LDS)

# Compute Units (CU's)

- Basic computational building block

- 4 SIMD units; each has PC and IB for 10 wavefronts

- Each cycle, single SIMD picked via RR to issue up to 5 instructions

- instructions must be of different types, from different wavefronts

- SIMD executes in parallel across multiple wavefronts, instead of in parallel within a single wavefront

- 16KB R/W L1-D cache & 32KB L1-I cache per 4 CU's

LRU replacement

- Local Data Share (LDS): 64KB memory used for intrawork-group synchronization

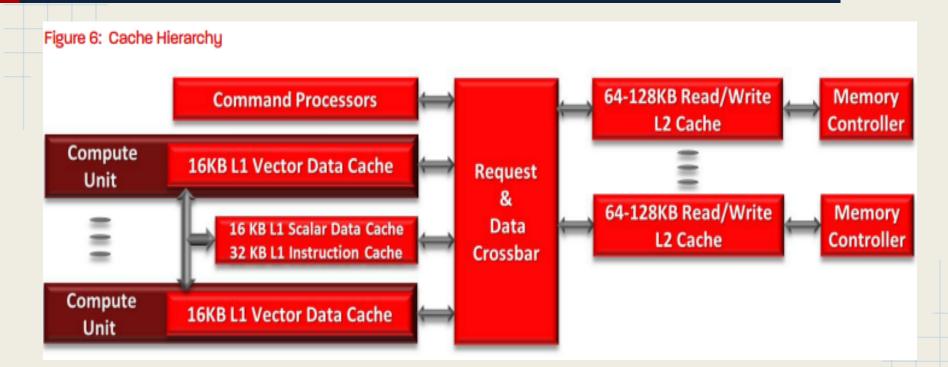

# GCN Cache Hierarchy

L1-D cache per CU, L1-I cache per 4 CU's, L2 cache partitioned and shared by all CU's

# Cache Hierarchy

- L1-D cache per CU; L1-I cache per 4 CU's

- write-through

- data written to L2 cache at end of wavefront instruction, or at a barrier

- work-group coherency

- L2 cache shared among all CU's and partitioned into one slice per memory channel

- write-back

- absorbs L1-D cache misses

- synchronizes among different wavefronts --> global coherency

- All caches use LRU replacement policy

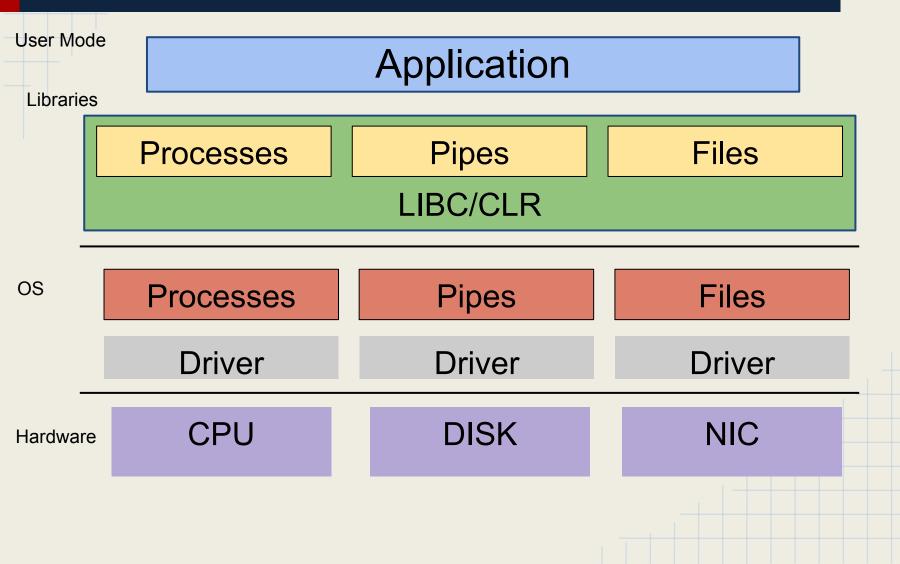

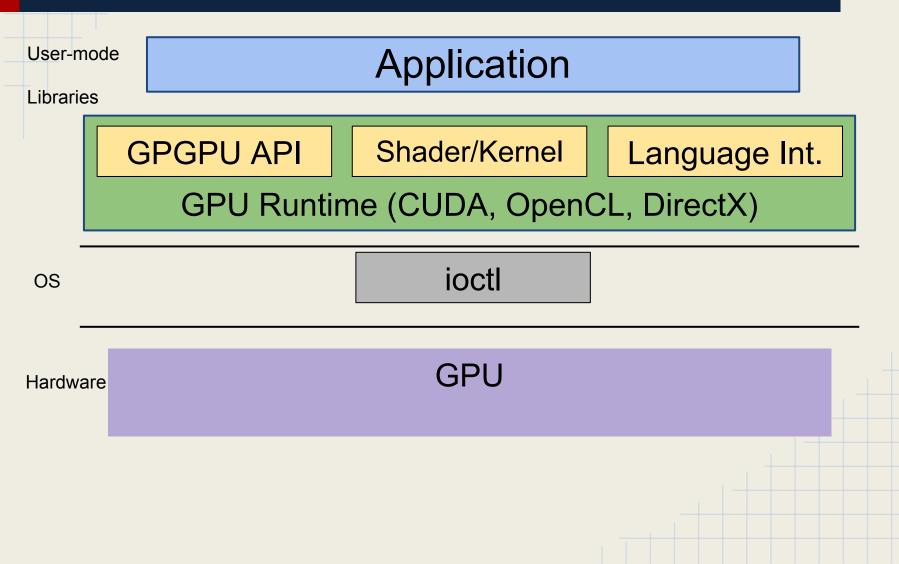

## **GPGPU** Challenges

- GPGPUs are more than just I/O devices

- First class computational devices

- Fairness and isolation guarantees

- Preempting GPUs is not easy

- Large number of parallel operations

- Limited interface

- Drivers are black boxes

- Existing OS/kernel interfaces use ioctl

- Memory can be disjoint

### **Additional Motivation**

- Data movement tied to algorithms

- High-level languages (CUDA) are hard to use.

- New applications that require OS support

encrypted file systems

- gesture detection

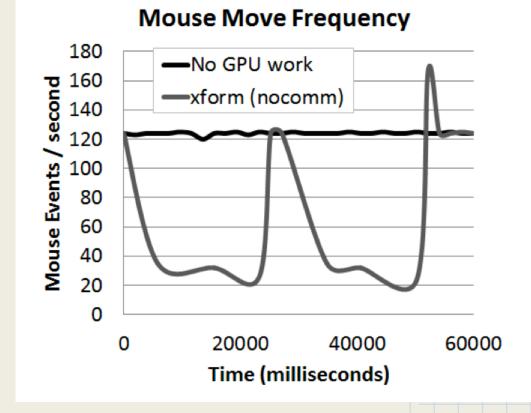

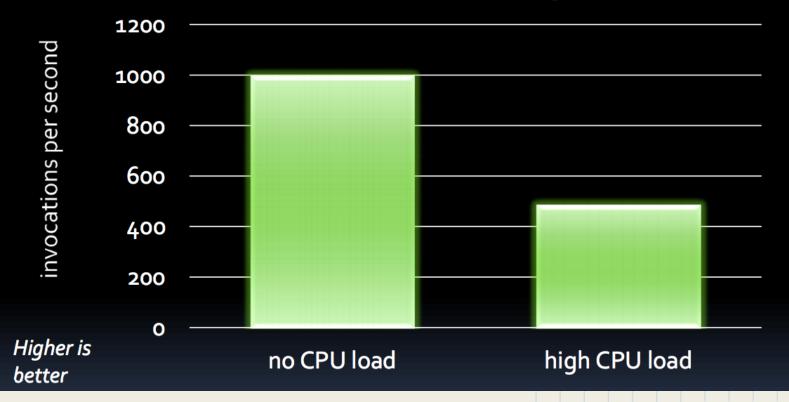

## Scheduling Bottlenecks

- GPU accelerated tasks can impair seemingly unrelated tasks

- GPU work causes system pauses

- CPU work interferes with GPU throughput

#### Scheduling Bottlenecks (cont.)

#### No OS support $\rightarrow$ No isolation

#### **GPU benchmark throughput**

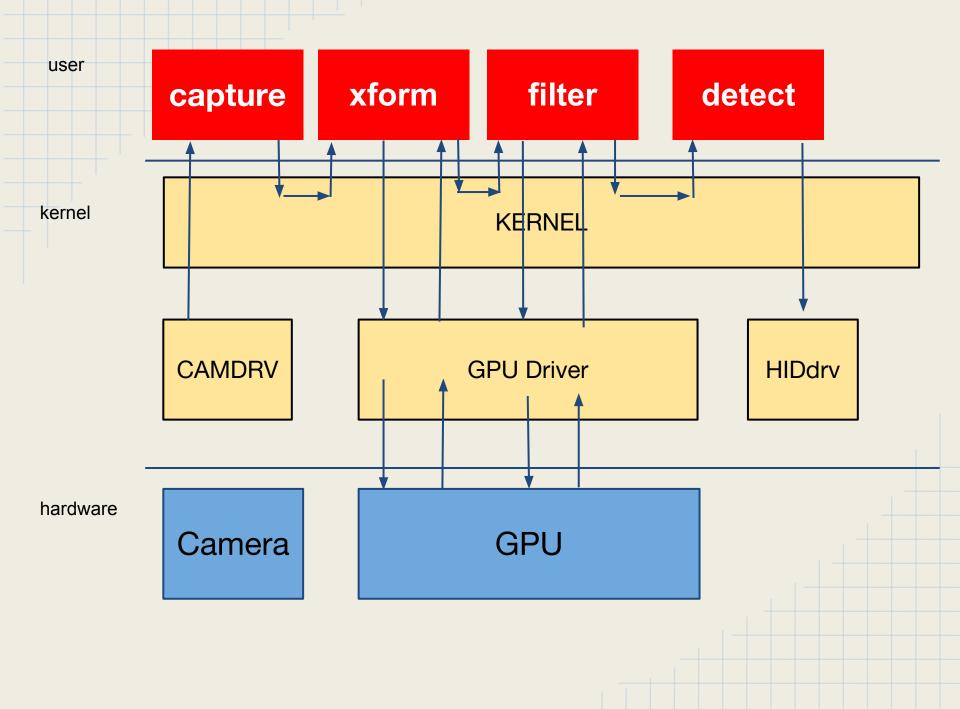

# OS Support

# GPGPU Support

#### PTask

- 1. GPUs under a single resource manager for fairness and isolation guarantees

- 2. Simplify development for accelerators/GPGPUs by introducing a programming model that manages devices, performs I/O, and deals with disjoint memory spaces.

- 3. Create an environment that allows modular and fast code

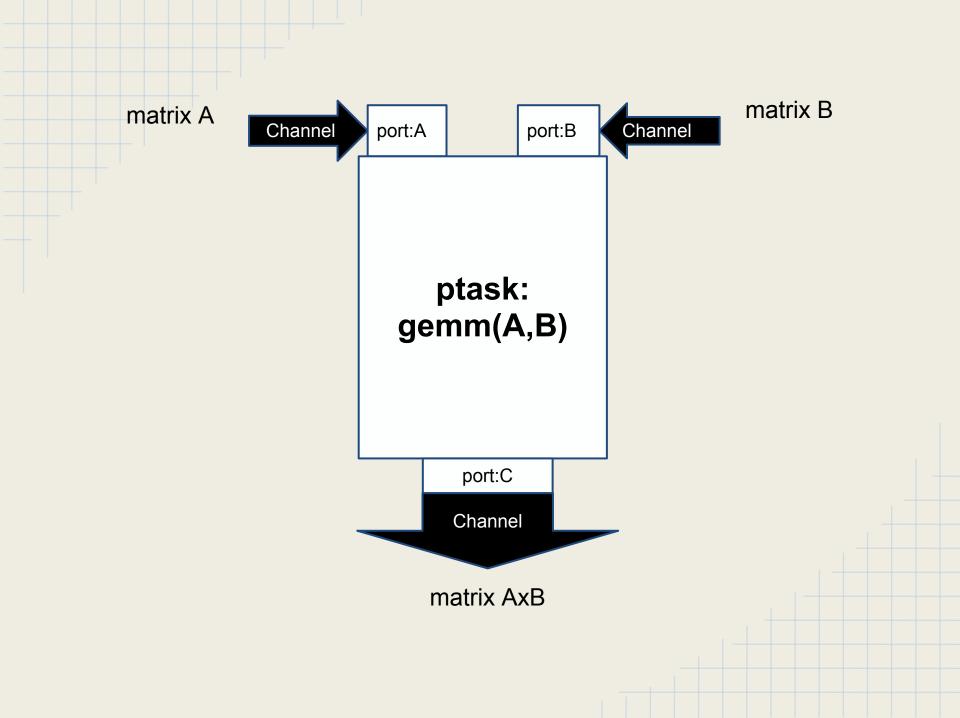

## **Dataflow Programming**

Modularity and efficiency

### Matrix Multiplication

```

matrix gemm(A, B) {

matrix AxB = new matrix();

copyToDevice(A);

copyToDevice(B);

invokeGPU(gemm_kernel, A, B, AxB);

copyFromDevice(AxB);

return AxB;

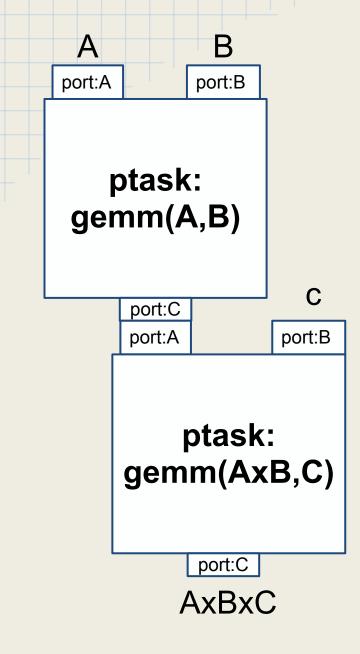

} matrix AxBxC(A,B,C) {

```

```

return gemm(gemm(A, B), C);

```

# Matrix Multiplication (Cont.)

matrix AxBxC(A,B,C) { Not modular! matrix AxB = new matrix(); matrix AxBxC = new matrix(); copyToDevice(A); copyToDevice(B); copyToDevice(C); invokeGPU(gemm kernel, A, B, AxB); invokeGPU(gemm kernel, AxB, C, AxBxC); copyFromDevice(AxBxC); return AxBxC;

### **Dataflow Programming**

- Allows modularity and efficiency

- Graph structured computation model

- Units of computation are vertices

- Vertices have data sources and data sinks (ports)

- Channels connect ports

- Dataflow managed by the OS

- Dataflow is managed by the OS.

- PTasks (vertices) are computation units

- Ports connected by channels (edges)

Both modular and efficient

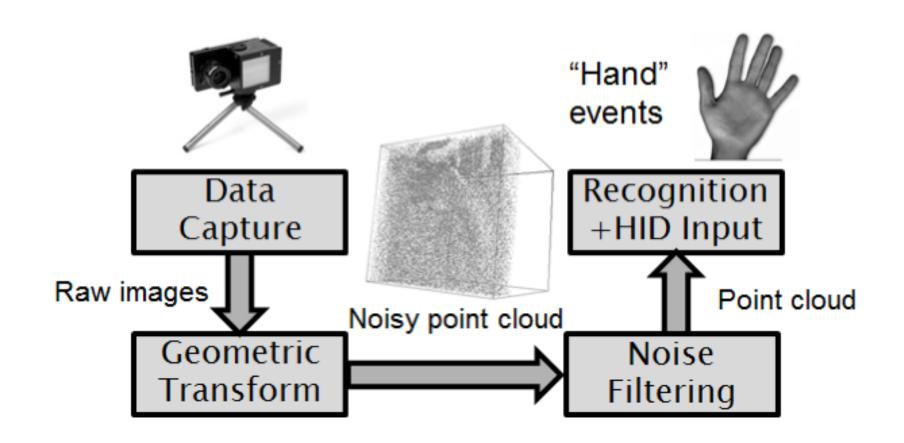

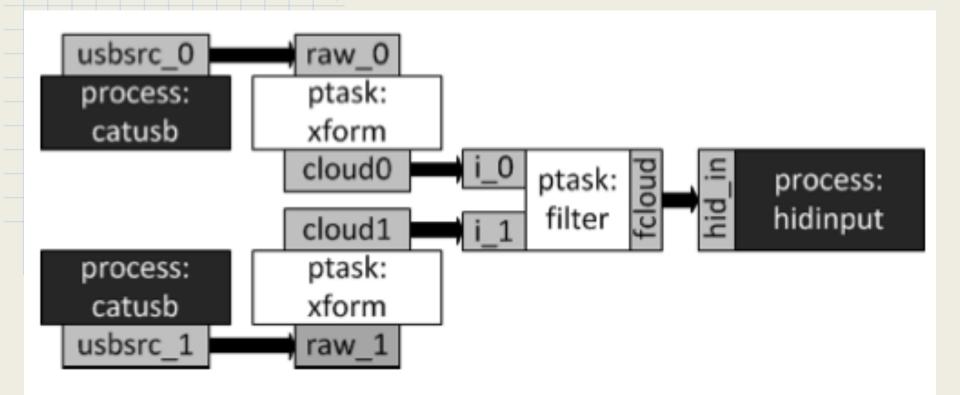

# Case Study: Gesture Recognition

- Computationally intensive

Ideal for GPGPU acceleration

- Latency requirements

- Largely data parallel

- Multiple user-kernel memory copies

- Follows dataflow paradigm

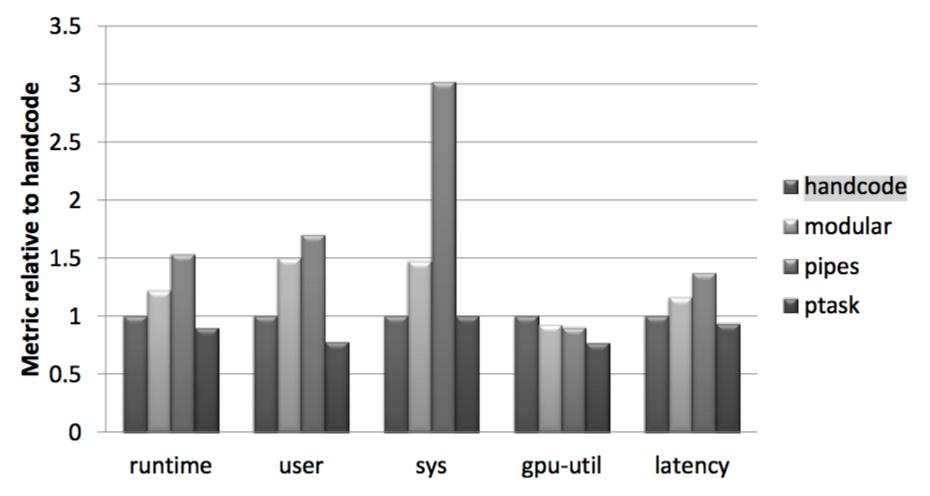

> capture | xform | filter | detect &

|            | impl       |               | fps  | tput (MB/s) | lat (ms) | user | sys  | gpu  | gmem | thrds | ws-delta   |

|------------|------------|---------------|------|-------------|----------|------|------|------|------|-------|------------|

| Core2-Quad | host-based | real-time     | 20.2 | 35.8        | 36.6     | 78.1 | 3.9  | -    | _    | 1     | -          |

| GTX580     | handcode   | real-time     | 30   | 53.8        | 10.5     | 4.0  | 5.3  | 21.0 | 138  | 1     | -          |

|            |            | unconstrained | 138  | 248.2       | -        | 2.4  | 6.4  | 41.8 | 138  | 1     | _          |

|            | modular    | real-time     | 30   | 53.8        | 12.2     | 6.0  | 8.1  | 19.4 | 72   | 1     | 0.8 (1%)   |

|            |            | unconstrained | 113  | 202.3       | -        | 5.7  | 8.6  | 55.7 | 72   | 1     | 0.9 (1%)   |

|            | pipes      | real-time     | 30   | 53.8        | 14.4     | 6.8  | 16.6 | 18.9 | 72   | 3     | 45.3 (58%) |

|            |            | unconstrained | 90   | 161.9       | -        | 12.4 | 24.6 | 55.4 | 76   | 3     | 46.3 (59%) |

|            | ptask      | real-time     | 30   | 53.8        | 9.8      | 3.1  | 5.5  | 16.1 | 71   | 7     | 0.7 (1%)   |

|            |            | unconstrained | 154  | 275.3       | -        | 4.9  | 8.8  | 65.7 | 79   | 7     | 1.4 (2%)   |

#### • Handcode

- remove unnecessary data copying

- Modular

- similar to Handcode but condensed into one process

- Pipes

- > capture | xform | filter | detect &

- PTasks

- Uses the PTask API

#### **Gestural Interface Performance**

#### References

- <u>GPU Computing</u> J. D. Owens, M. Houston, D. Luebke, S. Green, J. E. Stone, and J. C. Phillips. May 2008

- <u>A Closer Look at GPUs</u> K. Fatahalian, M. Houston. October 2008.

- Managing Accelerators: the Operating System Perspective K. Shantonu.

- <u>CUDA C Programming Guide</u> Nvidia Corporation. October 2012.

- <u>CUDA by Example</u> J. Sanders and E. Kandrot. April 2011.

- <u>CUDA, Supercomputing for the Masses series</u> R. Farber. April 2008 -September 2010.

- NVIDIA Kepler GK110 Architecture. Nvidia Corporation. 2012.

- <u>AMD GCN Architecture</u>. AMD. June 2012.

- <u>PTask: Operating Systems Abstractions To Manage GPUs as Compute</u> <u>Devices</u>. C Rossbach, J. Currey, M. Silberstein, B. Ray, E. Witchel. Microsoft Research. October 2011.

### PTask API

sys\_open\_graph sys\_open\_port sys open ptask sys open channel sys\_open\_template sys push sys\_pull sys\_run\_graph sys terminate graph sys\_set\_ptask\_prio sys set geometry

Create/open graph Create/open port Create/open a ptask Create and bind a channel Create/open a template Write to a channel/port Read from a channel/port Run a graph Terminate graph Set ptask priority Set iteration space

# PTask Scheduling

- First-available

- Fifo

- Priority

- Data-aware