## Combinational & Sequential Circuits (2)

#### • Sequential:

- >Output depends on the *current* input values and the *previous* sequence of input values.

- >Are Cyclic:

✓ Output of a gate feeds its input at some future time.

#### ≻Memory:

- ✓ Remember results of previous operations ✓ Use them as inputs.

- ≻Example of use:

✓Build registers and memory units.

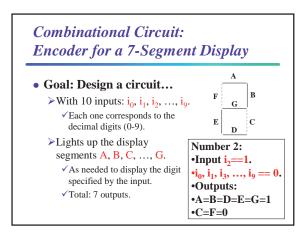

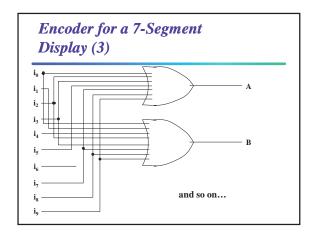

### Encoder for a 7-Segment Display (2)

- Boolean expression for the outputs:  $A = i_0 + i_2 + i_3 + i_5 + i_7 + i_8 + i_9$   $B = i_0 + i_1 + i_2 + i_3 + i_4 + i_7 + i_8 + i_9$

- $\begin{array}{rcl} C &=& i_0 \;+\; i_1 \;+\; i_3 \;+\; i_4 \;+\; i_5 \;+\; i_6 \;+\; i_7 \;+\; i_8 \;+\; i_9 \\ D &=& i_0 \;+\; i_2 \;+\; i_3 \;+\; i_5 \;+\; i_6 \;+\; i_8 \\ E &=& i_0 \;+\; i_2 \;+\; i_6 \;+\; i_8 \end{array}$

- $\begin{array}{rcl} F &=& i_0 \;+\; i_4 \;+\; i_5 \;+\; i_6 \;+\; i_8 \;+\; i_9 \\ G &=& i_2 \;+\; i_3 \;+\; i_4 \;+\; i_5 \;+\; i_6 \;+\; i_8 \;+\; i_9 \end{array}$

- Build the circuit with 7 OR gates:

- > One for each segment of the display

#### Constraints on Circuit Design

- Numerous constraints impact: >The speed and cost of a circuit.

- Speed:

- > Every gate in a circuit introduces a small delay.

- Circuit delay depends on the number of gates between inputs and outputs.

### Constraints on Circuit Design

#### • Size limitations:

- ➤More gates lead to larger circuits.

- >Large circuits are more expensive

- ✓ Higher failure rate.

- And slower.

- $\checkmark$  Signals must propagate from one end to the other.

- Fan-in and Fan-out:

- >Number of inputs and outputs of a gate.

- Large fan-in makes a gate slower.

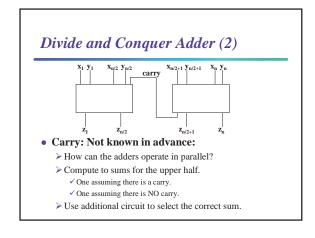

## Divide and Conquer Adder

- Already seen Ripple-Carry adder

- Need:

≻Adder with a smaller delay for larger words.

- Solution:

- ≻Use a divide and conquer strategy.

- ≻Use two N/2-bit adders and combine results.

- ≻Left and right halves added in parallel.

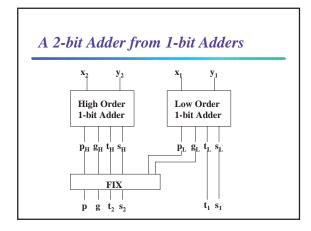

#### Design of an N-adder

- Assume two N-bit operands: x<sub>1</sub>...x<sub>N</sub> & y<sub>1</sub>...y<sub>N</sub>.

- Design N-adder that computes:

- Sum *without* carry-in:  $s_1...s_{N^*}$

- Sum *with* carry-in: t<sub>1</sub>...t<sub>N</sub>.

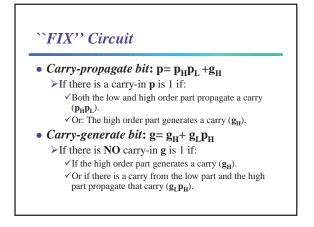

- > The *carry-propagate* bit, p:

- ✓ It is 1 if there is a carry-out assuming there is carry-in.

> The *carry-generate* bit, g:

- ✓ It is 1 if there is a carry-out even if there is NO carry-in.

- ✓ **NOTE:** if **g** is one then **p** will be one too (*g implies p*).

- First, build an 1-bit adder.

#### A 1-bit Adder

# Boolean Functions

| Х | У | S | t | p | g |  |

|---|---|---|---|---|---|--|

| 0 | 0 | 0 | 1 | 0 | 0 |  |

| 0 | 1 | 1 | 0 | 1 | 0 |  |

| 1 | 0 | 1 | 0 | 1 | 0 |  |

| 1 | 1 | 0 | 1 | 1 | 1 |  |

#### Logical Expressions

| $s = \overline{xy} + x\overline{y}$ |

|-------------------------------------|

| $t = \overline{xy} + xy$            |

| p = x + y                           |

| g = xy                              |

# *``FIX'' Circuit (2)*

- High order sum, NO carry-in: > It is:  $s_2 = s_H \overline{g}_L + t_H g_L$

- ✓ s<sub>H</sub> if there is no carry from low order part (~g<sub>L</sub>). ✓ t<sub>H</sub> if there is carry from low order part (g<sub>I</sub>).

- High order sum, with carry-in:

- The former sum, with curry-in. The second second

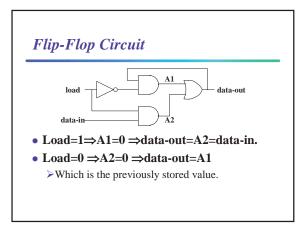

# Sequential Circuits for Memory Elements.

#### • Memory element:

A collection of gates capable of producing its last input as output.

- They are sequential circuits.

Their behavior depends on current and past inputs.

- Flip-flop:

- ≻A 1-bit memory element.

- ≻Typical flip-flop:

- ✓ Takes two inputs (load and data-in).

- ✓ Produces one output (data-out).

# Flip-Flops

- Load==0:

- $\succ$  The circuit produces the stored value as output.

- Load==1:

The circuit stores the value data-in and

Produces it as output.