### The Memory Hierarchy

- Topics

- Locality of reference

- Caching in the memory hierarchy

- Storage technologies and trends

2

### Locality

Principle of Locality:

- Temporal locality: Recently referenced items are likely to be referenced in the near future.

- Spatial locality: Items with nearby addresses tend to be referenced close together in time.

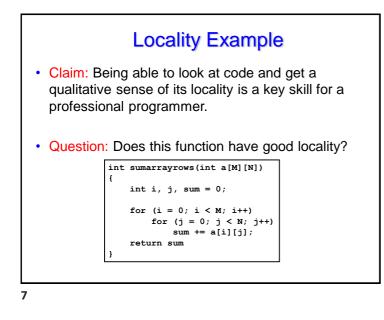

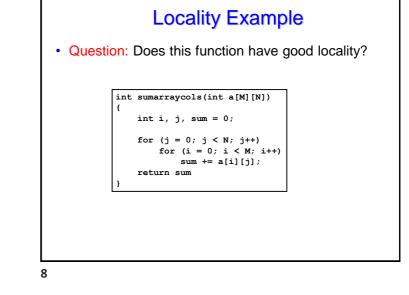

### Locality Example:

### • Data

sum = 0; for (i = 0; i < n; i++) sum += a[i]; return sum;

(stride-1 reference pattern): Spatial locality - Reference sum each iteration: Temporal locality

- Reference array elements in succession

- Instructions

- -Reference instructions in sequence: Spatial locality

- -Cycle through loop repeatedly: Temporal locality

# Loop Fusion

Can you improve the temporal locality of this program

```

for (i = 0; i < 100; i++)

A[i] = C[i];

for (i = 0; i < 100; i++)

B[i] = C[i]+1;

```

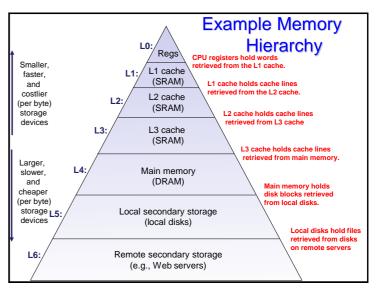

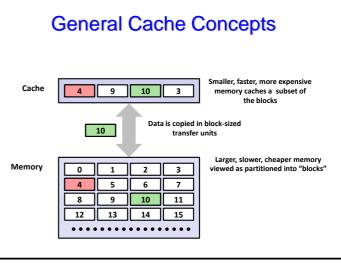

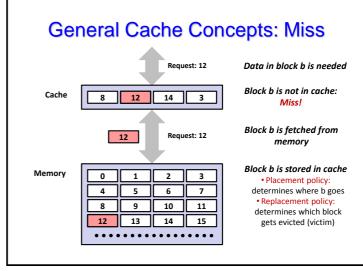

# General Caching Concepts: Types of Cache Misses

- Cold (compulsory) miss

- Cold misses occur because the cache is empty

- Conflict miss

- Most caches limit blocks at level k+1 to a small subset (sometimes a singleton) of the block positions at level k

- E.g. Block i at level k+1 must be placed in block (i mod 4) at level k

- Conflict misses occur when the level k cache is large enough, but multiple data objects all map to the same level k block

- + E.g. Referencing blocks 0, 8, 0, 8, 0, 8, ... would miss every time.

- Capacity miss

- Occurs when the set of active cache blocks (working set) is larger than the cache.

16

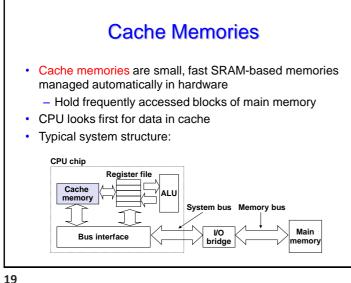

# Examples of Caching in the Mem. Hierarchy

| Cache Type              | What is Cached?      | Where is it Cached? | Latency (cycles) | Managed B           |

|-------------------------|----------------------|---------------------|------------------|---------------------|

|                         |                      |                     |                  |                     |

| TLB                     | Address translations | On-Chip TLB         | 0                | Hardware<br>MMU     |

| L1 cache                | 64-byte blocks       | On-Chip L1          | 4                | Hardware            |

| L2 cache                | 64-byte blocks       | On-Chip L2          | 10               | Hardware            |

| Virtual Memory          | 4-KB pages           | Main memory         | 100              | Hardware + O        |

| Buffer cache            | Parts of files       | Main memory         | 100              | OS                  |

| Disk cache              | Disk sectors         | Disk controller     | 100,000          | Disk firmwa         |

| Network buffer<br>cache | Parts of files       | Local disk          | 10,000,000       | NFS client          |

| Browser cache           | Web pages            | Local disk          | 10,000,000       | Web browse          |

| Web cache               | Web pages            | Remote server disks | 1,000,000,000    | Web proxy<br>server |

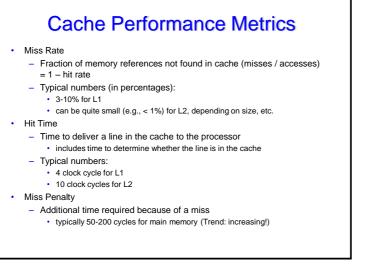

## Let's think about those numbers

- Huge difference between a hit and a miss

- Could be 100x, if just L1 and main memory

- Would you believe 99% hits is twice as good as 97%?

- Consider: cache hit time of 1 cvcle miss penalty of 100 cycles

- Average access time: \_ 97% hits: 1 cycle + 0.03 \* 100 cycles = 4 cycles 99% hits: 1 cycle + 0.01 \* 100 cycles = 2 cycles

- This is why "miss rate" is used instead of "hit rate"

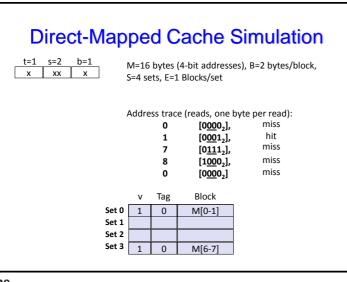

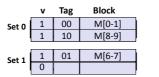

### 2-Way Set Associative Cache Simulation t=2 s=1 b=1 M=16 byte addresses, B=2 bytes/block, хх х х S=2 sets, E=2 blocks/set Address trace (reads, one byte per read): 0 [0000,], miss hit 1 [0001,], miss 7 [01<u>1</u>1<sub>2</sub>], miss 8 [1000,], hit 0 [00<u>0</u>0<sub>2</sub>] Tag Block v 00 1 M[0-1] Set 0 10 M[8-9] 1

Page 8

## **Breakout**

• Assume a direct-mapped cache of size 8 KByte 64-Byte line. A is located at 0x8000 and C is located at 0x9000. How many misses would you incur? Would this change with a 2-way set associative cache? Assume *i* is retained in a register and the arrays are not initially in the cache.

int A[100], C[100]; for (i = 0; i < 100; i++) A[i] = C[i];

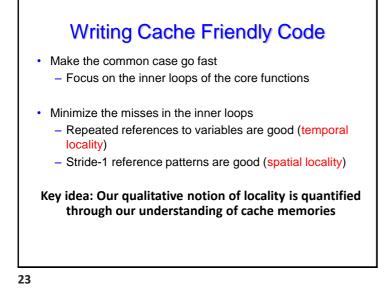

# Today Cache organization and operation Performance impact of caches The memory mountain Rearranging loops to improve spatial locality Using blocking to improve temporal locality

36