# r

# **Concurrent Programming is Hard!**

- The human mind tends to be sequential

- The notion of time is often misleading

- Thinking about all possible sequences of events in a computer system is at least error prone and frequently impossible

# Why employ concurrency?

- Resource sharing, information exchange, collaboration

- Tolerate delays such as slow I/O devices

- Provide good response times, e.g., with human interaction

- · Separate logical tasks

- Garbage collection

- Separate logical flow for each client in a concurrent server

2

4

- Reduce latency by deferring work

- Execute in parallel on hardware such as multicore machines

2

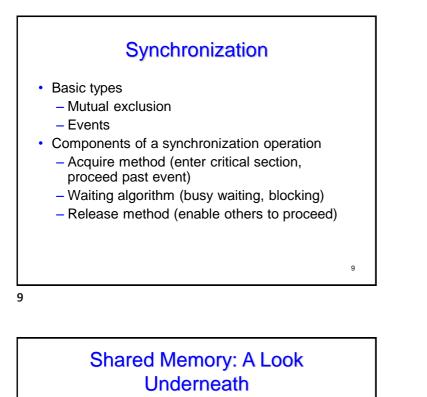

# What do we need?

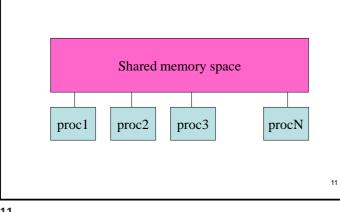

- Communication

- Messages versus shared memory

- Coordinate

- Synchronization

- Mutual exclusion

- Events

1

4

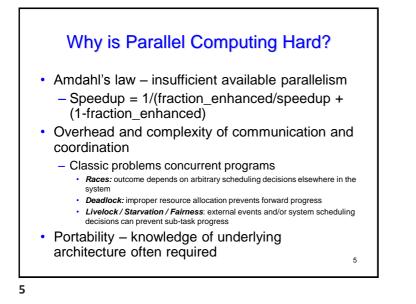

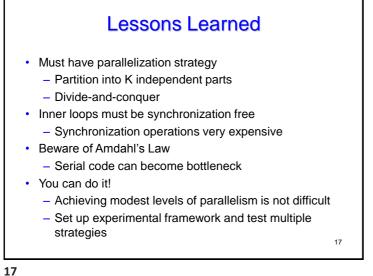

### Steps in the Parallelization Process

- Decomposition into tasks

- Assignment to processes

- Orchestration communication of data, synchronization among processes

6

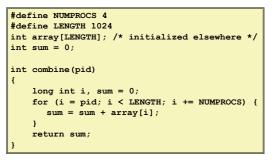

One Strategy to Sum Vector Elements in Parallel (pseudo-code)

Question: Assuming a direct-mapped cache size of 4 Kbytes and line size of 16 bytes, how many misses will each process incur on "array" assuming they are running in parallel on separate processors/cores? 7

# Types of Dependences

- Flow (or True) dependence RAW

- Anti-dependence WAR

- Output dependence WAW

7

8

Page 3

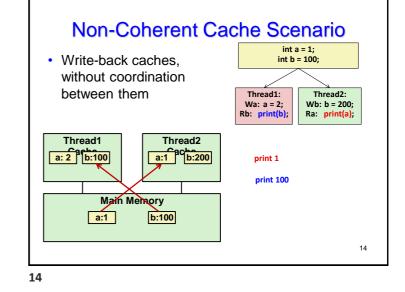

· Tag each cache block with state

Exclusive Writeable copy

a:1

Cannot use value

Thread2

Cache

E b:200

b:100

Readable copy

Main Memory

Invalid

Shared

Thread1

E a: 2 he

int a = 1:

Thread1:

Wa: a = 2;

Rb: print(b);

int b = 100;

Thread2:

Wb: b = 200;

Ra: print(a);

15

**Snoopy Caches** int a = 1; int b = 100; Tag each cache block with state • Invalid Cannot use value Thread1: Thread2: Shared Readable copy Wa: a = 2: Wb: b = 200: Exclusive Writeable copy Rb: print(b): Ra: print(a): Thread1 Thread2 S a:2 he S a: 2 he print 2 S b:200 S 6:200 print 200 Main Memory When cache sees request for one of its E-tagged blocks a:1 b:100 Supply value from cache Set tag to S 16 16

Topics covered:

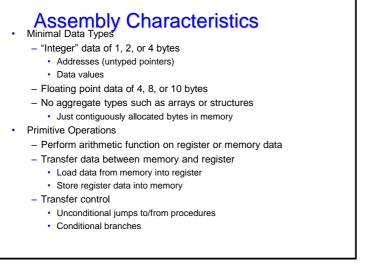

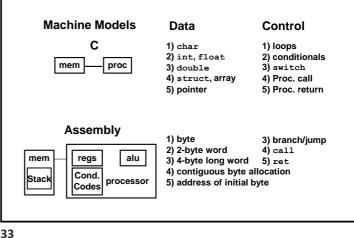

- · Data representation and computer arithmetic

- Assembly-level programs and instruction-set architectures

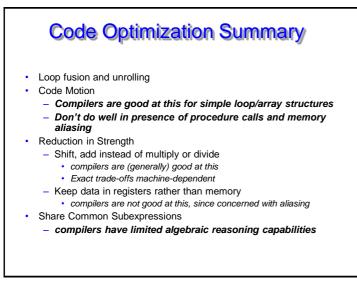

- · Processor architectures

- · Memory and storage hierarchies

- · Performance optimization

- · Exceptional control flow

- · Processes and virtual memory

- I/O interface, storage technologies, networking

- Concurrency

29

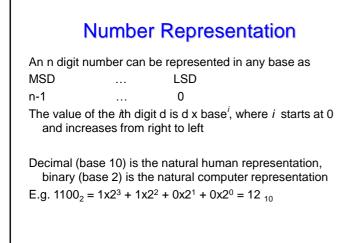

# **Data Representation**

- Memory: a large single-dimensional, conventionally byte-addressable, untyped array

- · Byte ordering big versus little endian

- Possible common interpretations

- Instruction

- Integer

31

- Floating point

- character

30

# Summary: Abstract Machines

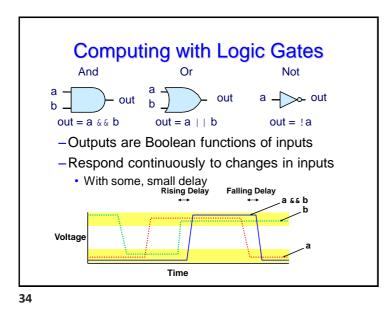

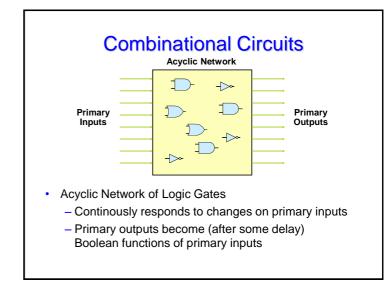

# Sequential Logic: Memory and Control

- · Sequential:

- Output depends on the *current* input values and the *previous* sequence of input values.

- Are Cyclic:

- Output of a gate feeds its input at some future time.

- Memory:

- Remember results of previous operations

- · Use them as inputs.

- Example of use:

- Build registers and memory units.

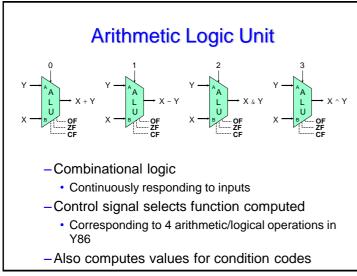

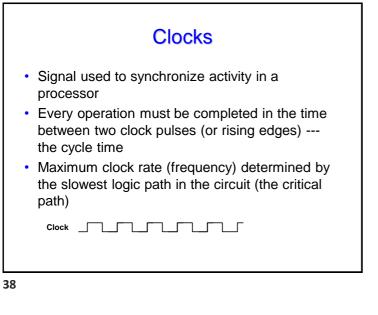

# **Processor Summary**

- Design Technique

- Create uniform framework for all instructions

- · Want to share hardware among instructions

- Connect standard logic blocks with bits of control logic

- Operation

- State held in memories and clocked registers

- Computation done by combinational logic

- Clocking of registers/memories sufficient to control overall behavior

- Enhancing Performance

- Pipelining increases throughput and improves resource utilization

- Must make sure maintains ISA behavior

39

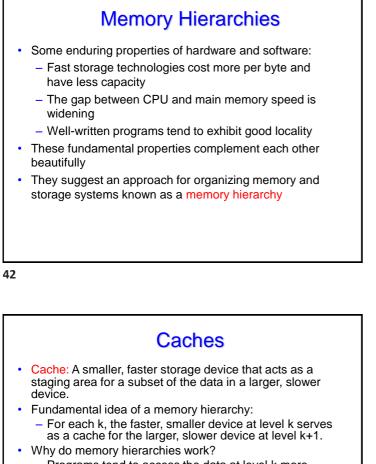

# Locality

- · Principle of Locality:

- Programs tend to reuse data and instructions near those they have used recently, or that were recently referenced themselves.

- Temporal locality: Recently referenced items are likely to be referenced in the near future.

- Spatial locality: Items with nearby addresses tend to be referenced close together in time.

#### Locality Example:

#### • Data

sum = 0; for (i = 0; i < n; i++) sum += a[i]; return sum;

(stride-1 reference pattern): Spatial locality - Reference sum each iteration: Temporal locality

- Reference array elements in succession

- Instructions

- Reference instructions in sequence: Spatial locality

- -Cycle through loop repeatedly: Temporal locality

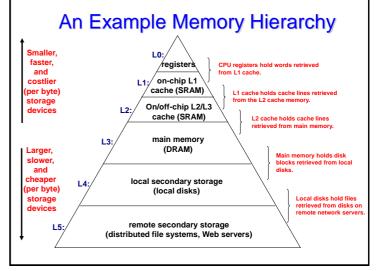

- Programs tend to access the data at level k more often than they access the data at level k+1.

- Thus, the storage at level k+1 can be slower, and thus larger and cheaper per bit.

- Net effect: A large pool of memory that costs as much as the cheap storage near the bottom, but that serves data to programs at the rate of the fast storage near the top.

# **Cache Organization**

- Location/placement how do you locate a block/where is a block placed

- · Replacement which block do you replace

- Least recently used (LRU)

- FIFO

- Random

- Write policy what happens on a write

- Write back

- Write through no write allocate

- Write through write allocate

# Problem 1

- Consider a computer with a 12-bit address space (i.e., each memory address is 12-bit long) and a byteaddressable memory. It has a data cache capable of holding eight cache blocks. Each cache block is 4 bytes (excluding any overhead).

- How many tag bits are needed

- What is the content of the cache for the following access pattern that repeats 4 times (a loop)

- 0x200, 0x204, 0x208, 0x20C, 0x2F4, 0x2F0, 0x200, 0x204, 0x218, 0x21C, 0x24C, 0x2F4

46

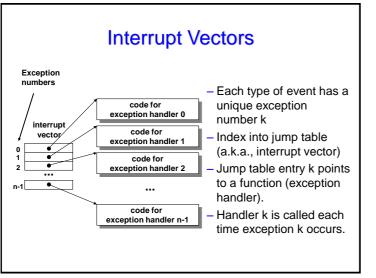

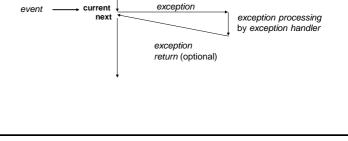

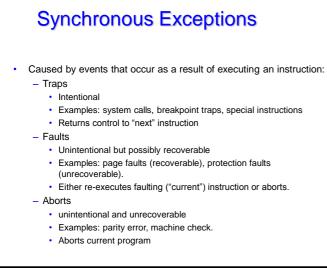

# An exception is a transfer of control to the OS in response to some event (i.e., change in processor state) User Process os

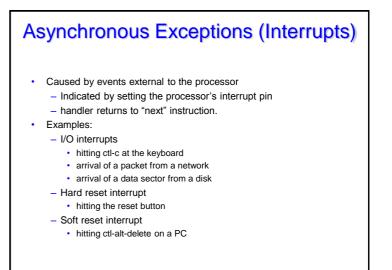

# **Exceptional Control Flow**

- Mechanisms for exceptional control flow exists at all levels of a computer system

- Low level Mechanism

- exceptions

- change in control flow in response to a system event (i.e., change in system state)

- Combination of hardware and OS software

- Higher Level Mechanisms

- Process context switch

- Signals

- Nonlocal jumps (setjmp/longjmp)

- Implemented by either:

- · OS software (context switch and signals)

- · C language runtime library: nonlocal jumps

51

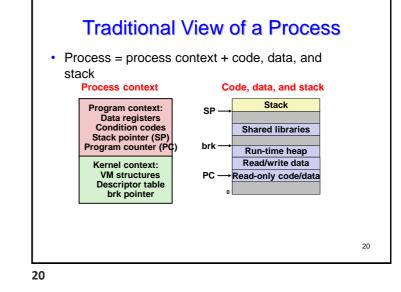

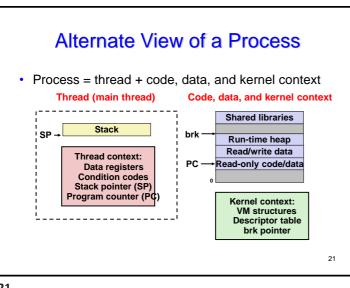

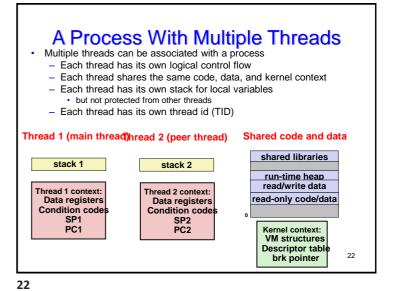

## Processes

- Def: A process is an instance of a running program.

- One of the most profound ideas in computer science.

- Not the same as "program" or "processor"

- Process provides each program with two key abstractions:

- Logical control flow

- Each program seems to have exclusive use of the CPU.

- Private address space

- · Each program seems to have exclusive use of main memory.

- · How are these Illusions maintained?

- Process executions interleaved (multitasking)

- Address spaces managed by virtual memory system

# Virtual Memory Programmer's View

- Large "flat" address space

- Large flat address space

- Can allocate large blocks of contiguous addresses

- Processor "owns" machine

- Has private address space

- · Unaffected by behavior of other processes

- System View

- User virtual address space created by mapping to set of pages

- Need not be contiguous

- · Allocated dynamically

- Enforce protection during address translation

- OS manages many processes simultaneously

- Continually switching among processes

- · Especially when one must wait for resource

- E.g., disk I/O to handle page fault

| Physical Page   |                                                                                         |

|-----------------|-----------------------------------------------------------------------------------------|

| Contents        |                                                                                         |

| Empty           |                                                                                         |

| Virtual Page 13 |                                                                                         |

| Virtual Page 5  |                                                                                         |

| Virtual Page 2  |                                                                                         |

| Empty           |                                                                                         |

| Virtual Page 0  |                                                                                         |

| Empty           |                                                                                         |

| Page Table      |                                                                                         |

|                 | Virtual Page 13<br>Virtual Page 5<br>Virtual Page 2<br>Empty<br>Virtual Page 0<br>Empty |

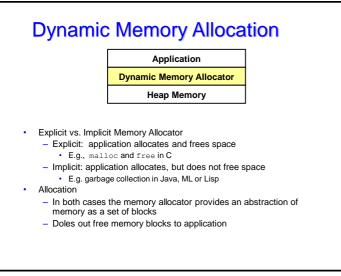

# Harsh Reality: Memory Matters

- · Memory is not unbounded

- It must be allocated and managed

- Many applications are memory dominated

- · Especially those based on complex, graph algorithms

- Memory referencing bugs especially pernicious

- Effects are distant in both time and space

- · Memory performance is not uniform

- Cache and virtual memory effects can greatly affect program performance

- Adapting program to characteristics of memory system can lead to major speed improvements

55

# Memory-Related Bugs

- Dereferencing bad pointers

- Reading uninitialized memory

- Overwriting memory

- · Referencing nonexistent variables

- · Freeing blocks multiple times

- Referencing freed blocks

- · Failing to free blocks

# Topics covered:

- Data representation and computer arithmetic

- Assembly-level programs and instruction-set architectures

- Processor architectures

- · Memory and storage hierarchies

- · Performance optimization

- Exceptional control flow

- · Processes and virtual memory

- I/O interface, storage technologies, networking

- Concurrency

58

58

59

**THANK YOU!**

Wishing you a restful, safe, and warm holiday

season, and a Happy New Year!