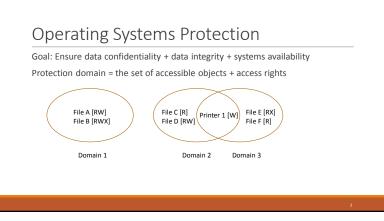

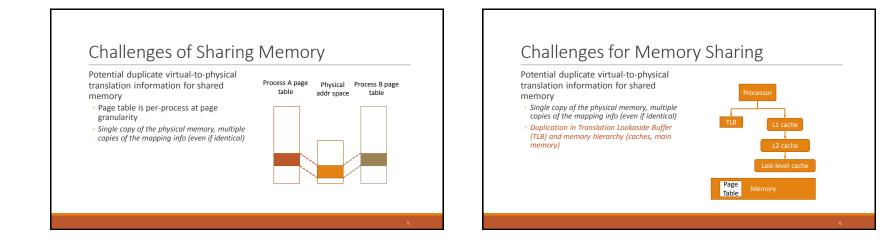

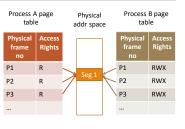

### Challenges for Changing Access Permissions of Memory Regions

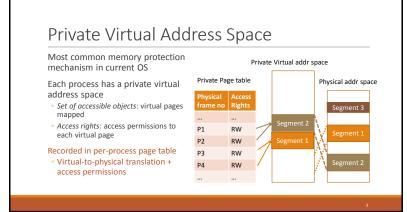

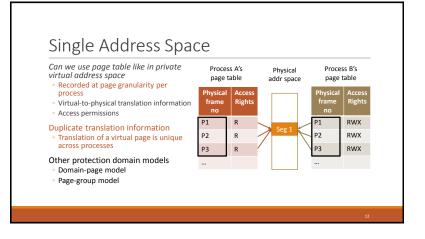

Changing access permissions of Process A page an entire memory region is table expensive • E.g., disabling writes to a memory Physical Access region across processes Rights frame no Page table is at page granularity P1 R on per-process basis P2 R Р3 R Required to traverse each page table entry of each virtual address space

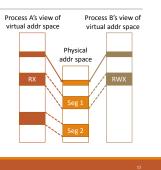

# Single Address Space

One single virtual address space shared across processes

# One virtual address is mapped to a *unique* physical address

Simplifies memory sharing compared to private virtual address space

Proposed in the 90s

• Emerging 64-bit address space

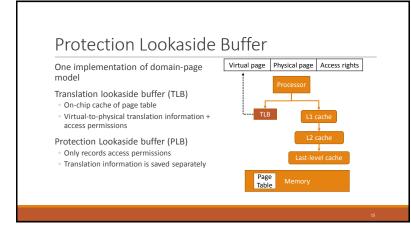

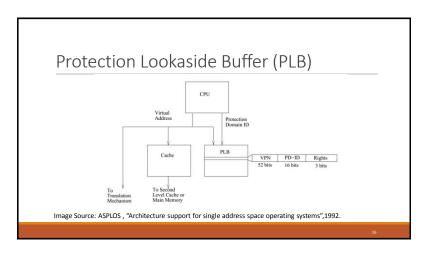

## PLB Advantages

No duplicate translation information • Each page has a single translation entry in TLB and memory hierarchy

Changing access permission of a memory region is cheaper

- Use a single PLB entry for the entire memory region (stack, code segment and etc.)

- Only required to modify one PLB entry

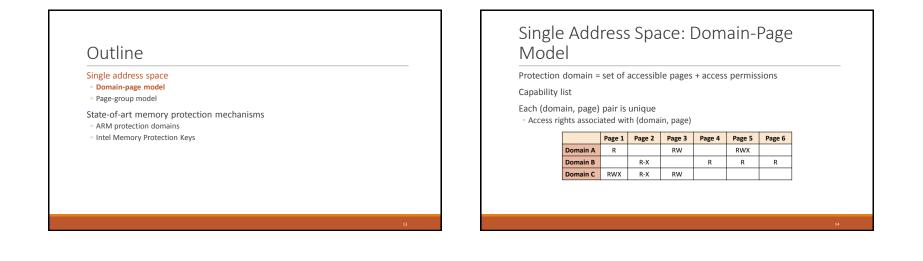

#### Outline

#### Single address space

- Domain-page model

- Page-group model

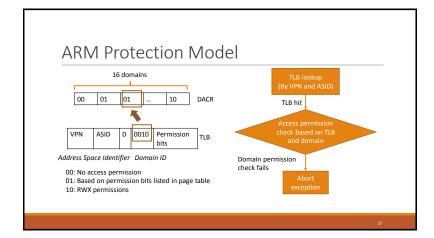

State-of-art memory protection mechanisms • ARM protection domains

Intel Memory Protection Keys

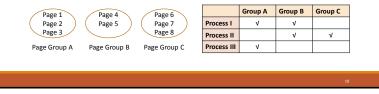

#### Single Address Space: Page-Group Model

Page group is a set of pages

• Each page belongs to a single page group

Access permissions associated with each page

• As opposed to (domain, page) pair in the domain-page group

Protection domain = set of accessible page groups + access permissions

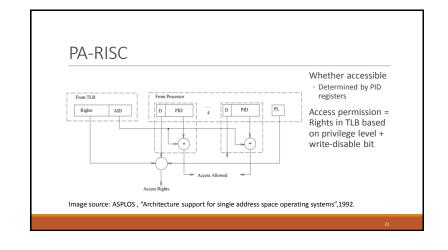

#### PA-RISC

An architecture of page-group model designed by HP

Each process has 4 page-group registers (PID) for accessible page group IDs • One additional write-disable bit that disables writes to the entire page group

Each process runs in one of the 4 privilege levels • 0 (the highest) to 3

|             | Privilege level | PID1 | PID2 | PID3 | PID4 |

|-------------|-----------------|------|------|------|------|

| Process I   | 0               | 3    | 11   | 6    | 9    |

| Process II  | 3               | 11   | 12   | 13   | 14   |

| Process III | 2               | 3    | 6    | 9    | 5    |

#### PA-RISC

Each page has unique translation information and access permissions

- Recorded in page table/TLB

- Access permission = read, write, execute and the corresponding privilege levels

E.g., writable from privilege level 0, readable from level 0, 1 and 2, and inaccessible from level 3

- No duplicate translation information

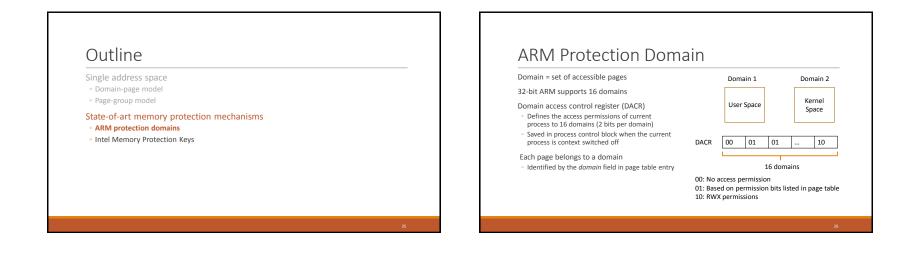

## Outline

Single address space

- Domain-page model

- Page-group model

State-of-art memory protection mechanisms

- ARM protection domains

- Intel Memory Protection Keys

### State-of-Art Memory Protection

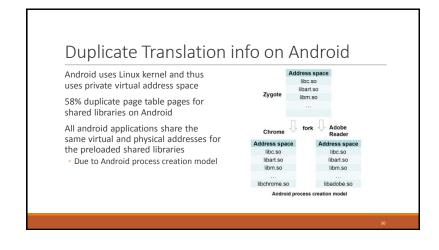

Modern architectures use private virtual address spaces • As supported in modern OSs such as Linux and FreeBSD

- However, they also provide other memory protection models

- Like ARM and Intel

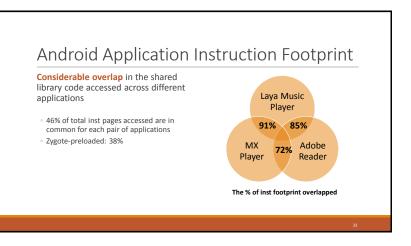

# ARM Protection Domain: A Use Case on Android

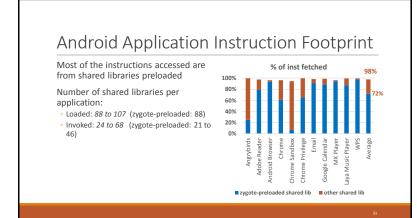

### Sharing TLB for Shared Libraries

To alleviate duplication, we share page table and TLB for preloaded shared libraries across all Android processes [Eurosys'16, IISWC'15] • In this talk we only focus on sharing TLB

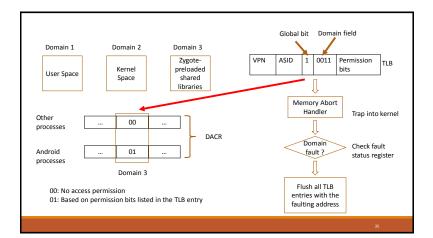

We use Global bit and ARM protection domain

#### Global bit

- Traditionally used for kernel-space translation

- Kernel space mappings are identical and therefore shared across processes

- Overrides Address Space Identifier (ASID) in TLB

# Sharing TLB for Shared Libraries

#### Global bit

- · Set the global bit in the page table entries of the preloaded shared libraries

- To share TLB entries

#### ARM protection domain

- . There are other process (system services and daemons) not forked from the template

- Prevents them from accessing the shared global TLB entries

- To unshare TLB entries

### Intel Memory Protection Keys

Similar to 32-bit ARM protection domain model • While 64-bit ARM removes it, Intel brings it back

Goal: Applications can efficiently modify access permissions at memory region granularity

Only applied to user-space pages

#### Intel Memory Protection Keys

Intel supports 16 domains

Protection key rights for user pages (PKU) register:

- Specifies the access permissions of current process to 16 domains

- 2 bits per domain (access disable bit + write disable bit)

- Configurable in user space

Each page is associated with a protection key

• Recorded in page table entry

Domain = set of accessible pages with the same protection key

Access permission check: page table entry permissions + protection key permissions (access disable? Write disable?)

#### Conclusions

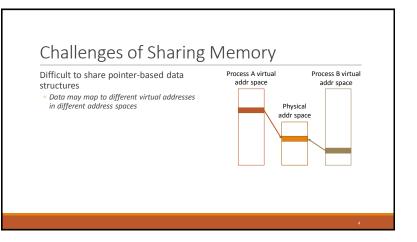

Per-process private virtual address space interferences with memory sharing

Duplication of address translation information resulted from private virtual address space

Changing access permissions at memory region granularity is expensive with page table

Other memory protection models can be leveraged:

Single address space

State-of-art mechanisms (ARM protection domain and Intel MPK)