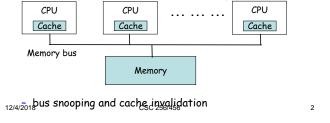

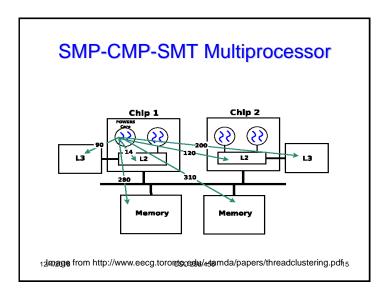

- A computer system in which two or more CPUs share full access to the main memory

- Each CPU might have its own cache and the coherence among multiple caches is maintained

- write operation by a CPU is visible to all other CPUs

- writes to the same location is seen in the same order by all CPUs (also called write serialization)

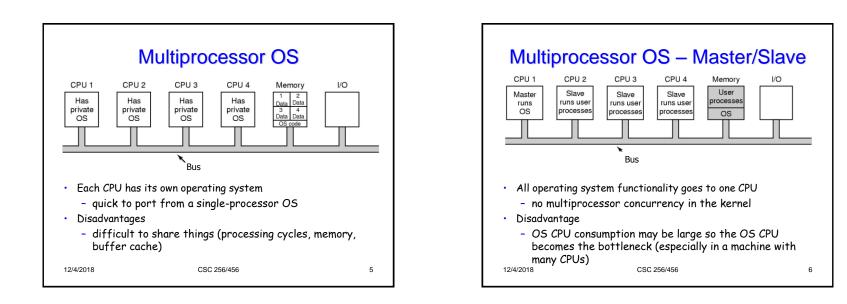

# Single-processor OS vs. Multiprocessor OS

- Single-processor OS

- easier to support kernel synchronization

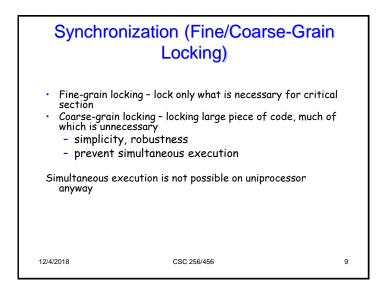

- coarse-grained locking vs. fine-grain locking

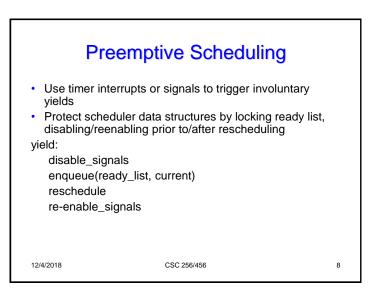

- disabling interrupts to prevent concurrent executions

- easier to perform scheduling

- which to run, not where to run

- Multiprocessor OS

- evolution of OS structure

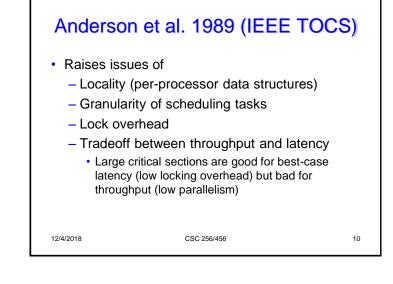

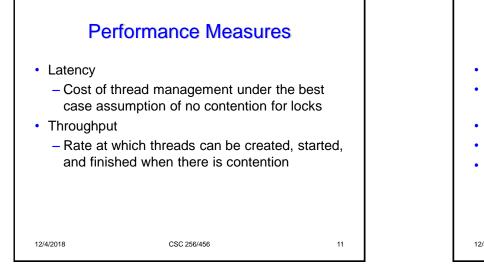

- synchronization

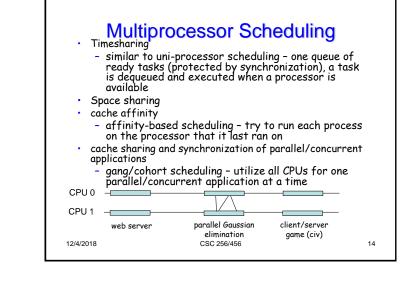

- scheduling

12/4/2018

CSC 256/456

4

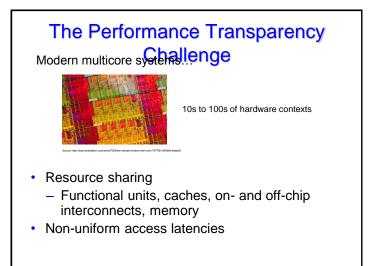

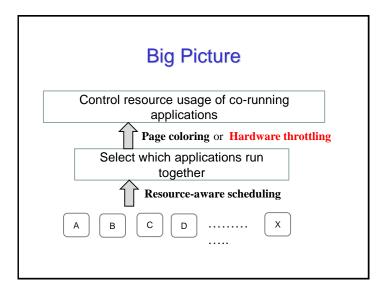

## Operating System Level Resource Management To Date

- Capitalistic generation of more requests results in more resource usage

- Performance: resource contention can result in significantly reduced overall performance

- Fairness: equal time slice does not necessarily guarantee equal progress

- Sharing oblivious: extraneous communication due to poor placement

17

#### Multi-Core Cache Challenges

- Hardware manages cache at the grain of cache lines.

- single program: data with different locality are mixed together

- shared cache: uncontrolled sharing threads

- compete for space -> interference

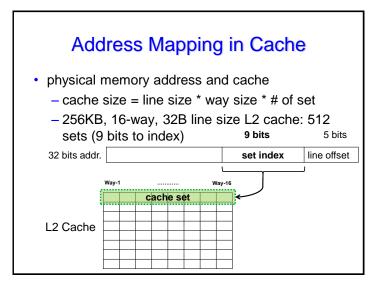

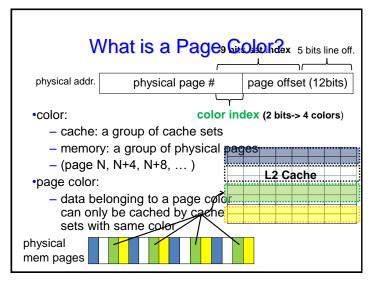

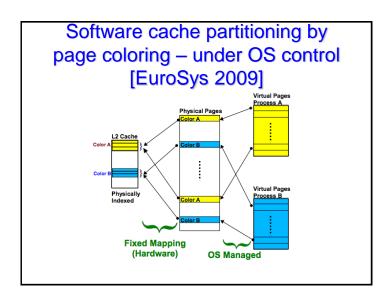

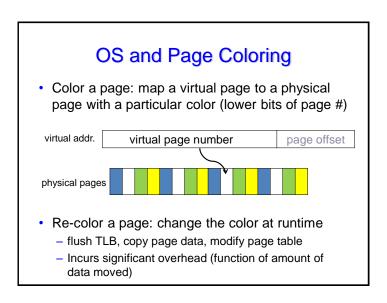

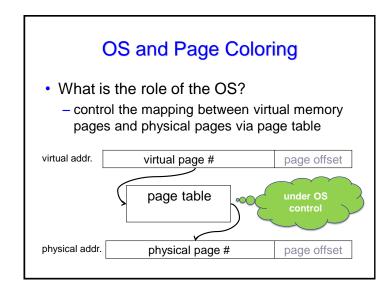

- Using OS as an auxiliary to manage cache

- high-level knowledge of program

- running state of the entire system

- how? page coloring

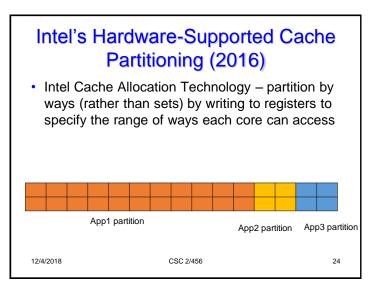

#### New Mechanism: Hardware Execution Throttling [Usenix'09]

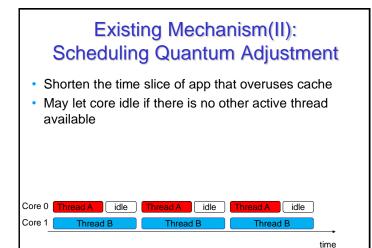

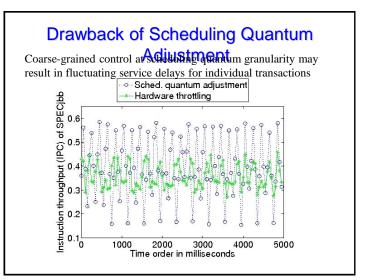

- · Throttle the execution speed of app that overuses cache

- Duty cycle modulation

- · CPU works only in duty cycles and stalls in non-duty cycles

- · Different from Dynamic Voltage Frequency Scaling

- Per-core vs. per-processor control

- Thermal vs. power management

- Enable/disable cache prefetchers

- L1 prefetchers

- IP: keeps track of instruction pointer for load history

- DCU: when detecting multiple loads from the same line within a time limit, prefetches the next line

- L2 prefetchers

- Adjacent line: Prefetches the adjacent line of required data

- Stream: looks at streams of data for regular patterns

## Hardware Execution Throttling [Usenix 2009]

- Instead of directly controlling cache resource allocation, throttle the execution speed of application that overuses resource

- Available throttling knobs

- Duty-cycle modulation

- Frequency/voltage scaling

- Cache prefetchers

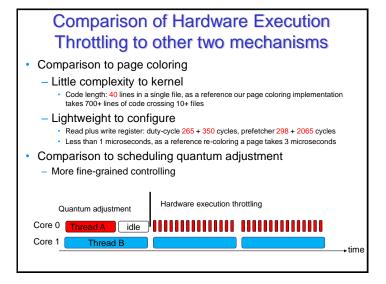

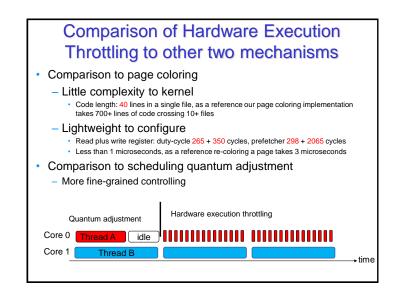

#### Comparing Hardware Execution Throttling to Page Coloring

- Kernel code modification complexity

- Code length: 40 lines in a single file, as a reference our page coloring implementation takes 700+ lines of code crossing 10+ files

- Runtime overhead of configuration

- Less than 1 microseconds, as a reference re-coloring a page takes 3 microseconds

#### Policies for Hardware Throttling-Enabled Multicore Management

- User-defined service level agreements (SLAs)

- Proportional progress among competing threads

- Unfairness metric: coefficient of variation of threads' performance

- Quality of service guarantee for high-priority application(s)

- Key challenge

- Throttling configuration space grows exponentially as the number of cores increases

- Quickly determining optimal or close to optimal throttling configurations is challenging

## TEMM: A Flexible Framework for Throttling-Enabled Multicore Management [ICPP'12]

- Customizable performance estimation model

- Reference configuration set and linear approximation

- Currently incorporates duty cycle modulation and frequency/voltage scaling

- Iterative refinement

- Prediction accuracy gets improved over time as more configurations are added into reference set