### Memory Consistency Model

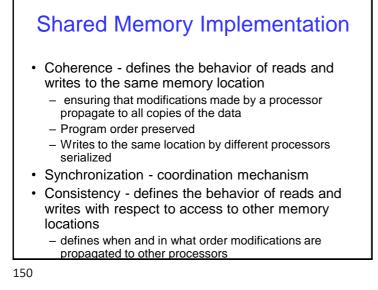

Specifies constraints on the order in which memory operations to different locations must appear to be performed with respect to one another

151

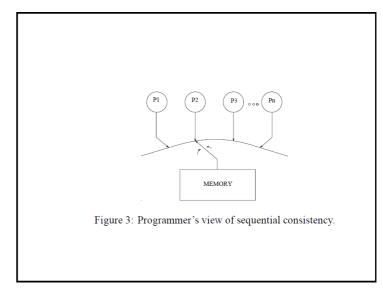

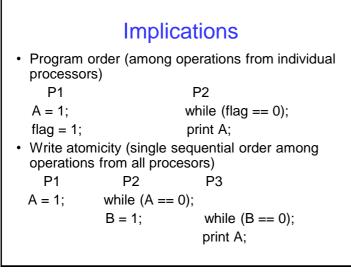

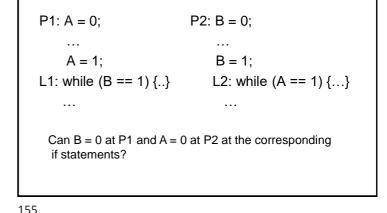

## Sequential Consistency

• ``A system is sequentially consistent if the result of any execution is the same as if the operations of all the processors were executed in some sequential order, and the operations of each individual processor appear in this sequence in the order specified by its program." [Lamport 79]

#### Dekker's Algorithm

158

# Consistency Model Classification

- Models vary along the following dimensions

- Local order order of a processor's accesses as seen locally

- Global order order of a single processor's accesses as seen by each of the other processors

- Interleaved order order of interleaving of different processor's accesses on other processors

## Drawbacks of Sequential Consistency

- SC imposes a performance penalty

- SC restricts any compiler optimization that can result in reordering memory operations

- Code motion, register allocation, common subexpression elimination, loop blocking, software pipelining

- SC restricts hardware generated memory re-orderings because of program-order and write-atomicity requirements

- Write Buffers, OOO instruction issue, pipelining of memory operations, lock-up free caches, non-atomic memory operations

159

## Memory Model Relaxations

- Possible relaxations

- -Write → Read

- -Write → Write

- Read  $\longrightarrow$  Read, Write

- Read other's write early

- Read own write early

- All Models provide some Safety net

- All models maintain uni-processor data and control dependencies

- Write atomicity is maintained by all the models except PC, RCpc, PowerPC

| Relaxation: | W →R<br>Order | W →W<br>Order | R →RW<br>Order | Read Others'<br>Write Early | Read Own<br>Write Early | Safety Net                      |

|-------------|---------------|---------------|----------------|-----------------------------|-------------------------|---------------------------------|

| IBM 370     | ~             |               |                |                             |                         | serialization<br>instructions   |

| TSO         | √             |               |                |                             | √                       | RMW                             |

| PC          | ~             |               |                | √                           | ✓                       | RMW                             |

| PSO         | √             | ~             |                |                             | ✓                       | RMW, STBAR                      |

| wo          | √             | ~             | ~              |                             | ✓                       | synchronization                 |

| RCsc        | ~             | ~             | ~              |                             | ~                       | release, acquire,<br>nsync, RMW |

| RCpc        | ~             | ~             | ~              | √                           | ~                       | release, acquire,<br>nsync, RMW |

| Alpha       | ~             | ~             | ~              |                             | ✓                       | MB, WMB                         |

| RMO         | √             | ~             | ~              |                             | ✓                       | various MEMBARs                 |

| PowerPC     | ~             | ~             | ~              | √                           | ~                       | SYNC                            |

162

Write Atomicity (continued)P1P2P3A = 1;while (A == 0);B = 1;while (B == 0);print A;370? TSO? PC?

#### Maintaining Write Atomicity

Initially A = B = C = 0

163

#### Consider Peterson's Algorithm

```

• Process P;

do {

flag[i] = true;

turn = j;

while (flag[j] && turn==j) ;

critical section

flag[i] = false;

remainder section

} while (1);

```

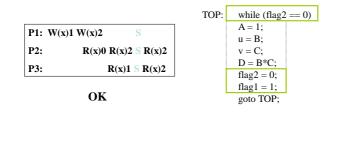

#### **Relaxing All Program Orders**

- Read or a Write operation may be reordered w.r.t following read or write to a different location

- Weak Ordering Model

- Release Consistency Model (RCsc / RCpc)

- Digital Alpha, Sparc V9 RMO, IBM Power PC

- Except Alpha, the above models allow reordering of two reads to the same location.

- RCpc and PowerPC allow a read to return the value of another processors write early.

#### Weak Ordering

- Classifies instructions into "Data" and "Sync"

- Reordering memory operations

between sync operations

- Hardware Implementation using WO counters, to issue sync operation counter must be zero

- No operations are issued until previous sync operation completes

- Synchronization accesses are sequentially consistent with respect to one another.

167

# Weak Ordering (Cont'd)

• Open up opportunities for buffering of reordered write operations between two synchronization points.

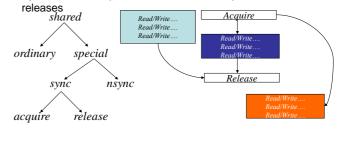

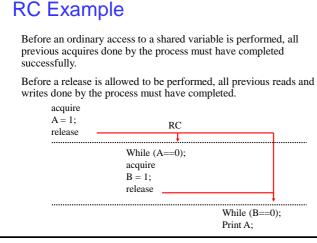

#### **Release Consistency**

- Extends WO and makes distinction among sync and nonsync operations

- Ordinary accesses are completely unordered with respect to each other

- Synchronization operations divided into acquires and releases

169

166

170

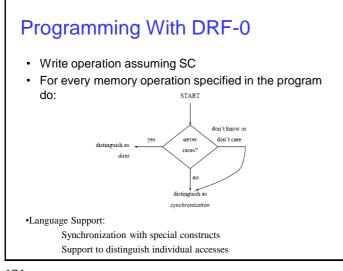

#### Programmer Centric View

- System Centric view is accompanied by higher level of complexity for programmers.

- Varied semantics for different models complicates the task of porting programs across systems.

Motivates for higher level of abstraction for programmers

· Provide informal rules for correct results defined by SC

i.e. Consistency Model is defined in terms of program level information provided by the programmer.

- DRF0 is one such approach which explores the information that is required to allow optimization similar to Weak Ordering.

- PL (Properly Labeled) approach for defining RCsc optimizations.

## Alpha, RMO and PowerPC

- Alpha employ RCsc model with Memory Barrier and Write Memory Barrier (WMB) fence instructions.

- Sparc V9 (RMO) employ RCsc model with MemBar instruction to specify any combination of RtoR, RtoW, WtoR, WtoW ordering.

- No need for RMW to preserve WtoR ordering

- Write atomicity is maintained

- PowerPC employ RCpc

- SYNC instruction similar to MB instruction except for RtoR order.

- RMW required to make writes atomic and preserve RtoR order.

171

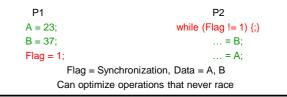

#### The Data-race-free-0 Model

Weak Ordering classifies instruction into "Data" and "Sync"

Key Goal is to formally distinguish operations as data or Synchronization on the basis of data races

- · An operation forms a race with another operation if,

- They access the same location && at least one operation is a write && there are no intervening operations between the two operations

## **Distinguishing Memory Operations**

- At the Programming Language Level

- Special synchronizaiton operation (library call)

- High-level paradigms

- Data or synchronization attribute with code or data

- At the hardware level

- Address regions

- Special instructions

175