93

#### Basic Hardware Mechanisms for Synchronization

- Test-and-set atomic exchange

- Fetch-and-op (e.g., increment) returns value and atomically performs op (e.g., increments it)

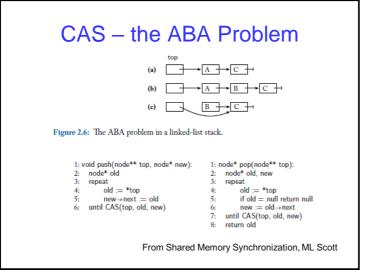

- Compare-and-swap compares the contents of two locations and swaps if identical

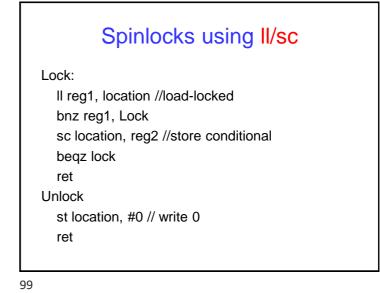

- Load-locked/store conditional pair of instructions – deduce atomicity if second instruction returns correct value

- Transaction support (e.g., Intel's TSX)

94

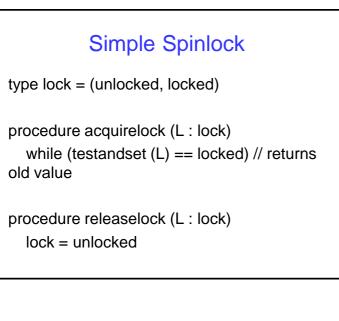

# Synchronization Using Special Instruction: TSL (test-and-set)

#### entry\_section: TSL R1, LOCK | copy lock to R1 and set lock to 1 CMP R1, #0 | was lock zero? JNE entry\_section | if it wasn't zero, lock was set, so loop RET | return; critical section entered exit\_section: MOV LOCK, #0 | store 0 into lock RET | return; out of critical section

98

## Using II/sc for Atomic Exchange • Swap the contents of R4 with the memory location specified by R1 try: mov R3, R4 ; mov exchange value I R2, 0(R1) ; load linked sc R3, 0(R1) ; store conditional beqz R3, try ; branch if store fails mov R4, R2 ; put load value in R4

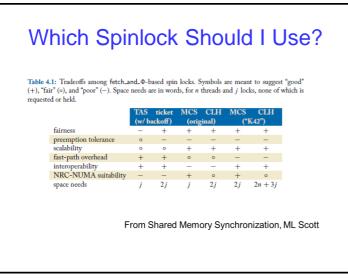

#### **Spinlock Algorithms**

- Test&test&set (w, w/o exponential backoff)

- Ticket lock (w, w/o proportional backoff)

- Array based queue locks

- MCS linked-list based queue locks

#### MCS Lock Acquire

| mcs_lo | ck_a | acqu | ire:   |

|--------|------|------|--------|

| st     | %g(  | ), [ | %01+4] |

| mov    | %01  | , %  | g3     |

| swap   | ) [% | 00]  | , %g3  |

| cmp    | %g3  | s, 0 |        |

| be     | .LI  | 4    |        |

| mov    | 1,   | %g2  |        |

| st     | %g2  | 2, [ | %o1]   |

| st     | %01  | , [  | %g3+4] |

| .LL9:  |      |      |        |

| ld     | [%c  | o1], | %g2    |

| cmp    | %g2  | 2, 0 |        |

| bne    | .LI  | .9   |        |

| nop    |      |      |        |

| .LL4:  |      |      |        |

| retl   |      |      |        |

| nop    |      |      |        |

|        |      |      |        |

102

#### MCS Lock Release

mcs lock release: ld [%o1+4], %g2 cmp %g2, 0 bne .LL11 nop cas [%00], %01, %q2 cmp %g2, %o1 be .LL10 nop .LL17: ld [%o1+4], %g2 cmp %g2, 0 be .LL17 nop .LL11: st %g0, [%g2] .LL10: retl nop

#### 103

106

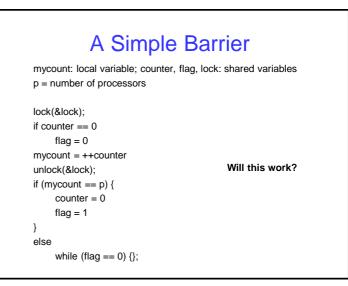

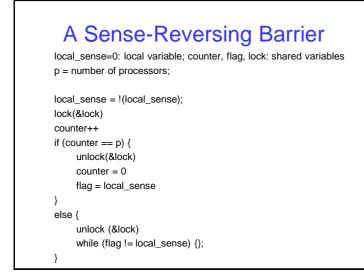

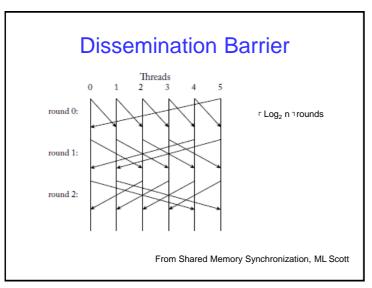

#### **Barrier Algorithms**

- · Centralized sense-reversing barrier

- Software combining tree

- Tournament barrier

- Dissemination barrier

- Combining (static) tree with improved locality

107

#### Which Barrier to Use?

Table 5.1: Tradeoffs among leading software barriers. Critical path lengths are in remote memory references (assuming broadcast on a CC-NUMA machine); they may not correspond precisely to wall-clock time. Space needs are in words. Constants *a* and *d* in the static tree barrier are arrival fan-in and departure fan-out, respectively. Fuzzy barriers are discussed in Section 5.3.1

|                           | central              | dissemination               | static tree                                                                       |

|---------------------------|----------------------|-----------------------------|-----------------------------------------------------------------------------------|

| space needs               |                      |                             |                                                                                   |

| CC-NUMA<br>NRC-NUMA       | n+1                  | $n+2n\lceil \log_2 n\rceil$ | 4n + 1<br>(5 + d)n                                                                |

| critical path length      |                      |                             |                                                                                   |

| CC-NUMA<br>NRC-NUMA       | n + 1<br>$\infty$    | $\lceil \log_2 n \rceil$    | $\lceil \log_a n \rceil + 1$<br>$\lceil \log_a n \rceil + \lceil \log_d n \rceil$ |

| total remote refs         |                      |                             | ou i ou i                                                                         |

| CC-NUMA<br>NRC-NUMA       | n + 1 2n<br>$\infty$ | $n \lceil \log_2 n \rceil$  | $n \\ 2n - 2$                                                                     |

| fuzzy barrier suitability | +                    | -                           | -                                                                                 |

| tolerance of changes in n | +                    | -                           | -                                                                                 |

From Shared Memory Synchronization, ML Scott

### **Performance Goals**

- · Low latency, short critical path

- · Low traffic

- Scalability

- · Low storage cost

- Fairness

110

#### Coherence A multiprocessor memory system is coherent if the results of any execution of a program are such that, for each location, it is possible to construct a hypothetical serial order of all operations to the location that is consistent with the result of the execution and - it ensures that modifications made by a processor propagate to all copies of the data - program order is preserved for each process in this hypothetical order - writes to the same location by different processors are serialized and the value returned by each read is the value written by the last write in the hypothetical order

#### Non-blocking algorithms

Failure or suspension of any thread cannot cause failure or suspension of another thread (no indefinite delay due to mutual exclusion)

- Operations defined on it do not require mutual exclusion over multiple instructions (use atomic primitives)

- Obstruction-free algorithm

- One that guarantees that a thread running in isolation will make progress (although livelock is possible)

- · Lock-free algorithm

- Operations guarantee that some process will complete its operation a finite amount of time, even if other processes halt

- Wait-free algorithm

- Operations can guarantee that EVERY non-faulting process will complete its operation in a finite amount of time

111

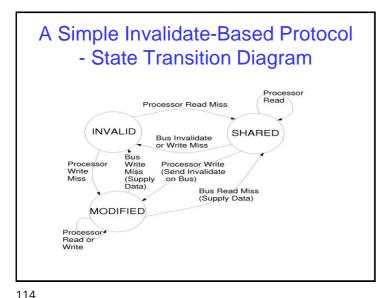

#### **Snoop-Based Coherence**

- Makes use of a shared broadcast medium to serialize events (all transactions visible to all controllers and in the same order)

- Write update-based protocol

- Write invalidate-based (e.g., basic MSI, MESI protocols)

- Cache controller uses a finite state machine (FSM) with a handful of stable states to track the status of each cache line

- Consists of a distributed algorithm represented by a collection of cooperating FSMs

#### **Correctness Requirements**

- · Need to avoid

- Deadlock caused by a cycle of resource dependencies

- Livelock activity without forward progress

- Starvation extreme form of unfairness where one or more processes do not make forward progress while others do

115

#### **Design Challenges**

- Cache controller and tag design

- Non-atomic state transitions

- Serialization

- · Cache hierarchies

- · Split-transaction buses