# Shared Memory: A Look Underneath

#### **Shared Memory Implementation**

- Coherence defines the behavior of reads and writes to the same memory location

- ensuring that modifications made by a processor propagate to all copies of the data

- Program order preserved

- Writes to the same location by different processors serialized

- · Synchronization coordination mechanism

- Consistency defines the behavior of reads and writes with respect to access to other memory locations

- defines when and in what order modifications are propagated to other processors

### Synchronization

- · Basic types

- Mutual exclusion

- Primitive: locks

- Events

- · Global event-based

- Primitive: Barriers

- · Point-to-point event-based

- Semaphores (blocking)

- Condition variables

- Flags (busy-waiting/spinning)

- Full-empty bits (hardware implementation; also considered message passing – produce-consumer)

- Interrupts

# Components of a Synchronization Event

- Acquire method (enter critical section, proceed past event)

- Waiting algorithm (busy waiting, blocking)

- Release method (enable others to proceed)

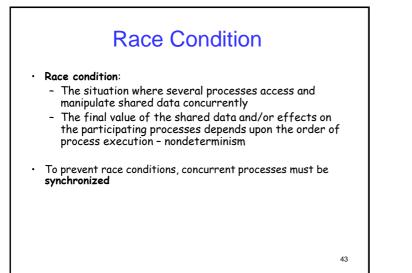

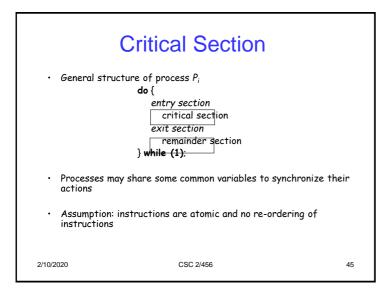

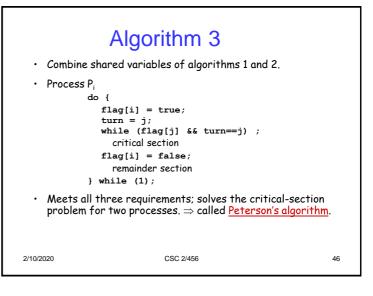

#### The Critical-Section Problem

- Problem context:

- n processes all competing to use some shared data

- Each process has a code segment, called *critical* section, in which the shared data is accessed.

- Find a solution that satisfies the following:

- 1. Mutual Exclusion. No two processes simultaneously in the critical section.

- 2. **Progress**. No process running outside its critical section may block other processes.

- 3. Bounded Waiting/Fairness. Given the set of concurrent processes, a bound must exist on the number of times that other processes are allowed to enter their critical sections after a process has made a request to enter its critical section and before that request is granted.

40

# **Basic Hardware Mechanisms for** Synchronization

- Test-and-set atomic exchange

- Fetch-and-op (e.g., increment) returns value and atomically performs op (e.g., increments it)

- Compare-and-swap compares the contents of two locations and swaps if identical

- · Load-locked/store conditional pair of instructions - deduce atomicity if second instruction returns correct value

- Transaction support (e.g., Intel's TSX)

### Simple Spinlock

type lock = (unlocked, locked)

procedure acquirelock (L : lock) while (testandset (L) == locked) // returns old value

procedure releaselock (L : lock) lock = unlocked

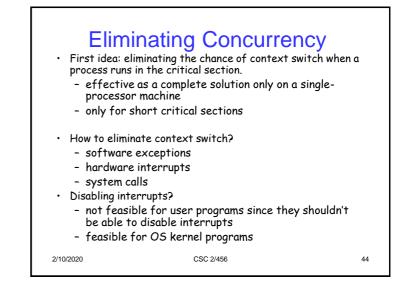

### Implementing Critical Sections Using • In all our solutions today, a process enters a loop until the

entry is granted  $\Rightarrow$  busy waiting.

- Problems with busy waiting:

- Waste of CPU time

- Potential for extra traffic/communication

- If a process is switched out of CPU during critical section

- other processes may have to waste a whole CPU quantum

- may even deadlock with strictly prioritized scheduling (priority inversion problem)

2/10/2020

49

#### Synchronization Using Special Instruction: TSL (test-and-set)

#### entry section: | copy lock to R1 and set lock to 1 TSL R1, LOCK CMP R1, #0 | was lock zero? JNE entry section | if it wasn't zero, lock was set, so loop RET | return; critical section entered exit\_section: MOV LOCK, #0 | store 0 into lock RET | return; out of critical section

| Implementing Locks Using<br>Test&Set<br>• On the SPARC Idstub moves an unsigned byte<br>into the destination register and rewrites the<br>same byte in memory to all 1s<br>_Lock_acquire:<br>Idstub [%00], %01<br>addcc %g0, %01, %g0<br>bne_Lock<br>nop<br>fin: |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| jmpl %r15+8, %g0                                                                                                                                                                                                                                                 |  |

| nop                                                                                                                                                                                                                                                              |  |

| _Lock_release:                                                                                                                                                                                                                                                   |  |

| st %g0, [%o0]                                                                                                                                                                                                                                                    |  |

| jmpl %r15+8, %g0                                                                                                                                                                                                                                                 |  |

| nop                                                                                                                                                                                                                                                              |  |

#### Using II/sc for Atomic Exchange

• Swap the contents of R4 with the memory location specified by R1

| try: mov R3, R4 | ; mov exchange value    |

|-----------------|-------------------------|

| ll R2, 0(R1)    | ; load linked           |

| sc R3, 0(R1)    | ; store conditional     |

| beqz R3, try    | ; branch if store fails |

| mov R4, R2      | ; put load value in R4  |

### Spinlock Algorithms

- Test&test&set (w, w/o exponential backoff)

- Ticket lock (w, w/o proportional backoff)

- Array based queue locks

- MCS linked-list based queue locks

#### MCS Lock Acquire

mcs lock acquire: st %g0, [%o1+4] mov %o1, %g3 swap [%o0], %g3 cmp %g3, 0 be .LL4 mov 1, %g2 st %g2, [%o1] st %o1, [%g3+4] .LL9: ld [%o1], %q2 cmp %g2, 0 bne .LL9 nop .LL4: retl nop

#### MCS Lock Release

mcs lock release: ld [%o1+4], %g2 cmp %g2, 0 bne .LL11 nop cas [%00], %01, %q2 cmp %g2, %o1 be .LL10 nop .LL17: ld [%o1+4], %g2 cmp %g2, 0 be .LL17 nop .LL11: st %g0, [%g2] .LL10: retl nop

#### **Barrier Algorithms**

- · Centralized sense-reversing barrier

- Software combining tree

- Tournament barrier

- Dissemination barrier

- · Combining tree with improved locality

#### A Sense-Reversing Barrier

local\_sense=0: local variable; counter, flag, lock: shared variables p = number of processors;

```

local_sense = !(local_sense);

lock(&lock)

counter++

if (counter == p) {

unlock(&lock)

counter = 0

flag = local_sense

}

else {

unlock (&lock)

while (flag != local_sense) {};

```

## **Performance Goals**

- · Low latency, short critical path

- Low traffic

- Scalability

- · Low storage cost

- Fairness

# Non-blocking algorithms

Failure or suspension of any thread cannot cause failure or suspension of another thread (no indefinite delay due to mutual exclusion)

- Operations defined on it do not require mutual exclusion over multiple instructions (use atomic primitives)

- · Obstruction-free algorithm

- One that guarantees that a thread running in isolation will make progress (although livelock is possible)

- · Lock-free algorithm

- Operations guarantee that some process will complete its operation a finite amount of time, even if other processes halt

- · Wait-free algorithm

- Operations can guarantee that EVERY non-faulting process will complete its operation in a finite amount of time

# Basic Hardware Mechanisms for Synchronization

- Test-and-set atomic exchange

- Fetch-and-op (e.g., increment) returns value and atomically performs op (e.g., increments it)

- Compare-and-swap compares the contents of two locations and swaps if identical

- Load-locked/store conditional pair of instructions – deduce atomicity if second instruction returns correct value

#### **Shared Memory Implementation**

- Coherence defines the behavior of reads and writes to the same memory location

- ensuring that modifications made by a processor propagate to all copies of the data

- Program order preserved

- Writes to the same location by different processors serialized

- · Synchronization coordination mechanism

- Consistency defines the behavior of reads and writes with respect to access to other memory locations

- defines when and in what order modifications are propagated to other processors