# CSC2/452 Computer Organization Assembly Language

Sreepathi Pai

URCS

September 23, 2019

◆□▶ ◆□▶ ◆臣▶ ◆臣▶ 臣 のへで

#### Outline

Administrivia

Recap

x86-64 assembly

Programming in Assembly

◆□▶ ◆□▶ ◆臣▶ ◆臣▶ 臣 のへで

#### Outline

Administrivia

Recap

x86-64 assembly

Programming in Assembly

◆□▶ ◆□▶ ◆三▶ ◆三▶ 三 のへの

### Assignments and Homeworks

#### Assigment #1 due this Friday

- Use the autograder to test your assignments

- No penalties for incorrect submissions before deadline

- Unlimited submissions before deadline

- Homework #3 out tomorrow

- Switching to a Tuesday–Monday schedule, instead of a Thu–Wed schedule

- Homework #3 will be due next Monday (Sep 30) in CLASS as usual

◆□▶ ◆□▶ ◆臣▶ ◆臣▶ 臣 の�?

#### Outline

Administrivia

#### Recap

x86-64 assembly

Programming in Assembly

▲□▶ ▲圖▶ ▲≣▶ ▲≣▶ = 三 ∽੧<⊙

# Previously

- Integers

- Floats

- Addresses

- Instructions

- The Instruction Set Architecture

- The programmer's interface to the processor

◆□▶ ◆□▶ ◆臣▶ ◆臣▶ 臣 のへで

#### Addresses: Summary

- ► Unsigned integers from 0 to 2<sup>n</sup> − 1 where n is size of address in bits

- Usually n = 64 on modern systems

- Labels are addresses

- Addresses can be loaded into registers

- leaq instruction on Intel 64 machines

- Effective addresses (the final address after any computations used to access memory) may be specified:

◆□▶ ◆□▶ ◆臣▶ ◆臣▶ 臣 の�?

- Directly (Absolute) e.g., 0x7f08e678d000

- Indirect e.g., mov (%rbx, %rsi, 1), 1

- Relative e.g., jmp

- Implicit e.g., push

#### Instruction Encoding

Instructions are encoded as multiword bitfields

- On Intel 64, they can occupy more than 64 bits

- Instruction encodings vary by processor

- They convey to the processor:

- What operation to perform

- What the operands (i.e. inputs and outputs) to that operation are

◆□▶ ◆□▶ ◆臣▶ ◆臣▶ 臣 の�?

Operands can be registers, memory or constants

- ▶ In the Intel ISA, not all combinations of operands are valid

- It is not fully orthogonal

#### Outline

Administrivia

Recap

x86-64 assembly

Programming in Assembly

◆□▶ ◆□▶ ◆三▶ ◆三▶ 三三 のへで

#### Nomenclature

Intel Processors have traditionally been known as x86

- 8086 (their first 16-bit processor)

- 80186, 80286

- 80386, 80486 (their 32-bit processors)

- 80586 became the Pentium, and Intel dropped the numbering scheme

- also 32-bit

- Courts said you couldn't trademark numbers

- The ISA for this was usually called 'x86' by everybody or IA-32 (by Intel)

◆□▶ ◆□▶ ◆臣▶ ◆臣▶ 臣 の�?

#### Going to 64-bits

The first 64-bit version of the x86 was made by AMD

- Was a new ISA based on x86 (much nicer!)

- Therefore sometimes called 'amd64'

- Also referred to as 'x86-64'

- Intel calls their version (which is not exactly the same) 'Intel 64'

Sometimes you will see 'x64' to refer to this architecture

- Intel's original proposal for a 64-bit processor was called Itanium

- 'IA-64', but the ISA was not widely adopted (sells about 250K each year)

◆□▶ ◆□▶ ◆臣▶ ◆臣▶ 臣 の�?

Don't confuse IA-32 and IA-64 – they're not related at all!

#### An overview of the Intel Manuals

- Volume 1: Basic Architecture

- Overview of all the data types, instructions, etc. that a programmer needs to know (500 pages)

- Recommend reading this

- Volume 2: Instruction Set Reference

- Describes every instruction, its operands, its encoding, and semantics (2242 pages)

- Look this up when you have to

- Volume 3: System Programming Guide

- If you're writing an OS or compiler or linker or assembler (1700 pages)

- Volume 4: Model-specific registers

- MSRs allow you to control processors (500 pages)

- Put them to sleep, set their operating mode, etc.

- You could order paper copies from Intel for free in the past

- You still can, though not for free

## Recall: Intel Instruction Format

#### B.1 MACHINE INSTRUCTION FORMAT

All Intel Architecture instructions are encoded using subsets of the general machine instruction format shown in Figure B-1. Each instruction consists of:

- an opcode

- a register and/or address mode specifier consisting of the ModR/M byte and sometimes the scale-index-base (SIB) byte (if required)

- a displacement and an immediate data field (if required)

| Legacy Prefixes REX Prefixes                                                                                                                                         | 76543210 76543210 76543210                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Grp 1, Grp 2, (optional)<br>Grp 3, Grp 4                                                                                                                             | 1, 2, or 3 Byte Opcodes (T = Opcode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |

| Mod Reg* R/M Scale Index E<br>ModR/M Byte SIB Byte<br>Register and/or Address                                                                                        | Mod Reg* R/M Scale Index Base d32   16   8   None d32   16   8   None d32   16   8   None d32   16   8   None d32   16   9   None d32   16   16   None d32   16   16   None d32   16   16   None d32   16   16   16   16   16   16   16   1 |  |  |  |  |  |  |

| Register and/or Address<br>Mode Specifier * The Reg Field may be used as an<br>opcode extension field (TTT) and as a<br>way to encode diagnostic registers<br>(eee). |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |

Figure B-1. General Machine Instruction Format

Source: Intel 64 and IA-32 Architectures: Software Developers Manual, Volume 2, Instruction Set Reference (A–Z), pg. 2095

200

크

#### The pushq instruction

11 0000 55

pushq %rbp

◆□▶ ◆□▶ ◆臣▶ ◆臣▶ 臣 のへで

- Line 11, address 0000 of main

- pushq %rbp is encoded as 0x55

## The PUSH instruction

- %rbp is a 64-bit register

- ▶ That has Opcode 50+*rd*

- That's 0x50, and the 0 format

- Page 1175 in Vol 2

| Opcode*       | Instruction | Op/<br>En | 64-Bit<br>Mode | Compat/<br>Leg Mode | Description |

|---------------|-------------|-----------|----------------|---------------------|-------------|

| FF /6         | PUSH r/m16  | м         | Valid          | Valid               | Push r/m16. |

| FF /6         | PUSH r/m32  | м         | N.E.           | Valid               | Push r/m32. |

| FF /6         | PUSH r/m64  | М         | Valid          | N.E.                | Push r/m64. |

| 50+ <i>rw</i> | PUSH r16    | 0         | Valid          | Valid               | Push r16.   |

| 50+rd         | PUSH r32    | 0         | N.E.           | Valid               | Push r32.   |

| 50+rd         | PUSH r64    | 0         | Valid          | N.E.                | Push r64.   |

| 6A ib         | PUSH imm8   | 1         | Valid          | Valid               | Push imm8.  |

| 68 iw         | PUSH imm16  | 1         | Valid          | Valid               | Push imm16. |

| 68 id         | PUSH imm32  | 1         | Valid          | Valid               | Push imm32. |

| 0E            | PUSH CS     | Z0        | Invalid        | Valid               | Push CS.    |

| 16            | PUSH SS     | ZO        | Invalid        | Valid               | Push SS.    |

| 1E            | PUSH DS     | ZO        | Invalid        | Valid               | Push DS.    |

| 06            | PUSH ES     | Z0        | Invalid        | Valid               | Push ES.    |

| OF AO         | PUSH FS     | ZO        | Valid          | Valid               | Push FS.    |

| OF A8         | PUSH GS     | ZO        | Valid          | Valid               | Push GS.    |

#### PUSH—Push Word, Doubleword or Quadword Onto the Stack

\* See IA-32 Architecture Compatibility section below.

#### Instruction Operand Encoding

| Op/En | Operand 1       | Operand 2 | Operand 3 | Operand 4 |  |

|-------|-----------------|-----------|-----------|-----------|--|

| М     | ModRM:r/m (r)   | NA        | NA        | NA        |  |

| 0     | opcode + rd (r) | NA        | NA        | NA        |  |

| 1     | imm8/16/32      | NA        | NA        | NA        |  |

| ZO    | NA              | NA        | NA        | NA        |  |

#### Description

Decrements the stack pointer and then stores the source operand on the top of the stack. Address and operand sizes are determined and used as follows:

◆□▶ ◆□▶ ◆三▶ ◆三▶ 三三 のへで

## What's +rd?

- +rb, +rw, +rd, +ro Indicated the lower 3 bits of the opcode byte is used to encode the register operand without a modR/M byte. The instruction lists the corresponding hexadecimal value of the opcode byte with low 3 bits as 000b. In non-64-bit mode, a register code, from 0 through 7, is added to the hexadecimal value of the opcode byte. In 64-bit mode, indicates the four bit field of REX.b and opcode[2:0] field encodes the register operand of the instruction. "+ro" is asplicable only in 64-bit mode. See Table 2-1 for the codes.

- +i A number used in floating-point instructions when one of the operands is ST(i) from the FPU register stack. The number ( which can range from 0 to 7) is added to the hexadecimal byte given at the left of the plus sign to form a single opcode byte.

| byte register word register |                             |           |          | dword register |           |          | quadword register<br>(64-Bit Mode only) |           |          |       |           |

|-----------------------------|-----------------------------|-----------|----------|----------------|-----------|----------|-----------------------------------------|-----------|----------|-------|-----------|

| Register                    | REX.B                       | Reg Field | Register | REX.B          | Reg Field | Register | REX.B                                   | Reg Field | Register | REX.B | Reg Field |

| AL                          | None                        | 0         | AX       | None           | 0         | EAX      | None                                    | 0         | RAX      | None  | 0         |

| CL                          | None                        | 1         | CX       | None           | 1         | ECX      | None                                    | 1         | RCX      | None  | 1         |

| DL                          | None                        | 2         | DX       | None           | 2         | EDX      | None                                    | 2         | RDX      | None  | 2         |

| BL                          | None                        | 3         | BX       | None           | 3         | EBX      | None                                    | 3         | RBX      | None  | 3         |

| AH                          | Not<br>encodab<br>le (N.E.) | 4         | SP       | None           | 4         | ESP      | None                                    | 4         | N/A      | N/A   | N/A       |

| CH                          | N.E.                        | 5         | BP       | None           | 5         | EBP      | None                                    | 5         | N/A      | N/A   | N/A       |

| DH                          | N.E.                        | 6         | SI       | None           | 6         | ESI      | None                                    | 6         | N/A      | N/A   | N/A       |

| BH                          | N.E.                        | 7         | DI       | None           | 7         | EDI      | None                                    | 7         | N/A      | N/A   | N/A       |

| SPL                         | Yes                         | 4         | SP       | None           | 4         | ESP      | None                                    | 4         | RSP      | None  | 4         |

| BPL                         | Yes                         | 5         | BP       | None           | 5         | EBP      | None                                    | 5         | RBP      | None  | 5         |

◆□▶ ◆□▶ ◆注▶ ◆注▶ 注 のへで

#### Table 3-1. Register Codes Associated With +rb, +rw, +rd, +ro

3-2 Vol. 2A

- +rd indicates EBP is 5

- But EBP is 32-bits!

Page 104 of Vol 2

## In 64-bit Mode ...

#### 2.2.1.7 Default 64-Bit Operand Size

In 64-bit mode, two groups of instructions have a default operand size of 64 bits (do not need a REX prefix for this operand size). These are:

- Near branches.

- All instructions, except far branches, that implicitly reference the RSP.

- Since PUSH implicitly references register RSP, this makes 0x55 reference %rbp, not %ebp

◆□▶ ◆□▶ ◆注▶ ◆注▶ 注 のへで

In 64-bit mode, you can't push EBP.

- The REX prefix of 0x48 tells the processor to use 64-bit registers

- 12 0001 4889E5 movq %rsp, %rbp

- It is not needed for PUSH

Page 46 of Vol 2

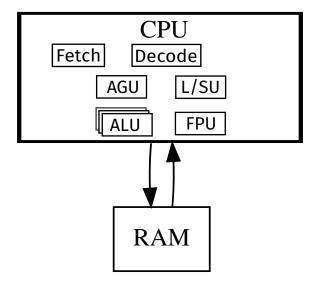

#### CPU: The Decode Unit

◆□▶ ◆□▶ ◆臣▶ ◆臣▶ 臣 のへで

#### Outline

Administrivia

Recap

x86-64 assembly

Programming in Assembly

◆□▶ ◆□▶ ◆三▶ ◆三▶ 三三 のへで

# Features of High-level Languages (HLL)

#### Variables

- Arrays

- Complex Expressions (large number of operands)

- Arithmetic Operations, Logical Operations, etc.

(日) (문) (문) (문) (문)

- Block structure { and } in C-like languages

- Conditionals if-then-else

- Loops while, for

- Functions

## Features of Assembly Languages

#### Memory

- Registers

- Expressions are very simple, maybe up to 3 operands

- Need to break up complex expressions into simple expressions

- No block structure

- No direct equivalent for conditionals

- No direct equivalent for loops

- Limited support for functions

### **Translating Variables**

Typically variables in programs like C end up in either:

- Memory

- Registers

- Memory can be seen as two logical regions heap, and stack

- Heap usually stores global variables and data

- Stack usually stores (function) local variables

- In assembly language, a variable is in:

- a register, if instruction uses a register operand, e.g. %rax (or any other register),

- heap, if instruction uses an indirect memory operand, e.g. (%rbx)

- stack, if an instruction uses an indirect memory operand relative to %rbp or %rsp, e.g. -4(%rbp)

- Since accessing memory is slow, a variable may be loaded from memory into a register before operating on it

- In which case, for some time, it exists in both memory and registers

## Example

```

int sum(int a, int b) {

int c = 0;

c = a + b:

return c;

}

00000000000000 <sum>:

0:

55

%rbp

push

1:

48 89 e5

mov

4:

89 7d ec

mov

7:

89 75 e8

mov

a:

c7 45 fc 00 00 00 00

movl

8b 55 ec

11:

mov

14:

8b 45 e8

mov

17:

01 d0

add

89 45 fc

19:

mov

1c:

8b 45 fc

mov

1f:

%rbp

5d

pop

20:

c3

retq

```

```

%rsp,%rbp

%edi,-0x14(%rbp)

# A r->s

%esi,-0x18(%rbp)

# B r->s

#Cs

$0x0,-0x4(%rbp)

-0x14(%rbp),%edx

# A s->r

-0x18(%rbp),%eax

# B s->r

%edx,%eax

# A + B

%eax,-0x4(%rbp)

# store into C

-0x4(%rbp),%eax

# C s \rightarrow r (rval)

```

r->s, register to stack. s->r, stack to register

rval, return value (must be stored in %eax)

## Translating Expressions

Most instructions accept only 1, 2 or 3 operands

- Example: ADD instruction takes two operands

- ▶ ADD %r1, %r2

- ▶ %r2 = %r1 + %r2

- An expression like s = a + b + c needs to be broken down to fit this instruction

◆□▶ ◆□▶ ◆三▶ ◆三▶ 三三 のへで

Do this by introducing temporaries

```

tmp = a + b;

tmp = tmp + c;

s = tmp;

```

## Translating Expressions: Example

|   | nt sum30<br>0:<br>1:<br>4:<br>7:<br>a:<br>int s = | (int a<br>55<br>48 89<br>89 7d<br>89 75<br>89 55<br>= 0; | ec<br>e8<br>e4 | int c) { | mov<br>mov                      | %edx,-0x1c(%rbp) | #<br># | B<br>C |

|---|---------------------------------------------------|----------------------------------------------------------|----------------|----------|---------------------------------|------------------|--------|--------|

|   | d:                                                | c7 45                                                    | fc 00 00       | 00 00    | movl                            | \$0x0,-0x4(%rbp) | #      | S      |

|   | s = (a<br>14:<br>17:<br>1a:<br>1c:<br>1f:<br>21:  | 8b 55<br>8b 45<br>01 c2<br>8b 45<br>01 d0                | ec<br>e8<br>e4 |          | mov<br>add<br>mov<br>add<br>mov | -0x1c(%rbp),%eax | #      |        |

| } | return<br>24:                                     | s;<br>8b 45                                              | fc             |          | mov                             | -0x4(%rbp),%eax  |        |        |

| J | 27:<br>28:                                        | 5d<br>c3                                                 |                |          | pop<br>retq                     | %rbp             |        |        |

◆□▶ ◆□▶ ◆三▶ ◆三▶ 三三 のへで

## Translating Conditionals

```

int max(int a, int b) {

if(a > b) {

return a;

} else {

return b;

}

}

```

(日) (월) (문) (문) (문)

#### Assembly Language Conditionals: Three components

◆□▶ ◆□▶ ◆臣▶ ◆臣▶ 臣 のへで

- Comparison functions

- Conditional jumps

- Unconditional jumps

#### Disassembly of max

00000000000000 <max>:

| 0:  | 55 |    |    |  |

|-----|----|----|----|--|

| 1:  | 48 | 89 | e5 |  |

| 4:  | 89 | 7d | fc |  |

| 7:  | 89 | 75 | f8 |  |

| a:  | 8b | 45 | fc |  |

| d:  | Зb | 45 | f8 |  |

| 10: | 7e | 05 |    |  |

| 12: | 8b | 45 | fc |  |

| 15: | eb | 03 |    |  |

| 17: | 8b | 45 | f8 |  |

| 1a: | 5d |    |    |  |

| 1b: | c3 |    |    |  |

push %rbp %rsp,%rbp mov %edi,-0x4(%rbp) mov %esi,-0x8(%rbp) mov -0x4(%rbp),%eax mov -0x8(%rbp),%eax  $\mathtt{cmp}$ jle 17 <max+0x17> -0x4(%rbp),%eax mov jmp 1a < max+0x1a >-0x8(%rbp),%eax mov %rbp pop retq

(日) (문) (문) (문)

- # COMPARISON

# COND. JUMP

- # UNCOND. JUMP

æ

#### Comparison

| a:  | 8b 45 fc | mov | -0x4(%rbp),%eax          |              |

|-----|----------|-----|--------------------------|--------------|

| d:  | 3b 45 f8 | cmp | -0x8(%rbp),%eax          | # COMPARISON |

| 10: | 7e 05    | jle | 17 <max+0x17></max+0x17> | # COND. JUMP |

|     |          |     |                          |              |

| 17: | 8b 45 f8 | mov | -0x8(%rbp),%eax          | # RETURN B   |

- We know a is on the stack at -0x4(%rbp)

- We know b is on the stack at -0x8(%rbp)

- The cmp instruction compares b with %eax (which contains a)

For cmp x, y, the cmp instruction calculates y - x

- The results of the cmp operation are stored in the EFLAGS register. Of relevance to jle:

- ZF: Zero flag: set to 1 if y x == 0

- OF: Overflow flag: set to 1 if y x underflowed or overflowed

- SF: Sign flag: set to sign bit of y x

Part of the family of jcc instructions

- cc is conditional code

- Jump If Less Or Equal

- If ZF is 0, then y = x.

- If OF  $\neq$  SF then, y < x

- ► To understand this, work out all cases of y < x where they are +/+,-/-,+/-,-/+

◆□▶ ◆□▶ ◆臣▶ ◆臣▶ 臣 の�?

- Note that at machine level, two's complement integers "wrap-around" on overflow and underflow

- Here, the conditional jump to max+0x17 occurs if  $a \le b$

- Otherwise control "falls through" to the next instruction

## Conditionals: Full translation

Evaluate the condition and jump to the Else part Or fall through to the Then part 8b 45 fc -0x4(%rbp),%eax a: mov d: 3b 45 f8 -0x8(%rbp),%eax # COMPARISON cmp 17 <max+0x17> 10: 7e 05 # COND. JUMP jle The Then Part 12: 8b 45 fc -0x4(%rbp),%eaxmov 15: eb 03 1a < max+0x1a >jmp # UNCOND. JUMP The Else Part 17: 8b 45 f8 -0x8(%rbp),%eax mov Code immediately after Else 1a: 5d %rbp pop

(日) (四) (王) (王) (王)

臣

#### Loops

```

int div(int a, int b) {

int q = 0;

while(a - b > 0) {

a = a - b;

q = q + 1;

}

return q;

}

```

(Ignore what this function is trying to do)

◆□▶ ◆□▶ ◆臣▶ ◆臣▶ 臣 のへで

#### Loops: Removing Structure

```

int div2(int a, int b) {

int q = 0;

goto loop_test;

loop_body:

a = a - b:

q = q + 1;

loop_test:

if((a - b > 0))

goto loop_body;

loop_exit: /* not required, for clarity only */

return q;

}

```

We can convert a while loop into unstructured form using goto and if

#### Unstructured Loop Translation

- goto is an unconditional jmp

- The if(cond) goto form is just a conditional jump

◆□▶ ◆□▶ ◆三▶ ◆三▶ 三三 のへで

#### Translation

0000000000002c <div2>:

| 3d: | eb Ob       | jmp  | 4a <div2+0x1e></div2+0x1e> | <pre># goto loop_test</pre>  |

|-----|-------------|------|----------------------------|------------------------------|

| 3f: | 90          | nop  |                            | <pre># loop_body:</pre>      |

| 40: | 8b 45 e8    | mov  | -0x18(%rbp),%eax           |                              |

| 43: | 29 45 ec    | sub  | %eax,-0x14(%rbp)           |                              |

| 46: | 83 45 fc 01 | addl | \$0x1,-0x4(%rbp)           |                              |

| 4a: | 8b 45 ec    | mov  | -0x14(%rbp),%eax           | # loop_test: a - b           |

| 4d: | 2b 45 e8    | sub  | -0x18(%rbp),%eax           | -                            |

| 50: | 85 c0       | test | %eax,%eax                  | # is a - b > 0?              |

| 52: | 7f eb       | jg   | 3f <div2+0x13></div2+0x13> | <pre># jump if greater</pre> |

| 54: | 90          | nop  |                            |                              |

| 55: | 8b 45 fc    | mov  | -0x4(%rbp),%eax            |                              |

| 58: | 5d          | рор  | %rbp                       |                              |

| 59: | c3          | retq |                            |                              |

|     |             |      |                            |                              |

◆□▶ ◆□▶ ◆三▶ ◆三▶ 三三 のへで

test performs a logical and of its two operands and sets ZF and SF

- sub sets the OF flag

- jg jumps if ZF=0 and SF=OF

#### Translating for loops

```

int iter(int a, int b) {

int i;

for(i = 0; i < 10; i++) {

a = a + b;

}

return i;

}</pre>

```

(□) (@) (E) (E) E

#### De-structuring for loops

```

int iter2(int a, int b) {

int i;

loop_head:

i = 0;

goto loop_test;

loop_body:

a = a + b;

i++; /* loop update */

loop_test:

if(i < 10)

goto loop_body;

loop_exit:

return i;

}

```

◆□▶ ◆□▶ ◆三▶ ◆三▶ 三三 のへで

## Translating for loops

00000000000028 <iter2>:

| 32:<br>39: | c7 45 fc 00 00 00 00<br>eb 0b | movl<br>jmp | <pre>\$0x0,-0x4(%rbp) 46 <iter2+0x1e></iter2+0x1e></pre> | # i = 0<br># goto loop_test               |

|------------|-------------------------------|-------------|----------------------------------------------------------|-------------------------------------------|

| 3b:<br>3c: | 90<br>8b 45 e8                | nop<br>mov  | -0x18(%rbp),%eax                                         | <pre># loop_body:</pre>                   |

| 3f:        | 01 45 ec                      | add         | %eax,-0x14(%rbp)                                         | # a = a + b                               |

| 42:        | 83 45 fc 01                   | addl        | \$0x1,-0x4(%rbp)                                         |                                           |

| -12.       | 00 10 10 01                   | uuur        | WORI, ORI(MIDP)                                          | # 1                                       |

| 46:        | 83 7d fc 09                   | cmpl        | \$0x9,-0x4(%rbp)                                         | <pre># loop_test:</pre>                   |

| 4a:        | 7e ef                         | jle         | 3b <iter2+0x13></iter2+0x13>                             | <pre># if(i &lt; 10) goto loop_body</pre> |

|            |                               | 5           |                                                          |                                           |

| 4c:        | 90                            | nop         |                                                          |                                           |

|            |                               |             |                                                          |                                           |

▲□▶ ▲圖▶ ▲目▶ ▲目▶ 目 のへで

. . .

## Basics of translating HLLs to Assembly (so far)

- Simplify expressions

- Find locations for variables

- Destructure loops

- Use conditional and unconditional jumps

◆□▶ ◆□▶ ◆三▶ ◆三▶ 三三 のへで

### Handling Function Calls

- How to pass arguments to function?

- How to jump to a function?

- How to come back to just after call location?

- How does ret know where to return to?

- How to receive the return value from a function?

◆□▶ ◆□▶ ◆臣▶ ◆臣▶ 臣 の�?

#### References

#### Read Chapter 3 of the textbook

Esp. the Figure detailing all the registers

◆□▶ ◆□▶ ◆三▶ ◆三▶ 三三 のへで