# CSC 252: Computer Organization Spring 2018: Lecture 11

#### Instructor: Yuhao Zhu

Department of Computer Science University of Rochester

**Action Items:**

Assignment 3 is due March 2, midnight

### Announcement

- Programming Assignment 3 is out

- Due on March 2, midnight

| 25 | 26 | 27 | 28 | Mar 1 | 2<br>due | 3 |

|----|----|----|----|-------|----------|---|

### Announcement

- There is another faculty candidate talk

- Monday, noon, this room, with food

Monday, February 26, 2018 12:00 PM 1400 Wegmans Hall

Zhen Bai Carnegie Mellon University

Augmenting Social Reality for Good

The profound transformation of the employment landscape requires advanced socioemotional skills for effective collaboration and communication in cross-disciplinary and diverse cultural environments. People's ability to cope with social situations and exert influence on others is critically linked with their ability to understand and affect meanings that others associate with their surroundings. This association is "meaning making", the transformation of reality "in the raw" to socially constructed reality, which fundamentally affects how individuals act towards objects, people and situations. It remains challenging, however, to help people navigate their social reality because it is situated in the immediate surroundings, constantly changes through social interaction, and is only accessible through communication.

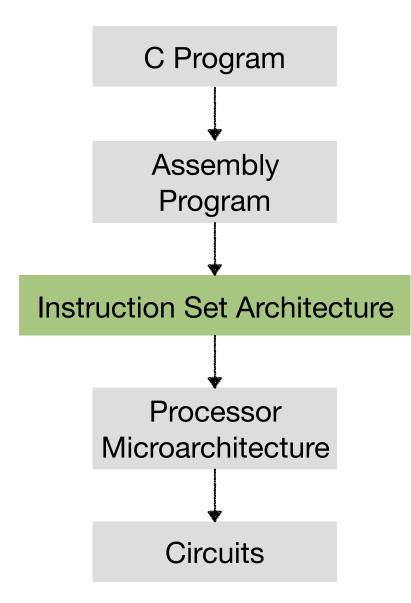

# So far in 252...

- ISA is the interface between assembly programs and microarchitecture

- Assembly view:

- How to program the machine, based on instructions and processor states (registers, memory, condition codes, etc.)?

- Instructions are executed sequentially

- Microarchitecture view:

- What hardware needs to be built to run assembly programs?

- How to run programs as fast (energy-efficient) as possible?

## **Today: Processor Microarchitecture**

- The Y86-64 ISA: Simplified version of x86-64

- How an assembler works

- Sequential, single-cycle microarchitecture implementation

- Basic idea

- Hardware implementation

# How are Instructions Encoded in Binary?

- Remember that in a stored program computer, instructions are stored in memory as bits (just like data)

- Each instruction is fetched (according to the address specified in the PC), decoded, and executed by the CPU

- The ISA defines the format of an instruction (syntax) and its meaning (semantics)

- Each instruction has two major fields: opcode and operand

- The OPCODE field says what the instruction does (e.g. ADD)

- The OPERAND field(s) say where to find inputs and outputs

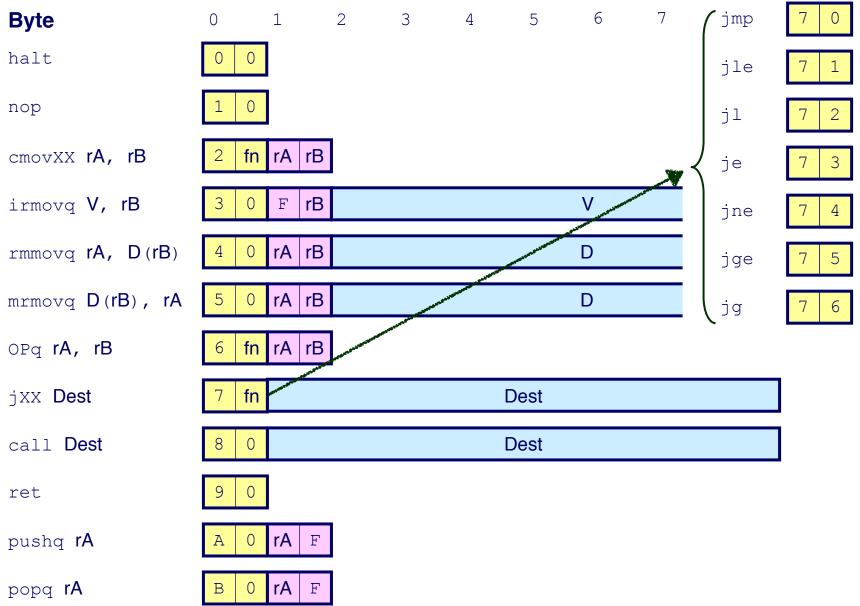

### Y86-64 Instruction Set

| Byte                | 0          | 1       | 2        | 3 | 4 | 5    | 6 | 7 | 8 | 9 |

|---------------------|------------|---------|----------|---|---|------|---|---|---|---|

| halt                | 0 (        |         |          |   |   |      |   |   |   |   |

| nop                 | 1 (        | )       |          |   |   |      |   |   |   |   |

| cmovXX rA, rB       | 2 <b>f</b> | n rA rE | 3        |   |   |      |   |   |   |   |

| irmovq V, rB        | 3 (        | ) F r   | 3        |   |   |      | V |   |   |   |

| rmmovq rA, D(rB)    | 4 (        | rA rE   | 3        |   |   |      | D |   |   |   |

| mrmovq $D(rB)$ , rA | 5 (        | rA rE   | 3        |   |   |      | D |   |   |   |

| OPq rA, rB          | 6 <b>f</b> | n rA rE | 3        |   |   |      |   |   |   |   |

| jxx Dest            | 7 <b>f</b> | n       |          |   |   | Dest |   |   |   |   |

| call <b>Dest</b>    | 8 (        | )       |          |   |   | Dest |   |   |   |   |

| ret                 | 9 (        | )       |          |   |   |      |   |   |   |   |

| pushq <b>rA</b>     | A (        | rA E    | 7        |   |   |      |   |   |   |   |

| popq rA             | В (        | rA E    | <u>.</u> |   |   |      |   |   |   |   |

### Y86-64 Instruction Set

| Byte             | 0          | 1                    | 2 | 3 | 4                                      | 5    | 6 | 7  | 8   | 9   |

|------------------|------------|----------------------|---|---|----------------------------------------|------|---|----|-----|-----|

| halt             | 0 0        |                      |   |   |                                        |      |   |    |     |     |

| nop              | 1 (        | )                    |   |   |                                        |      |   |    |     |     |

| cmovXX rA, rB    | 2 <b>f</b> | <mark>n</mark> rA rB |   |   |                                        |      |   |    |     |     |

| irmovq V, rB     | 3 (        | ) F rB               |   |   |                                        |      | V |    |     |     |

| rmmovq rA, D(rB) | 4 (        | rA rB                |   |   |                                        |      | D | (  |     |     |

| mrmovq D(rB), rA | 5 (        | rA rB                |   |   |                                        |      | D | a  | ddq | 6 0 |

| OPq rA, rB       | 6 fi       | n rA rB              |   |   | ************************************** |      |   | s  | ubq | 6 1 |

| jxx <b>Dest</b>  | 7 fi       | n                    |   |   | C                                      | Dest |   | a  | ndq | 6 2 |

| call <b>Dest</b> | 8 (        | )                    |   |   | C                                      | )est |   | (x | orq | 6 3 |

| ret              | 9 (        | )                    |   |   |                                        |      |   |    |     |     |

| pushq <b>rA</b>  | A (        | rA F                 |   |   |                                        |      |   |    |     |     |

| popq <b>rA</b>   | В (        | rA F                 |   |   |                                        |      |   |    |     |     |

### Y86-64 Instruction Set

### **Encoding Registers**

#### Each register has 4-bit ID

- Same encoding as in x86-64

- Register ID 15 (0xF) indicates "no register"

- Will use this in our hardware design in multiple places

| % <b>rax</b>  | 0 | %r8          | 8   |

|---------------|---|--------------|-----|

| %rcx          | 1 | 8 <b>r9</b>  | 9   |

| %rdx          | 2 | 8 <b>r10</b> | A   |

| %rbx          | 3 | 8 <b>r11</b> | В   |

| %rsp          | 4 | 8 <b>r12</b> | С   |

| %rbp          | 5 | 8 <b>r13</b> | D   |

| % <b>rs</b> i | 6 | 8 <b>r14</b> | Е   |

| %rdi          | 7 | No Registe   | r F |

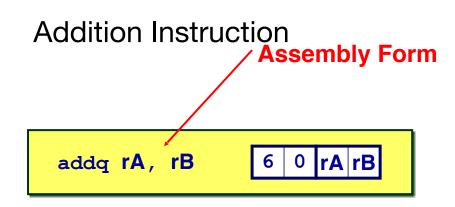

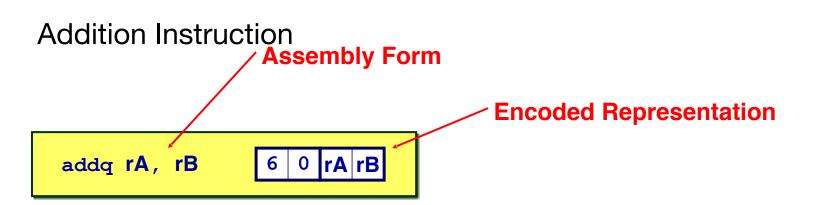

# Instruction Example

**Addition Instruction**

- Add value in register rA to that in register rB

- Store result in register rB

- Note that Y86-64 only allows addition to be applied to register data

- Set condition codes based on result

- e.g., addq %rax, %rsi Encoding: 60 06

- Two-byte encoding

- First indicates instruction type

- Second gives source and destination registers

# Instruction Example

- Add value in register rA to that in register rB

- Store result in register rB

- Note that Y86-64 only allows addition to be applied to register data

- Set condition codes based on result

- e.g., addq %rax, %rsi Encoding: 60 06

- Two-byte encoding

- First indicates instruction type

- Second gives source and destination registers

# Instruction Example

- Add value in register rA to that in register rB

- Store result in register rB

- Note that Y86-64 only allows addition to be applied to register data

- Set condition codes based on result

- e.g., addq %rax, %rsi Encoding: 60 06

- Two-byte encoding

- First indicates instruction type

- Second gives source and destination registers

# **Arithmetic and Logical Operations**

Add

addq rA, rB 6 0 rA rB

Subtract (rA from rB)

subq rA, rB 6 1 rA rB

#### And

andq rA, rB 6 2 rA rB

#### **Exclusive-Or**

xorq rA, rB 6 3 rA rB

- Refer to generically as "OPq"

- Encodings differ only by "function code"

- Low-order 4 bytes in first instruction

word

- Set condition codes as side effect

# **Arithmetic and Logical Operations**

#### Function Code

#### Subtract (rA from rB)

subq rA, rB 6 1 rA rB

#### And

andq rA, rB 6 2 rA rB

#### **Exclusive-Or**

xorq rA, rB 6 3 rA rB

- Refer to generically as "OPq"

- Encodings differ only by "function code"

- Low-order 4 bytes in first instruction

word

- Set condition codes as side effect

# **Arithmetic and Logical Operations**

Subtract (rA from rB)

subq rA, rB 6 1 rA rB

#### And

andq rA, rB 6 2 rA rB

#### **Exclusive-Or**

xorq rA, rB 6 3 rA rB

- Refer to generically as "OPq"

- Encodings differ only by "function code"

- Low-order 4 bytes in first instruction

word

- Set condition codes as side effect

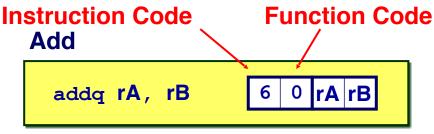

### **Move Operations**

#### **Register** → **Register**

- Like the x86-64 movq instruction

- Simpler format for memory addresses

- Give different names to keep them distinct

## **Jump Instructions**

#### **Jump Unconditionally**

| eunp encen           |                  |      |

|----------------------|------------------|------|

| jmp <b>Dest</b>      | 7 0              | Dest |

| Jump When            | Less or Equal    |      |

| jle <b>Dest</b>      | 7 1              | Dest |

| Jump When            | Less             |      |

| jl Dest              | 7 2              | Dest |

| Jump When            | Equal            |      |

| je <b>Dest</b>       | 7 3              | Dest |

| Jump When            | Not Equal        |      |

| jne <b>Dest</b>      | 7 4              | Dest |

| Jump When            | Greater or Equal |      |

| jge <b>Dest</b>      | 7 5              | Dest |

| Jump When            | Greater          |      |

| jg <mark>Dest</mark> | 7 6              | Dest |

|                      |                  |      |

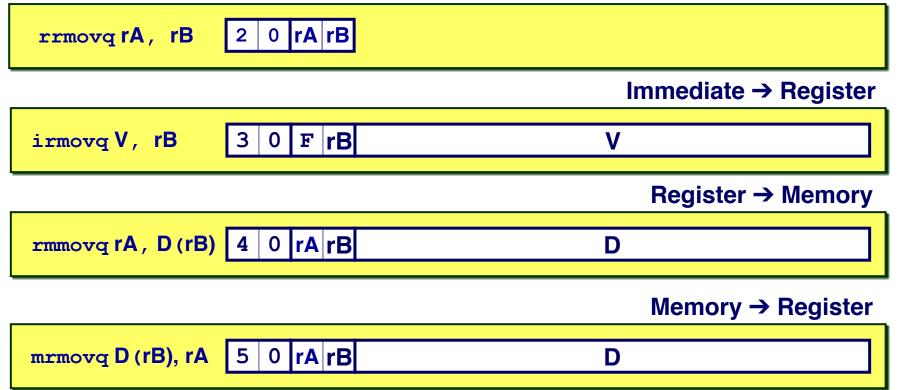

## **Stack Operations**

- Decrement %rsp by 8

- Store word from rA to memory at %rsp

- Like x86-64

- Read word from memory at %rsp

- Save in rA

- Increment %rsp by 8

- Like x86-64

## **Subroutine Call and Return**

- Push address of next instruction onto stack

- Start executing instructions at Dest

- Like x86-64

- Pop value from stack

- Use as address for next instruction

- Like x86-64

## **Miscellaneous Instructions**

Don't do anything

- Stop executing instructions

- x86-64 has comparable instruction, but can't execute it in user mode

- We will use it to stop the simulator

- Encoding ensures that program hitting memory initialized to zero will halt

# **Status Conditions**

| Mnemonic        | Code      |

|-----------------|-----------|

| AOK             | 1         |

| Mnemonic        | Code      |

| HLT             | 2         |

|                 |           |

| Mnemonic        | Code      |

| Mnemonic<br>ADR | Code<br>3 |

|                 |           |

- Normal operation

- Halt instruction encountered

- Bad address (either instruction or data) encountered

- Invalid instruction encountered

- Desired Behavior

- If AOK, keep going

- Otherwise, stop program execution

## How Does An Assemble Work?

- Translates assembly code to binary-encode

- Reads assembly program line by line, and translates according to the instruction format defined by an ISA

#### Add

- It sometimes needs to make two passes on the assembly program to resolve forward references

- E.g., forward branch target address

#### Jump Unconditionally

## **Today: Processor Microarchitecture**

- The Y86-64 ISA: Simplified version of x86-64

- How an assembler works

- Sequential, single-cycle microarchitecture implementation

- Basic idea

- Hardware implementation

### **Basic Principles for a Sequential Implementation**

#### **Principles**:

- Execute each instruction one at a time, one after another

- Express every instruction as series of simple steps

- Dedicated hardware structure for completing each step

- Follow same general flow for each instruction type

Fetch: Read instruction from instruction memory Decode: Read program registers Execute: Compute value or address Memory: Read or write data Write Back: Write program registers PC: Update program counter

# **Executing Arith./Logical Operation**

OPq rA, rB 6 fn rA rB

#### Fetch

Read 2 bytes

#### Decode

Read operand registers

#### Execute

- Perform operation

- Set condition codes

#### Memory

Do nothing

#### Write back

Update register

#### **PC Update**

Increment PC by 2

OPq rA, rB 6 fn rA rB

OPq rA, rB

|       | OPq rA, rB 6                                                                  | fn <b>rA rB</b>                             |

|-------|-------------------------------------------------------------------------------|---------------------------------------------|

| Fetch | OPq rA, rB<br>icode:ifun $\leftarrow M_1[PC]$<br>rA:rB $\leftarrow M_1[PC+1]$ | Read instruction byte<br>Read register byte |

|       | valP ← PC+2                                                                   | Compute next PC                             |

| OPq <b>rA, rB</b> |  |

|-------------------|--|

|-------------------|--|

6 fn **rA rB**

|        | OPq rA, rB                       |                       |

|--------|----------------------------------|-----------------------|

|        | icode:ifun ← M <sub>1</sub> [PC] | Read instruction byte |

| Fetch  | rA:rB ← M <sub>1</sub> [PC+1]    | Read register byte    |

|        | valP ← PC+2                      | Compute next PC       |

| Decode | valA ← R[rA]                     | Read operand A        |

| Decode | valB ← R[rB]                     | Read operand B        |

OPq rA, rB

6 fn **rA rB**

|         | OPq rA, rB                       |   |

|---------|----------------------------------|---|

|         | icode:ifun ← M <sub>1</sub> [PC] | R |

| Fetch   | rA:rB ← M <sub>1</sub> [PC+1]    | R |

|         | valP ← PC+2                      | C |

| Decode  | valA ← R[rA]                     | R |

| Decode  | valB ← R[rB]                     | R |

| Evenute | valE ← valB OP valA              | Р |

| Execute | Set CC                           | S |

Read instruction byte Read register byte

Compute next PC Read operand A Read operand B Perform ALU operation Set condition code register

OPq rA, rB

6 fn **rA rB**

|         | OPq rA, rB                                                                                |

|---------|-------------------------------------------------------------------------------------------|

| Fetch   | icode:ifun $\leftarrow M_1[PC]$<br>rA:rB $\leftarrow M_1[PC+1]$<br>valP $\leftarrow PC+2$ |

| Decode  | valA ← R[rA]<br>valB ← R[rB]                                                              |

| Execute | valE ← valB OP valA<br>Set CC                                                             |

| Memory  |                                                                                           |

Read instruction byte Read register byte

Compute next PC Read operand A Read operand B Perform ALU operation Set condition code register

OPq rA, rB

6 fn **rA rB**

| OPq rA, rB                    |                                                                                                                                                                                             |

|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| icode:ifun ← M₁[PC]           | Rea                                                                                                                                                                                         |

| rA:rB ← M <sub>1</sub> [PC+1] | Rea                                                                                                                                                                                         |

| valP ← PC+2                   | Con                                                                                                                                                                                         |

| valA ← R[rA]                  | Rea                                                                                                                                                                                         |

| valB ← R[rB]                  | Rea                                                                                                                                                                                         |

| valE ← valB OP valA           | Perf                                                                                                                                                                                        |

| Set CC                        | Set                                                                                                                                                                                         |

|                               |                                                                                                                                                                                             |

| R[rB] ← valE                  | Writ                                                                                                                                                                                        |

|                               |                                                                                                                                                                                             |

|                               | icode:ifun $\leftarrow M_1[PC]$<br>rA:rB $\leftarrow M_1[PC+1]$<br>valP $\leftarrow PC+2$<br>valA $\leftarrow R[rA]$<br>valB $\leftarrow R[rB]$<br>valE $\leftarrow$ valB OP valA<br>Set CC |

Read instruction byte Read register byte

Compute next PC Read operand A Read operand B Perform ALU operation Set condition code register

Write back result

OPq rA, rB

6 fn rA rB

|           | OPq rA, rB                       |                             |

|-----------|----------------------------------|-----------------------------|

| Fetch     | icode:ifun ← M <sub>1</sub> [PC] | Read instruction byte       |

|           | rA:rB ← M <sub>1</sub> [PC+1]    | Read register byte          |

|           | valP ← PC+2                      | Compute next PC             |

| Decode    | valA ← R[rA]                     | Read operand A              |

|           | valB ← R[rB]                     | Read operand B              |

| Execute   | valE ← valB OP valA              | Perform ALU operation       |

|           | Set CC                           | Set condition code register |

| Memory    |                                  |                             |

| Write     | R[rB] ← valE                     | Write back result           |

| back      |                                  |                             |

| PC update | PC ← valP                        | Update PC                   |

## Executing rmmovq

rmmovq rA, D(rB) 4 0 rA rB

D

#### Fetch

Read 10 bytes

#### Decode

Read operand registers

#### Execute

Compute effective address: R[rB] + D

#### Memory

Write R[rA] to to memory at address R[rB] + D

#### Write back

Do nothing

#### **PC Update**

Increment PC by 10

### Stage Computation: rmmovq

rmmovq rA, D(rB) 4 0 rA rB

D

rmmovq rA, D(rB)

### Stage Computation: rmmovq

rmmovq rA, D(rB) 4 0 rA rB

D

|       | rmmovq rA, D(rB)                                              |  |

|-------|---------------------------------------------------------------|--|

|       | icode:ifun ← M <sub>1</sub> [PC]                              |  |

| Fetch | rA:rB ← M <sub>1</sub> [PC+1]<br>valC ← M <sub>8</sub> [PC+2] |  |

| FEIGH | valC ← M <sub>8</sub> [PC+2]                                  |  |

|       | valP ← PC+10                                                  |  |

Read instruction byte Read register byte Read displacement D Compute next PC

rmmovq rA, D(rB) 4

0 **rA rB**

D

|        | rmmovq rA, D(rB)              |

|--------|-------------------------------|

| Fetch  | icode:ifun ← M₁[PC]           |

|        | rA:rB ← M <sub>1</sub> [PC+1] |

|        | valC ← M <sub>8</sub> [PC+2]  |

|        | valP ← PC+10                  |

| Decode | valA ← R[rA]                  |

|        | valB ← R[rB]                  |

Read instruction byte Read register byte Read displacement D Compute next PC Read operand A Read operand B

rmmovq rA, D(rB) 4

0 **rA rB**

D

|         | rmmovq rA, D(rB)              |

|---------|-------------------------------|

| Fetch   | icode:ifun ← M₁[PC]           |

|         | rA:rB ← M <sub>1</sub> [PC+1] |

|         | valC ← M <sub>8</sub> [PC+2]  |

|         | valP ← PC+10                  |

| Decode  | valA ← R[rA]                  |

|         | valB ← R[rB]                  |

| Execute | valE ← valB + valC            |

|         |                               |

Read instruction byte Read register byte Read displacement D Compute next PC Read operand A Read operand B Compute effective address

rmmovq rA, D(rB)

4 0 rA rB

D

|         | rmmovq rA, D(rB)             |

|---------|------------------------------|

| Fetch   | icode:ifun ← M₁[PC]          |

|         | rA:rB ← M₁[PC+1]             |

|         | valC ← M <sub>8</sub> [PC+2] |

|         | valP ← PC+10                 |

| Decode  | valA ← R[rA]                 |

|         | valB ← R[rB]                 |

| Execute | valE ← valB + valC           |

| Memory  | M <sub>8</sub> [valE] ← valA |

Read instruction byte Read register byte Read displacement D Compute next PC Read operand A Read operand B Compute effective address

Write value to memory

rmmovq rA, D(rB) 4

0 **rA rB**

D

|         | rmmovq rA, D(rB)              |

|---------|-------------------------------|

| Fetch   | icode:ifun ← M₁[PC]           |

|         | rA:rB ← M <sub>1</sub> [PC+1] |

|         | valC ← M <sub>8</sub> [PC+2]  |

|         | valP ← PC+10                  |

| Decode  | valA ← R[rA]                  |

|         | valB ← R[rB]                  |

| Execute | valE ← valB + valC            |

|         |                               |

| Memory  | M <sub>8</sub> [valE] ← valA  |

| Write   |                               |

| back    |                               |

Read instruction byte Read register byte Read displacement D Compute next PC Read operand A Read operand B Compute effective address

Write value to memory

rmmovq rA, D(rB) 4

0 rA rB

D

|           | rmmovq rA, D(rB)                 |

|-----------|----------------------------------|

| Fetch     | icode:ifun ← M <sub>1</sub> [PC] |

|           | rA:rB ← M <sub>1</sub> [PC+1]    |

|           | valC ← M <sub>8</sub> [PC+2]     |

|           | valP ← PC+10                     |

| Decode    | valA ← R[rA]                     |

|           | valB ← R[rB]                     |

| Execute   | valE ← valB + valC               |

| Memory    | M <sub>8</sub> [valE] ← valA     |

| Write     |                                  |

| back      |                                  |

| PC update | PC ← valP                        |

Read instruction byte Read register byte Read displacement D Compute next PC Read operand A Read operand B Compute effective address

Write value to memory

**Update PC**

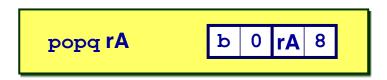

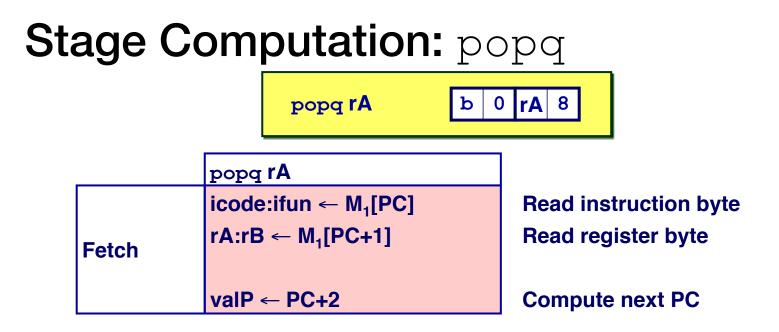

# Executing popq

#### Fetch

Read 2 bytes

#### Decode

Read stack pointer (%rsp)

#### Execute

Increment stack pointer by 8

#### Memory

Read from the top of the stack from memory

#### Write back

- Update stack pointer

- Write result to register

#### **PC Update**

Increment PC by 2

popq rA

0 **rA** 8 b

| popq <b>rA</b> |  |

|----------------|--|

|----------------|--|

icode:ifun ← M<sub>1</sub>[PC] **Fetch**

Decode

$rA:rB \leftarrow M_1[PC+1]$

valP ← PC+2

$valA \leftarrow R[\$rsp]$

valB ← R[%rsp]

**Read instruction byte Read register byte**

**Compute next PC Read stack pointer Read stack pointer**

popq rA

b 0 **rA** 8

popq rA

icode:ifun ← M<sub>1</sub>[PC] **rA:rB** ← M<sub>1</sub>[PC+1] **Fetch**

Decode

Execute

valP  $\leftarrow$  PC+2

$valA \leftarrow R[\$rsp]$

valB ← R[%rsp]

$valE \leftarrow valB + 8$

**Read instruction byte Read register byte**

**Compute next PC Read stack pointer Read stack pointer Increment stack pointer**

popq rA

0 **rA** 8 b

| popq rA |

|---------|

|---------|

icode:ifun ← M<sub>1</sub>[PC]

**Fetch**

Decode

Execute

Memory

**rA:rB** ← M<sub>1</sub>[PC+1]

valP  $\leftarrow$  PC+2

$valA \leftarrow R[\$rsp]$

$valB \leftarrow R[\$rsp]$

$valE \leftarrow valB + 8$

valM  $\leftarrow$  M<sub>8</sub>[valA]

**Read instruction byte Read register byte**

**Compute next PC Read stack pointer Read stack pointer Increment stack pointer**

**Read from stack**

popq rA

b 0 **rA** 8

Fetch

Execute

Memory

Write

back

icode:ifun  $\leftarrow M_1[PC]$ rA:rB  $\leftarrow M_1[PC+1]$

valP ← PC+2 Decode valA ← R[%rsp]

$valB \leftarrow R[\$rsp]$

$valE \leftarrow valB + 8$

valM  $\leftarrow$  M<sub>8</sub>[valA]

$R[\$rsp] \leftarrow valE$

$R[rA] \leftarrow valM$

Read instruction byte Read register byte

Compute next PC Read stack pointer Read stack pointer Increment stack pointer

Read from stack Update stack pointer Write back result

popq rA

b 0 **rA** 8

icode:ifun ← M<sub>1</sub>[PC] **rA:rB** ← M<sub>1</sub>[PC+1] **Fetch**

Decode

Execute

Memory

PC update

Write

back

$valA \leftarrow R[\$rsp]$

$valB \leftarrow R[\$rsp]$

$valE \leftarrow valB + 8$

valM  $\leftarrow$  M<sub>8</sub>[valA]

$R[\$rsp] \leftarrow valE$

$R[rA] \leftarrow valM$

PC ← valP

valP  $\leftarrow$  PC+2

**Read instruction byte Read register byte**

**Compute next PC Read stack pointer Read stack pointer Increment stack pointer**

**Read from stack** Update stack pointer Write back result **Update PC**

popq rA

0 **rA** 8 b

| popq | rA |

|------|----|

|      |    |

icode:ifun ← M<sub>1</sub>[PC]  $rA:rB \leftarrow M_1[PC+1]$

**Fetch**

Decode

Execute

Memory

PC update

Write

back

$valA \leftarrow R[\$rsp]$

$valB \leftarrow R[\$rsp]$

$valE \leftarrow valB + 8$

valM  $\leftarrow$  M<sub>8</sub>[valA]

$R[\$rsp] \leftarrow valE$

$R[rA] \leftarrow valM$

PC ← valP

valP  $\leftarrow$  PC+2

**Read register byte**

**Compute next PC Read stack pointer Read stack pointer Increment stack pointer**

**Read instruction byte**

**Read from stack** Update stack pointer Write back result **Update PC**

• Must update two registers (Register file must have two write ports)

Popped value and New stack pointer

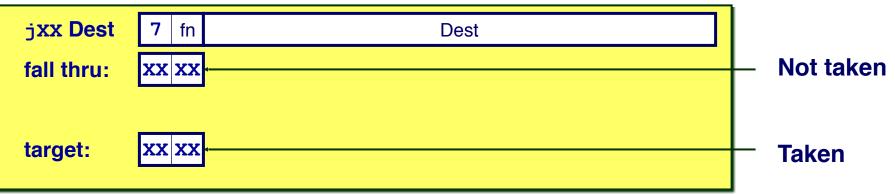

# **Executing Jumps**

#### Fetch

- Read 9 bytes

- Increment PC by 9

#### Decode

Do nothing

#### Execute

Determine whether to take branch based on jump condition and condition codes

#### Memory

Do nothing

#### Write back

Do nothing

#### **PC Update**

Set PC to Dest if branch taken or to incremented PC if not branch

jXX Dest

- Compute both addresses

- Choose based on setting of condition codes and branch condition

|       | jXX Dest                                    |

|-------|---------------------------------------------|

|       | icode:ifun ← M <sub>1</sub> [PC]            |

| Fetch | valC ← M <sub>8</sub> [PC+1]<br>valP ← PC+9 |

**Read instruction byte**

Read destination address Fall through address

- Compute both addresses

- Choose based on setting of condition codes and branch condition

|        | jXX Dest                                                                                 |

|--------|------------------------------------------------------------------------------------------|

| Fetch  | icode:ifun $\leftarrow M_1[PC]$<br>valC $\leftarrow M_8[PC+1]$<br>valP $\leftarrow PC+9$ |

| Decode |                                                                                          |

**Read instruction byte**

Read destination address Fall through address

- Compute both addresses

- Choose based on setting of condition codes and branch condition

|         | jXX Dest                                    |                                                  |

|---------|---------------------------------------------|--------------------------------------------------|

|         | icode:ifun ← M <sub>1</sub> [PC]            | Read instruction byte                            |

| Fetch   | valC ← M <sub>8</sub> [PC+1]<br>valP ← PC+9 | Read destination address<br>Fall through address |

| Decode  |                                             |                                                  |

| Execute | Cnd ← Cond(CC,ifun)                         | Take branch?                                     |

- Compute both addresses

- Choose based on setting of condition codes and branch condition

|         | jXX Dest                                    |                                                  |

|---------|---------------------------------------------|--------------------------------------------------|

|         | icode:ifun ← M <sub>1</sub> [PC]            | Read instruction byte                            |

| Fetch   | valC ← M <sub>8</sub> [PC+1]<br>valP ← PC+9 | Read destination address<br>Fall through address |

| Decode  |                                             |                                                  |

| Execute | Cnd ← Cond(CC,ifun)                         | Take branch?                                     |

| Memory  |                                             |                                                  |

- Compute both addresses

- Choose based on setting of condition codes and branch condition

|         | jXX Dest                         |                          |

|---------|----------------------------------|--------------------------|

|         | icode:ifun ← M <sub>1</sub> [PC] | Read instruction byte    |

| Fetch   | valC ← M <sub>8</sub> [PC+1]     | Read destination address |

|         |                                  | neau destination address |

|         | valP ← PC+9                      | Fall through address     |

| Decode  |                                  |                          |

| Execute | Cnd ← Cond(CC,ifun)              | Take branch?             |

| Memory  |                                  |                          |

| Write   |                                  |                          |

| back    |                                  |                          |

- Compute both addresses

- Choose based on setting of condition codes and branch condition

|           | jXX Dest                         |                          |

|-----------|----------------------------------|--------------------------|

|           | icode:ifun ← M <sub>1</sub> [PC] | Read instruction byte    |

| Fetch     |                                  |                          |

|           | valC ← M <sub>8</sub> [PC+1]     | Read destination address |

|           | valP ← PC+9                      | Fall through address     |

| Decode    |                                  |                          |

| Execute   | Cnd ← Cond(CC,ifun)              | Take branch?             |

| Memory    |                                  |                          |

| Write     |                                  |                          |

| back      |                                  |                          |

| PC update | PC ← Cnd ? valC : valP           | Update PC                |

- Compute both addresses

- Choose based on setting of condition codes and branch condition

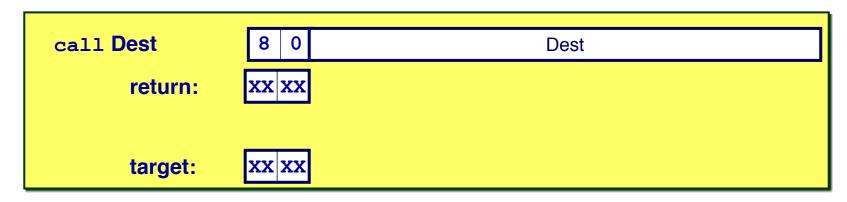

# **Executing** call

#### Fetch

- Read 9 bytes

- Increment PC by 9 (return address)

#### Decode

Read stack pointer (%rsp)

#### Execute

Decrement stack pointer by 8

#### Memory

Write incremented PC (i.e., return address) to top of the stack in the memory

#### Write back

Update stack pointer

#### **PC Update**

Set PC to Dest

call Dest

|       | call <b>Dest</b>                            |        |

|-------|---------------------------------------------|--------|

|       | icode:ifun ← M <sub>1</sub> [PC]            | R      |

| Fetch | valC ← M <sub>8</sub> [PC+1]<br>valP ← PC+9 | R<br>C |

**Read instruction byte**

Read destination address Compute return point

|        | call <b>Dest</b>                                                                         |

|--------|------------------------------------------------------------------------------------------|

| Fetch  | icode:ifun $\leftarrow M_1[PC]$<br>valC $\leftarrow M_8[PC+1]$<br>valP $\leftarrow PC+9$ |

| Decode | valB ← R[%rsp]                                                                           |

**Read instruction byte**

Read destination address Compute return point

**Read stack pointer**

|         | call <b>Dest</b>                                                                         |

|---------|------------------------------------------------------------------------------------------|

| Fetch   | icode:ifun $\leftarrow M_1[PC]$<br>valC $\leftarrow M_8[PC+1]$<br>valP $\leftarrow PC+9$ |

| Decode  | valB ← R[%rsp]                                                                           |

| Execute | valE ← valB + –8                                                                         |

**Read instruction byte**

Read destination address Compute return point

Read stack pointer Decrement stack pointer

|         | call Dest                                                                                |

|---------|------------------------------------------------------------------------------------------|

| Fetch   | icode:ifun $\leftarrow M_1[PC]$<br>valC $\leftarrow M_8[PC+1]$<br>valP $\leftarrow PC+9$ |

| Decode  | valB ← R[%rsp]                                                                           |

| Execute | valE ← valB + –8                                                                         |

| Memory  | M <sub>8</sub> [valE] ← valP                                                             |

**Read instruction byte**

Read destination address Compute return point

Read stack pointer Decrement stack pointer

Write return value on stack

|         | call <b>Dest</b>                                                                         |

|---------|------------------------------------------------------------------------------------------|

| Fetch   | icode:ifun $\leftarrow M_1[PC]$<br>valC $\leftarrow M_8[PC+1]$<br>valP $\leftarrow PC+9$ |

| Decode  | valB ← R[%rsp]                                                                           |

| Execute | valE ← valB + –8                                                                         |

| Memory  | M <sub>8</sub> [valE] ← valP                                                             |

| Write   | R[%rsp] ← valE                                                                           |

| back    |                                                                                          |

**Read instruction byte**

Read destination address Compute return point

Read stack pointer Decrement stack pointer

Write return value on stack Update stack pointer

|           | call <b>Dest</b>                                                                         |

|-----------|------------------------------------------------------------------------------------------|

| Fetch     | icode:ifun $\leftarrow M_1[PC]$<br>valC $\leftarrow M_8[PC+1]$<br>valP $\leftarrow PC+9$ |

| Decode    | valB ← R[%rsp]                                                                           |

| Execute   | valE ← valB + –8                                                                         |

| Memory    | M <sub>8</sub> [valE] ← valP                                                             |

| Write     | R[%rsp] ← valE                                                                           |

| back      |                                                                                          |

| PC update | PC ← valC                                                                                |

**Read instruction byte**

Read destination address Compute return point

Read stack pointer Decrement stack pointer

Write return value on stack Update stack pointer

Set PC to destination

# **Today: Processor Microarchitecture**

- The Y86-64 ISA: Simplified version of x86-64

- How an assembler works

- Sequential, single-cycle microarchitecture implementation

- Basic idea

- Hardware implementation

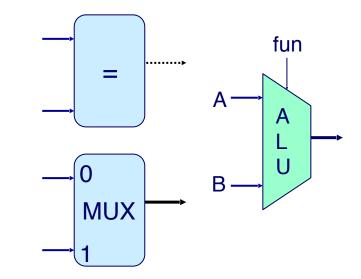

# **Building Blocks**

#### **Combinational Logic**

- Compute Boolean functions of inputs

- Continuously respond to input changes

- Operate on data and implement control

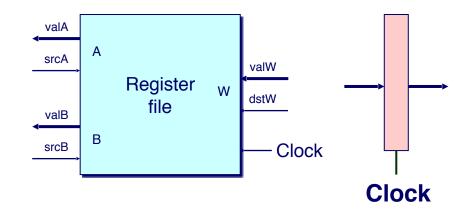

#### **Storage Elements**

- Store bits

- Addressable memories

- Non-addressable registers

- Loaded only as clock rises

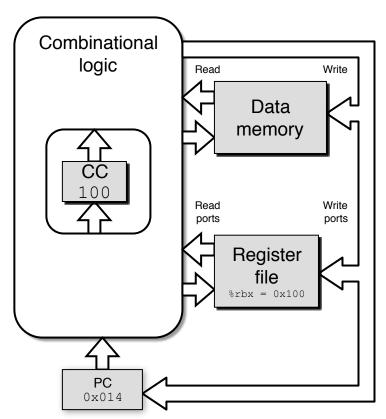

# **Microarchitecture Overview**

#### Storage (All updated as clock rises)

- PC register

- Cond. Code register

- Data memory

- Register file

#### **Combinational Logic**

- ALU

- Control logic

- Memory reads

- Instruction memory

- Register file

- Data memory