# CSC 252: Computer Organization Spring 2020: Lecture 16

Instructor: Yuhao Zhu

Department of Computer Science University of Rochester

#### Announcements

- By default 252/452 will be pass/fail

- 4/10 is the deadline to opt-out and request a letter grade

- Mid-term solution has been posted

- Mid-term grades will be posted this weekend

- Lectures will be recorded and posted online

- Office hours will be held through Zoom; links on the website

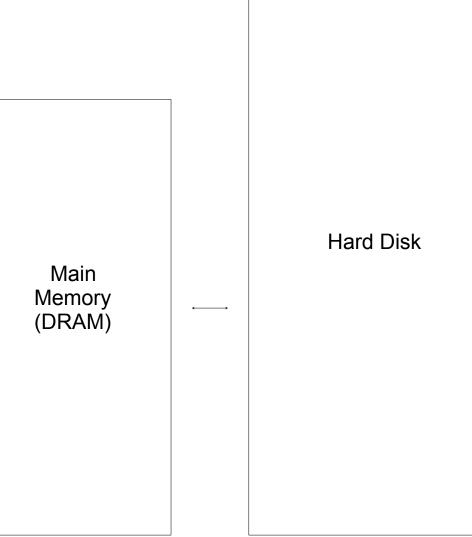

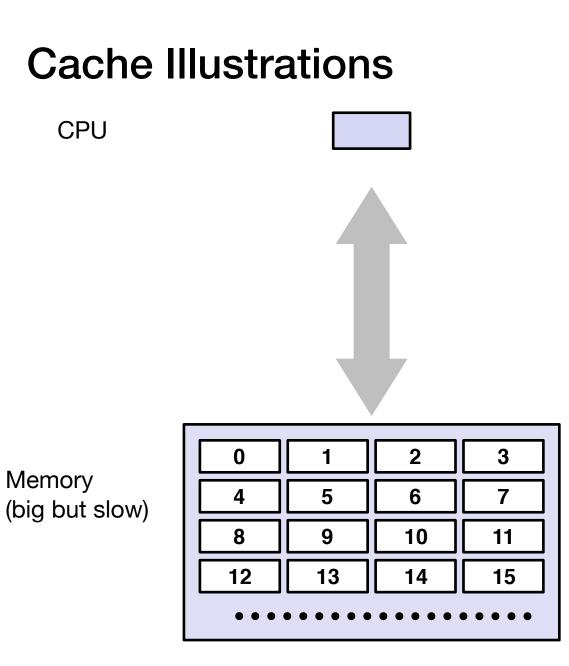

### The Problem

#### • Bigger is slower

- Flip-flops/Small SRAM, sub-nanosec

- SRAM, KByte~MByte, ~nanosec

- DRAM, Gigabyte, ~50 nanosec

- Hard Disk, Terabyte, ~10 millisec

- Faster is more expensive (dollars and chip area)

- SRAM, < 10\$ per Megabyte

- DRAM, < 1\$ per Megabyte

- Hard Disk < 1\$ per Gigabyte

- Other technologies have their place as well

- PC-RAM, MRAM, RRAM

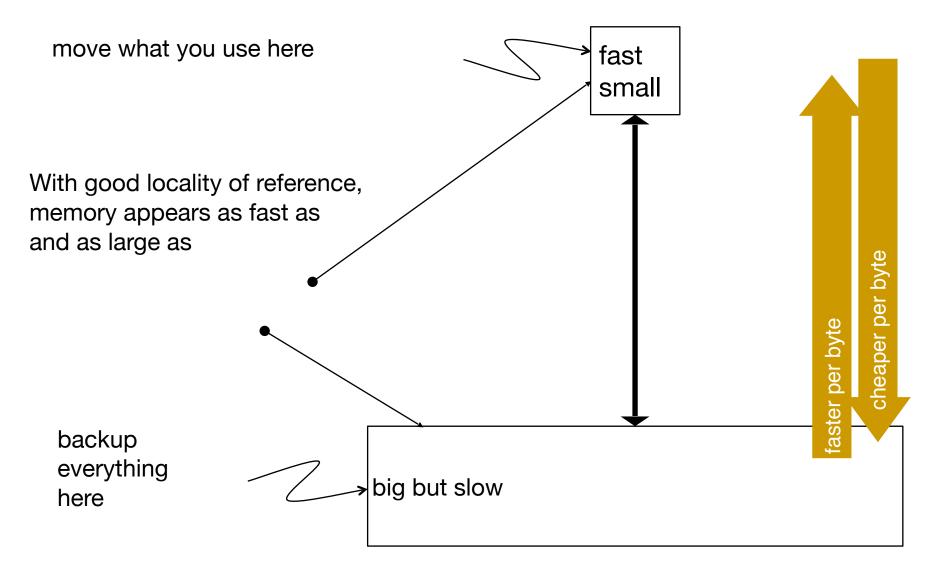

#### We want both fast and large Memory

- But we cannot achieve both with a single level of memory

- Idea: Memory Hierarchy

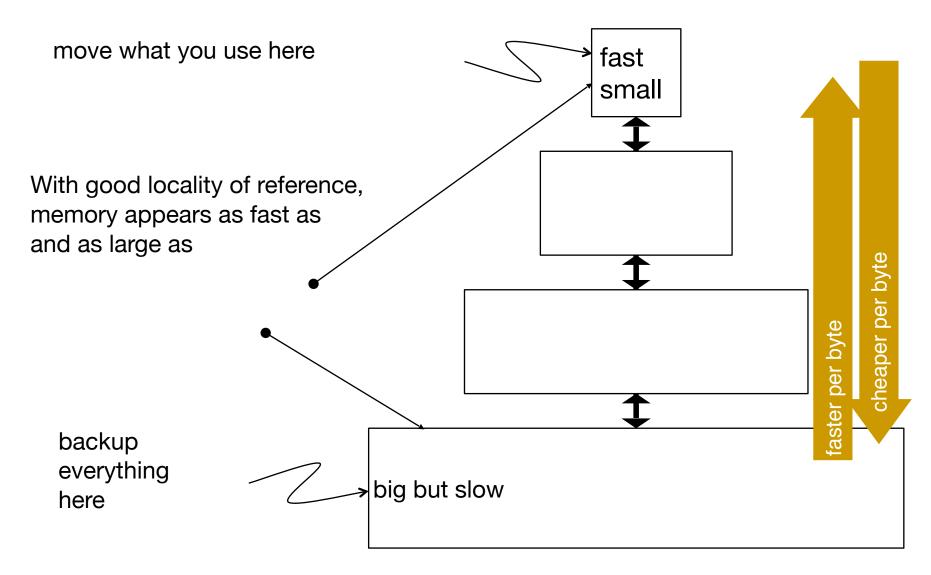

- Have multiple levels of storage (progressively bigger and slower as the levels are farther from the processor)

- ensure most of the data the processor needs in the near future is kept in the fast(er) level(s)

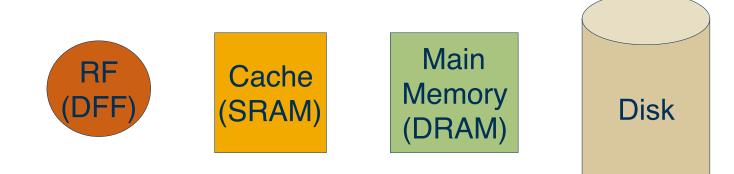

### **Memory Hierarchy**

### **Memory Hierarchy**

### **Memory Hierarchy**

- Fundamental tradeoff

- Fast memory: small

- Large memory: slow

- Balance latency, cost, size, bandwidth

# The Bookshelf Analogy

- Book in your hand

- Desk

- Bookshelf

- Boxes at home

- Boxes in storage

- Recently-used books tend to stay on desk

- Comp Org. books, books for classes you are currently taking

- Until the desk gets full

- Adjacent books in the shelf needed around the same time

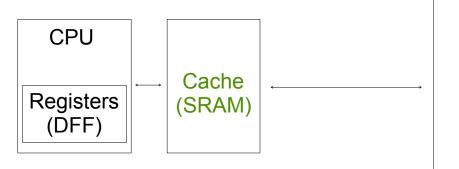

### A Modern Memory Hierarchy

Register File (DFF) 32 words, sub-nsec

L1 cache (SRAM)

~32 KB, ~nsec

L2 cache (SRAM) 512 KB ~ 1MB, many nsec

L3 cache (SRAM)

••••

Main memory (DRAM), GB, ~100 nsec

Hard Disk 100 GB, ~10 msec

#### **How Things Have Progressed**

| 1995 low-mid<br>range<br>Hennessy & Patterson, Computer<br>Arch., 1996       | 200B<br>5ns     | 64KB<br>10ns  | 32MB<br>100ns  | 2GB<br>5ms    |

|------------------------------------------------------------------------------|-----------------|---------------|----------------|---------------|

| 2009 low-mid<br>range<br>www.dell.com, \$449 including 17"<br>LCD flat panel | ~200B<br>0.33ns | 8MB<br>0.33ns | 4GB<br><100ns  | 750GB<br>4ms  |

| 2015<br>mid range                                                            | ~200B<br>0.33ns | 8MB<br>0.33ns | 16GB<br><100ns | 256GB<br>10us |

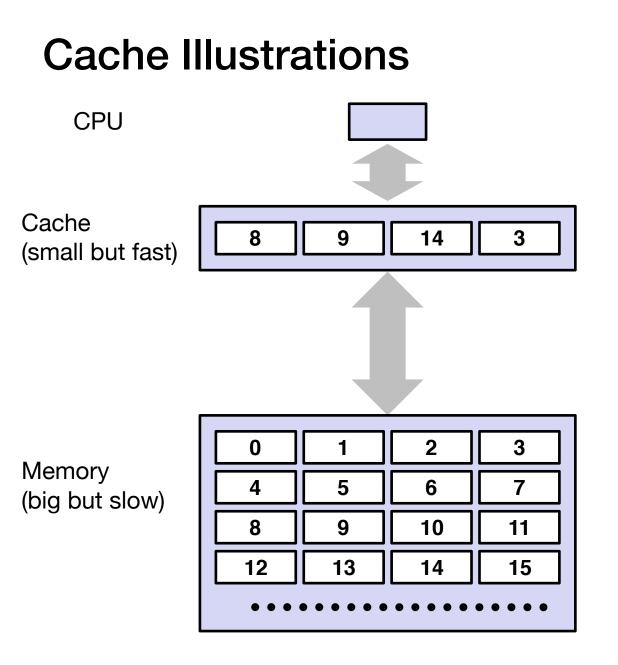

### How to Make Effective Use of the Hierarchy

- Fundamental question: how do we know what data to put in the fast and small memory?

- Answer: ensure most of the data the processor needs in the near future is kept in the fast(er) level(s)

- How do we know what data will be needed in the future?

- Do we know before the program runs?

- If so, programmers or compiler can place the right data at the right place

- Do we know only after the program runs?

- If so, only the hardware can effectively place the data

#### How to Make Effective Use of the Hierarchy

- Modern computers provide both ways

- Register file: programmers explicitly move data from the main memory (slow but big DRAM) to registers (small, very fast)

- movq (%rdi), %rdx

- Cache, on the other hand, is automatically managed by hardware

- Sits between registers and main memory, "invisible" to programmers

- The hardware automatically figures out what data will be used in the near future, and place in the cache.

- How does the hardware know that??

# Locality

• Principle of Locality: Programs tend to use data and instructions with addresses near or equal to those they have used recently

# Locality

- Principle of Locality: Programs tend to use data and instructions with addresses near or equal to those they have used recently

- Temporal locality:

- Recently referenced items are likely to be referenced again in the near future

# Locality

- Principle of Locality: Programs tend to use data and instructions with addresses near or equal to those they have used recently

- Temporal locality:

- Recently referenced items are likely to be referenced again in the near future

- Spatial locality:

- Items with nearby addresses tend to be referenced close together in time

#### Locality Example

sum = 0; for (i = 0; i < n; i++) sum += a[i]; return sum;

- Data references

- **Spatial** Locality: Reference array elements in succession (stride-1 reference pattern)

- **Temporal** Locality: Reference variable sum each iteration.

- Instruction references

- Spatial Locality: Reference instructions in sequence.

- Temporal Locality: Cycle through loop repeatedly.

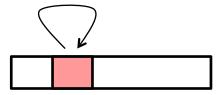

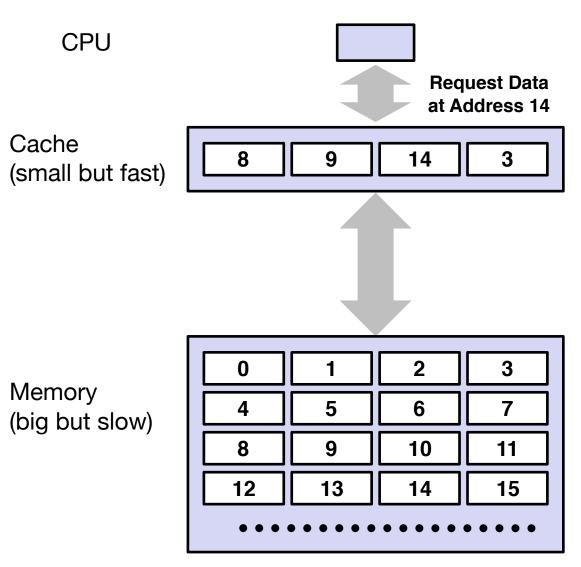

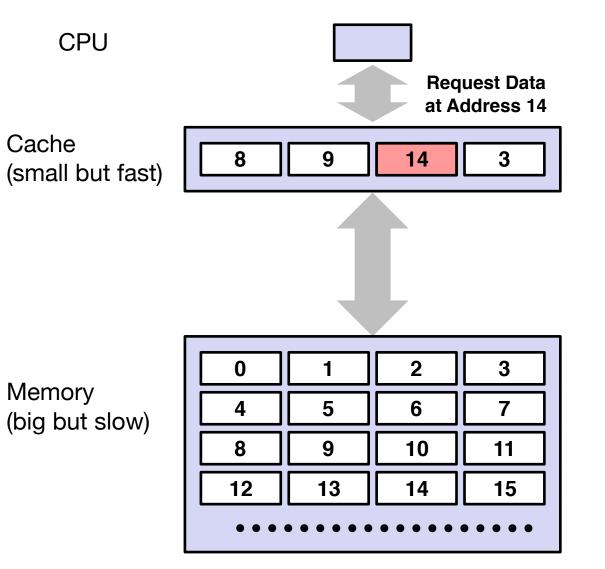

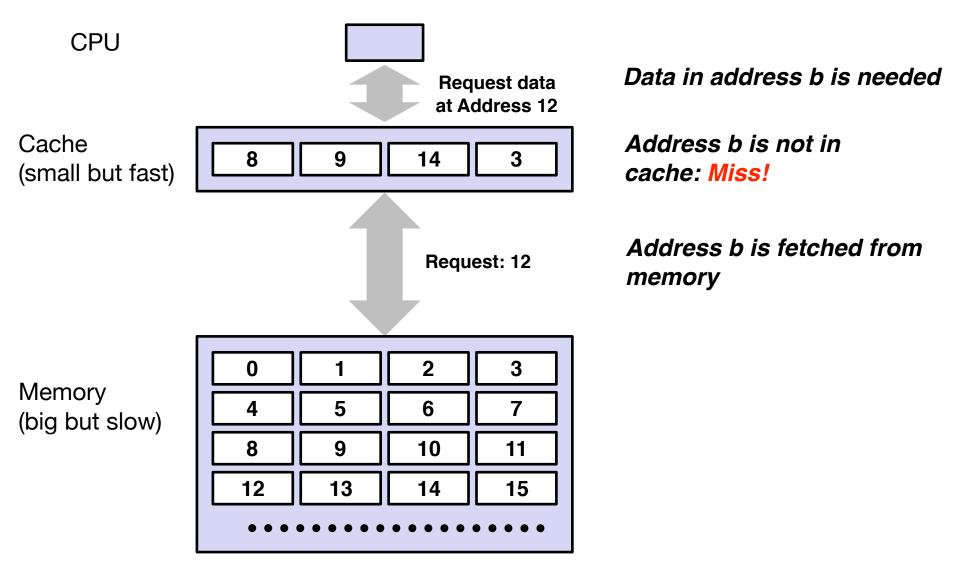

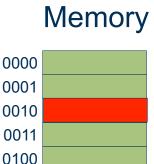

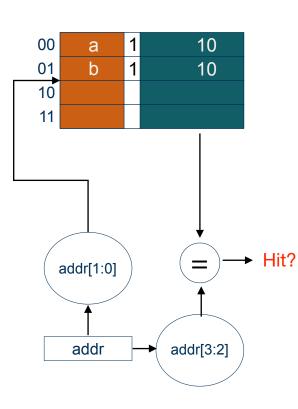

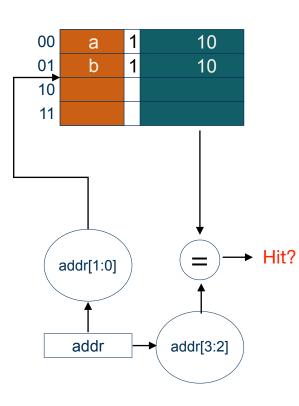

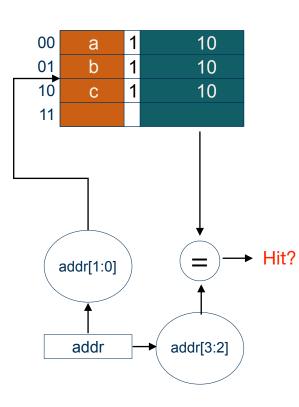

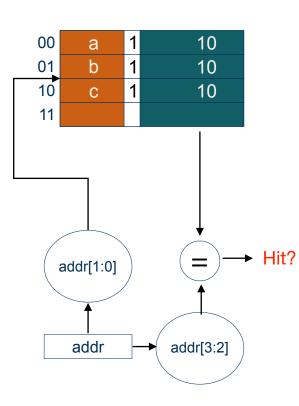

#### Data in address b is needed

Data in address b is needed

Address b is in cache: Hit!

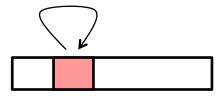

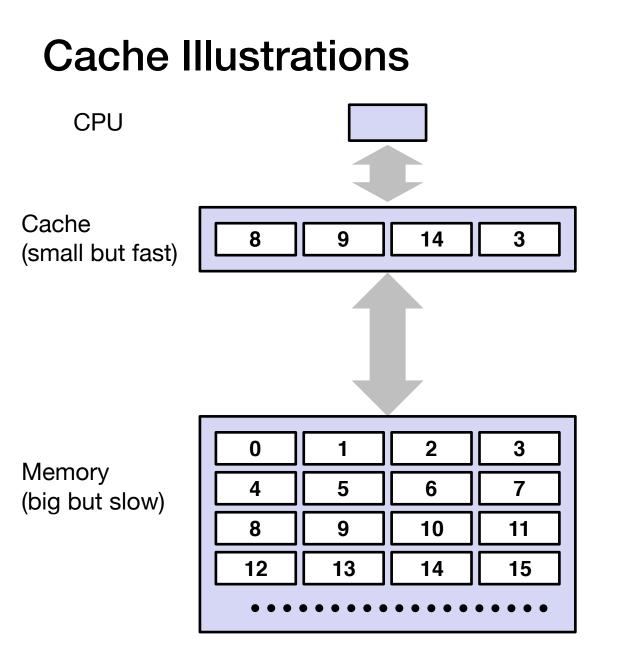

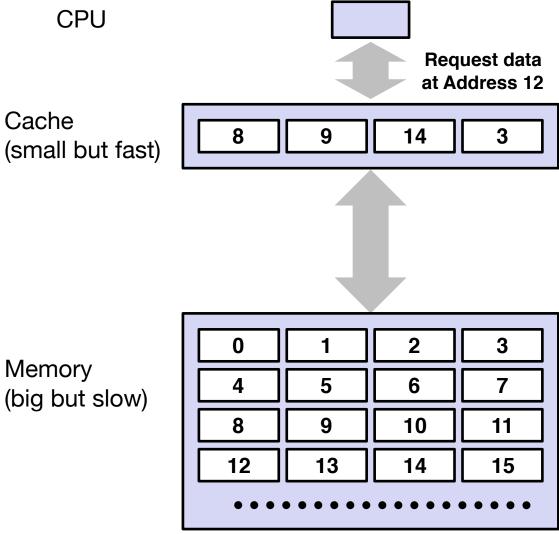

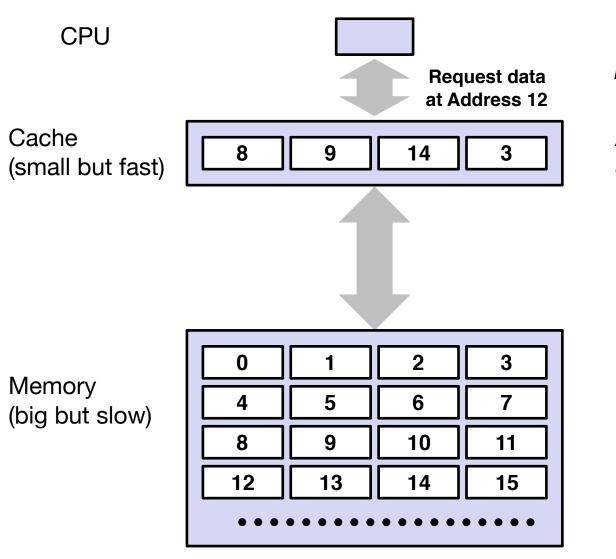

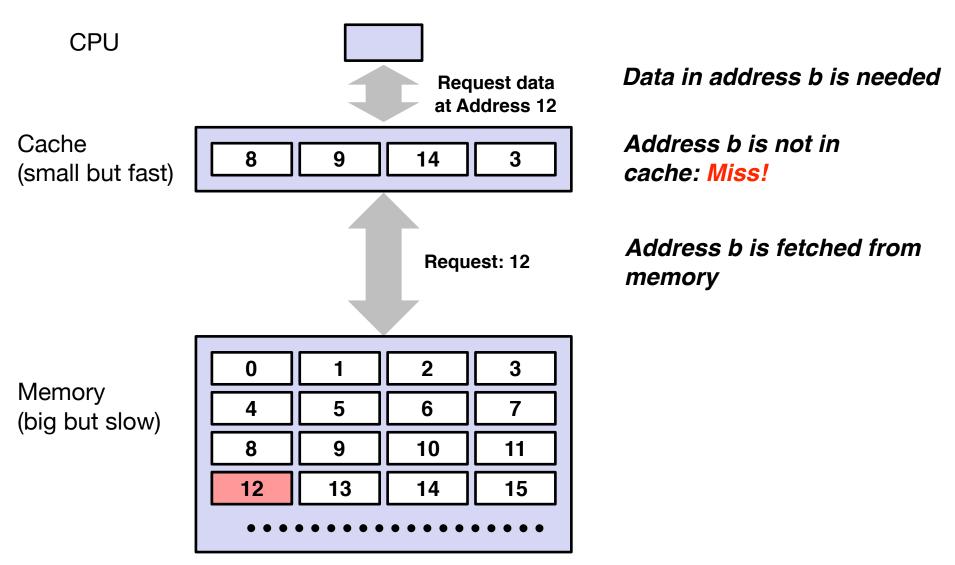

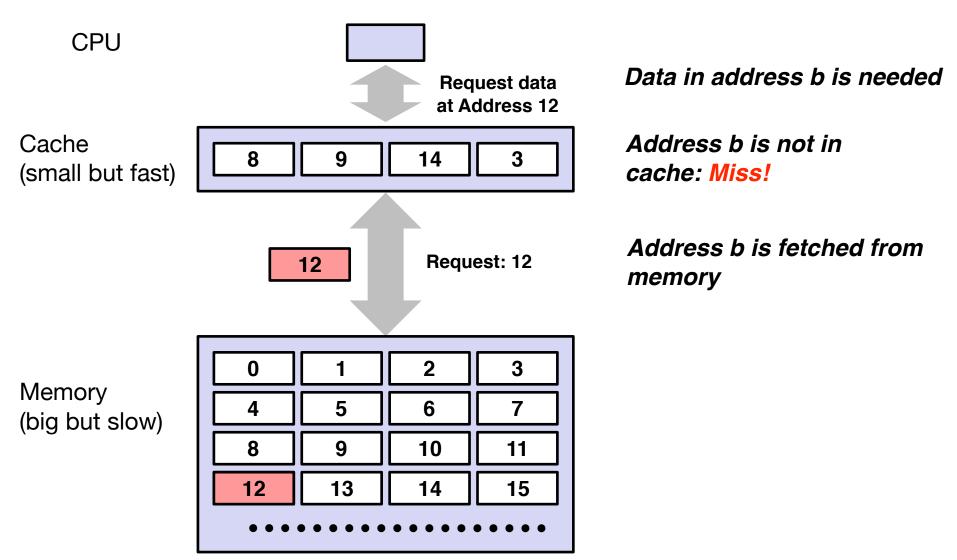

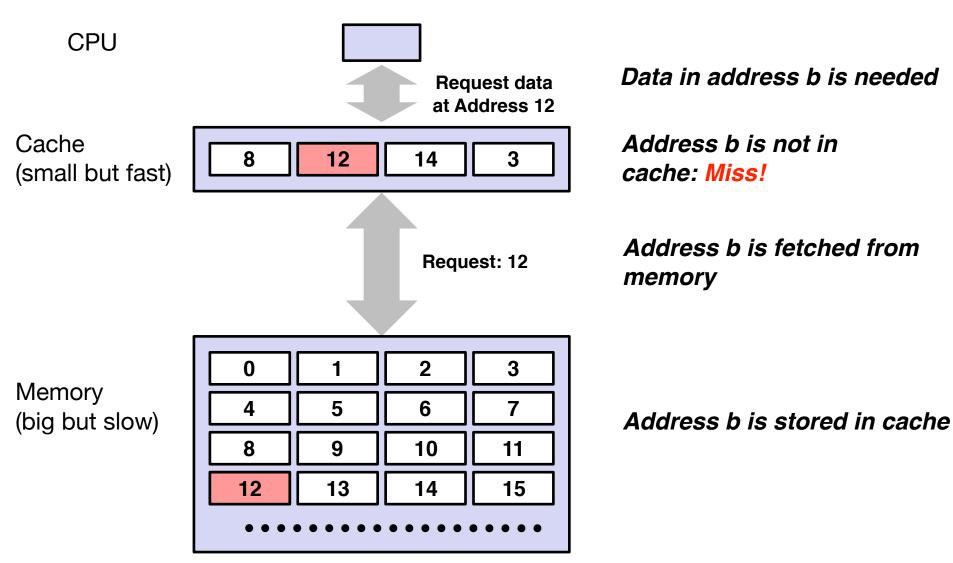

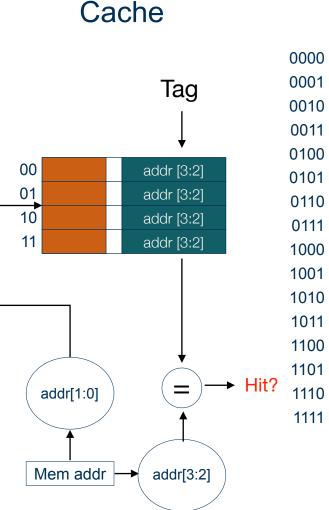

#### Data in address b is needed

Address b is not in cache: Miss!

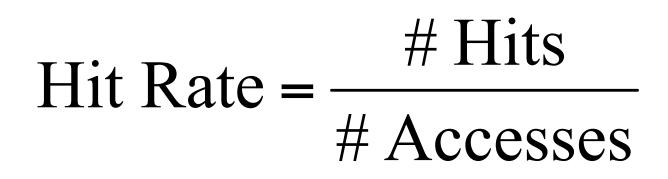

#### **Cache Hit Rate**

- Cache hit is when you find the data in the cache

- Hit rate indicates the effectiveness of the cache

#### **Two Fundamental Issues in Cache Management**

- Finding the data in the cache

- Given an address, how do we decide whether it's in the cacher not?

- Kicking data out of the cache

- Cache is small than memory, so when there's no place left in the cache, we need to kick something out before we can put new data into it, but who to kick out?

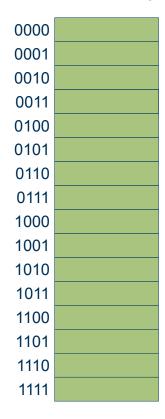

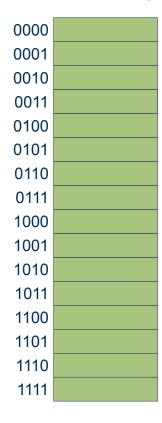

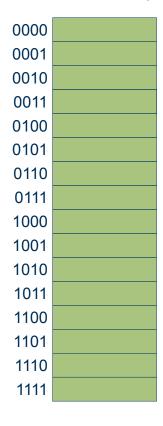

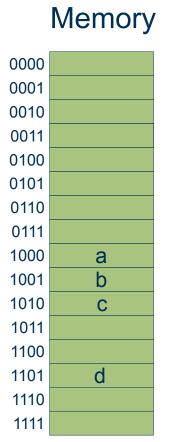

Cache

| Memory |  |  |  |  |

|--------|--|--|--|--|

| 0000   |  |  |  |  |

| 0001   |  |  |  |  |

| 0010   |  |  |  |  |

| 0011   |  |  |  |  |

| 0100   |  |  |  |  |

| 0101   |  |  |  |  |

| 0110   |  |  |  |  |

| 0111   |  |  |  |  |

| 1000   |  |  |  |  |

| 1001   |  |  |  |  |

| 1010   |  |  |  |  |

| 1011   |  |  |  |  |

| 1100   |  |  |  |  |

| 1101   |  |  |  |  |

| 1110   |  |  |  |  |

| 1111   |  |  |  |  |

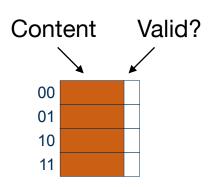

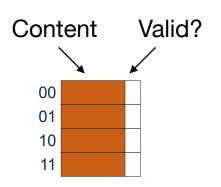

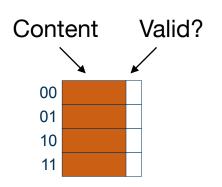

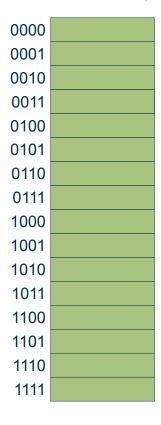

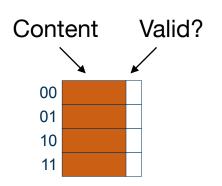

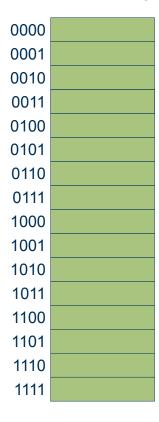

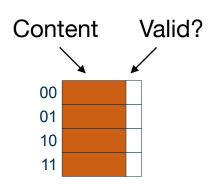

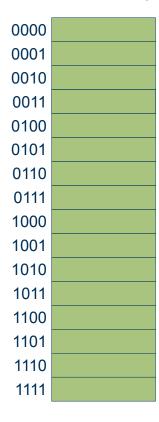

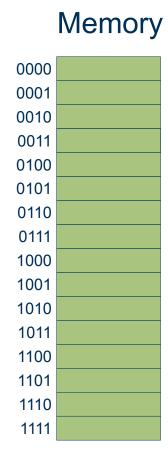

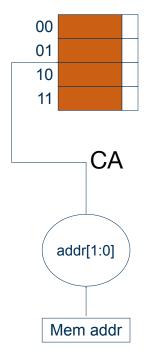

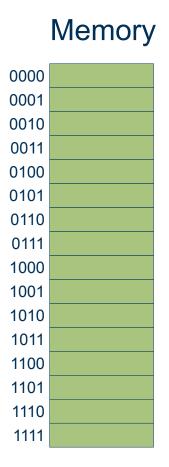

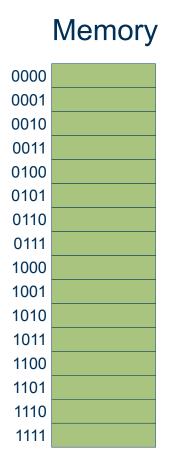

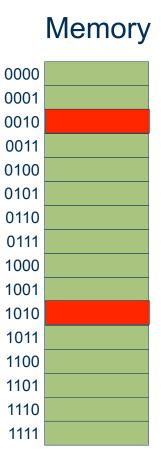

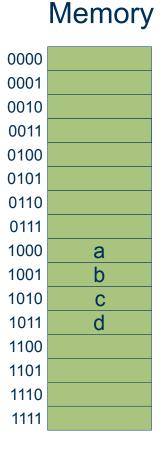

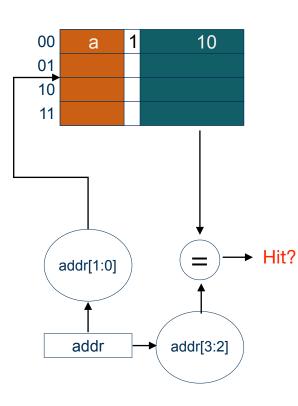

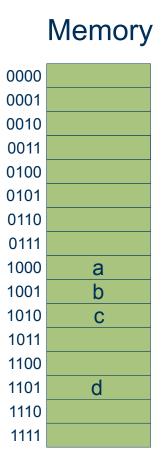

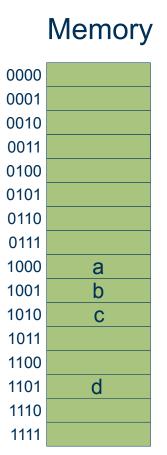

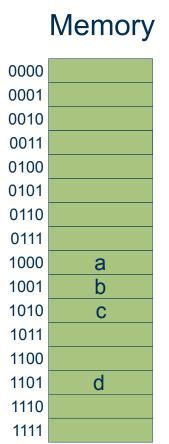

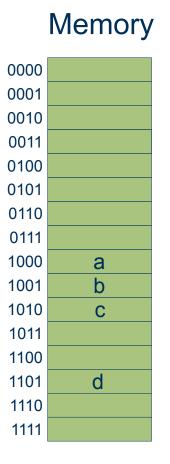

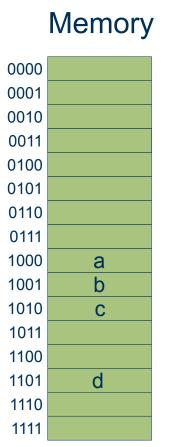

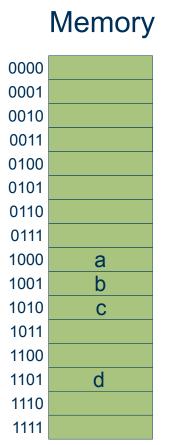

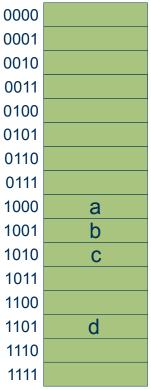

- 16 memory locations

- 4 cache locations

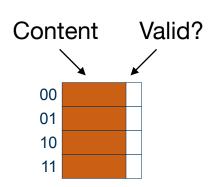

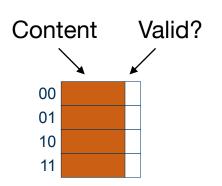

Cache

- 16 memory locations

- 4 cache locations

- Also called cache-line

Cache

- 16 memory locations

- 4 cache locations

- Also called cache-line

- Every location has a valid bit, indicating whether that location contains valid data; 0 initially.

Cache

- 16 memory locations

- 4 cache locations

- Also called cache-line

- Every location has a valid bit, indicating whether that location contains valid data; 0 initially.

- For now, assume cache location size

== memory location size == 1 B

Cache

- 16 memory locations

- 4 cache locations

- Also called cache-line

- Every location has a valid bit, indicating whether that location contains valid data; 0 initially.

- For now, assume cache location size

== memory location size == 1 B

- Assume each memory location can only reside in one cache-line

Cache

- 16 memory locations

- 4 cache locations

- Also called cache-line

- Every location has a valid bit, indicating whether that location contains valid data; 0 initially.

- For now, assume cache location size

== memory location size == 1 B

- Assume each memory location can only reside in one cache-line

- Cache is smaller than memory (obviously)

Cache

- 16 memory locations

- 4 cache locations

- Also called cache-line

- Every location has a valid bit, indicating whether that location contains valid data; 0 initially.

- For now, assume cache location size

== memory location size == 1 B

- Assume each memory location can only reside in one cache-line

- Cache is smaller than memory (obviously)

- Thus, not all memory locations can be cached at the same time

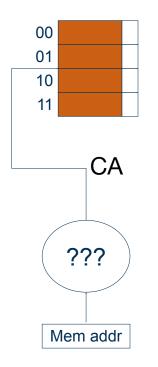

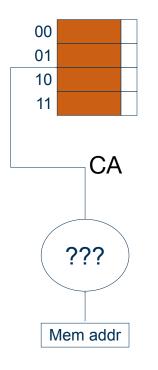

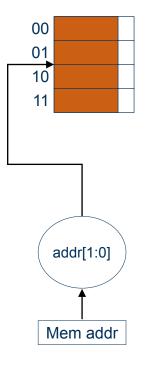

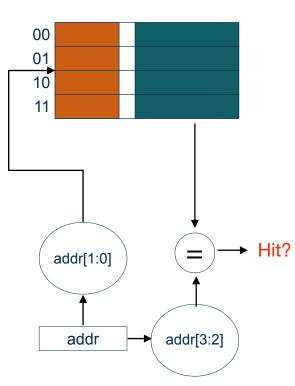

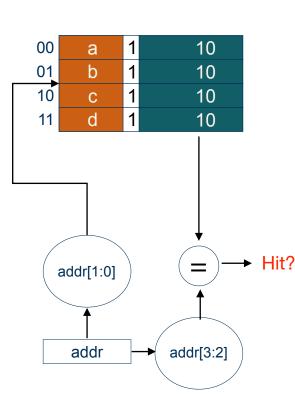

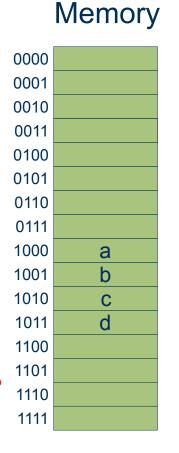

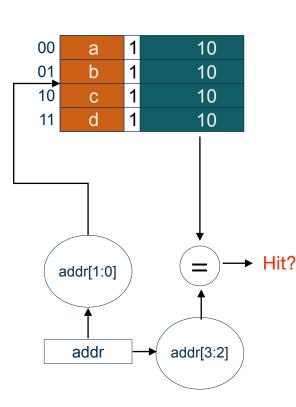

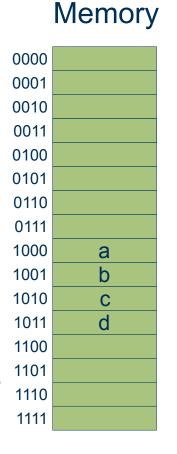

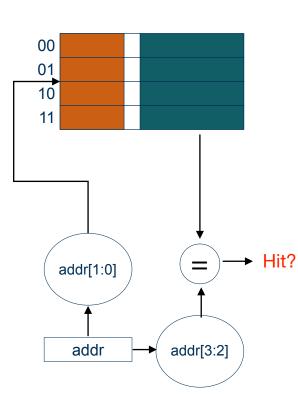

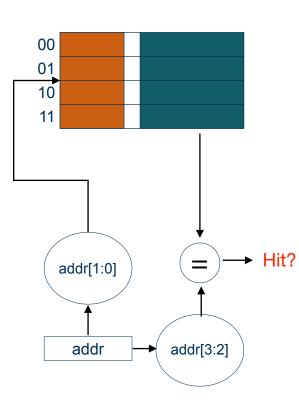

#### **Cache Placement**

#### **Cache Placement**

Cache

• Given a memory addr, say 0x0001, we want to put the data there into the cache; where does the data go?

#### **Function to Address Cache**

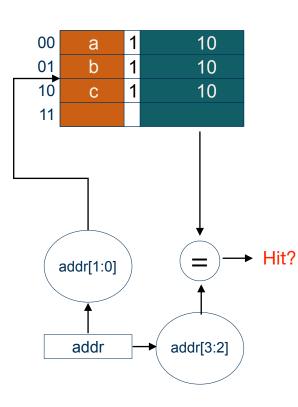

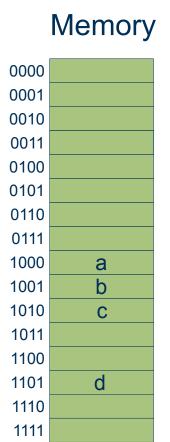

- Simplest way is to take a subset of address bits

- Six combinations in total

- CA = ADDR[3],ADDR[2]

- CA = ADDR[3],ADDR[1]

- CA = ADDR[3],ADDR[0]

- CA = ADDR[2],ADDR[1]

- CA = ADDR[2],ADDR[0]

- CA = ADDR[1],ADDR[0]

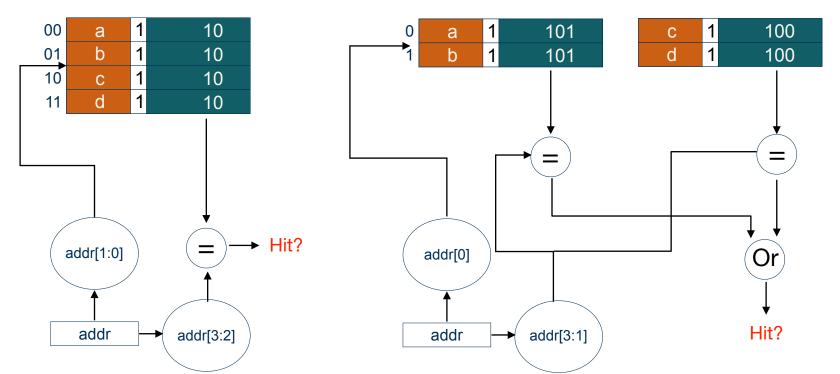

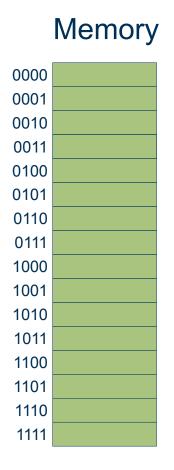

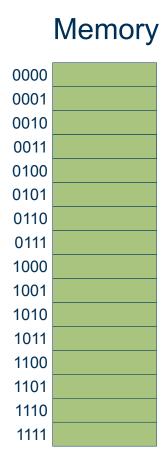

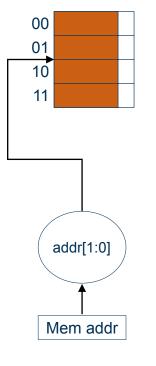

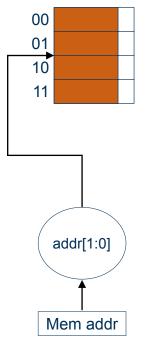

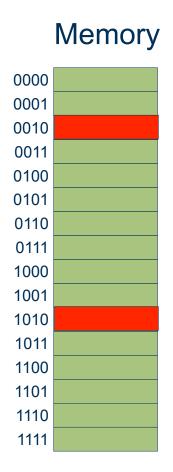

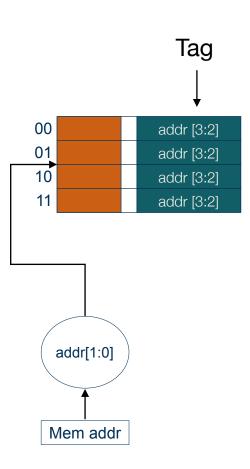

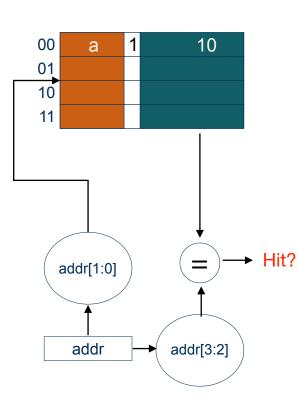

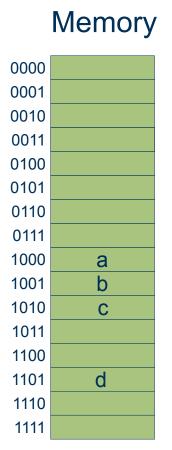

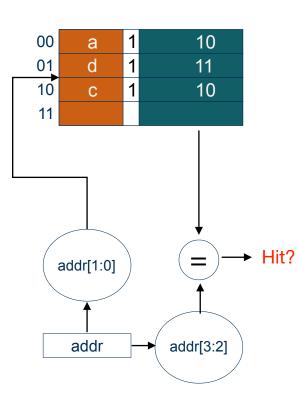

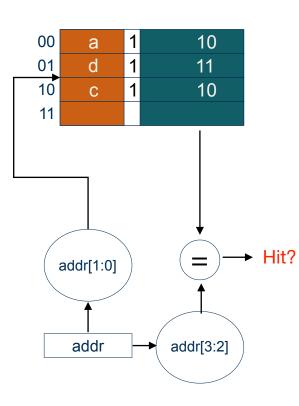

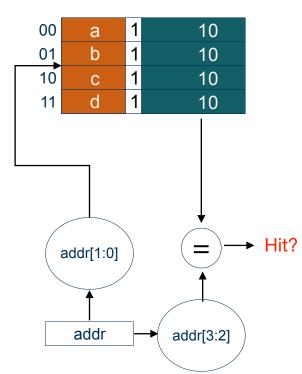

- Direct-Mapped Cache

- CA = ADDR[1],ADDR[0]

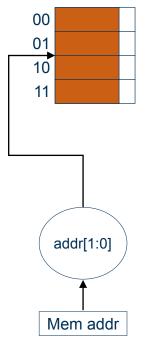

Cache

#### • Direct-Mapped Cache

- CA = ADDR[1],ADDR[0]

- Always use the lower order address bits

- Direct-Mapped Cache

- CA = ADDR[1],ADDR[0]

- Always use the lower order address bits

- Multiple addresses can be mapped to the same location

- Direct-Mapped Cache

- CA = ADDR[1],ADDR[0]

- Always use the lower order address bits

- Multiple addresses can be mapped to the same location

- E.g., 0010 and 1010

- Direct-Mapped Cache

- CA = ADDR[1],ADDR[0]

- Always use the lower order address bits

- Multiple addresses can be mapped to the same location

- E.g., 0010 and 1010

- How do we differentiate between different memory locations that are mapped to the same cache location?

- Direct-Mapped Cache

- CA = ADDR[1],ADDR[0]

- Always use the lower order address bits

- Multiple addresses can be mapped to the same location

- E.g., 0010 and 1010

- How do we differentiate between different memory locations that are mapped to the same cache location?

- Add a tag field for that purpose

- Direct-Mapped Cache

- CA = ADDR[1],ADDR[0]

- Always use the lower order address bits

- Multiple addresses can be mapped to the same location

- E.g., 0010 and 1010

- How do we differentiate between different memory locations that are mapped to the same cache location?

- Add a tag field for that purpose

- ADDR[3] and ADDR[2] in this particular example

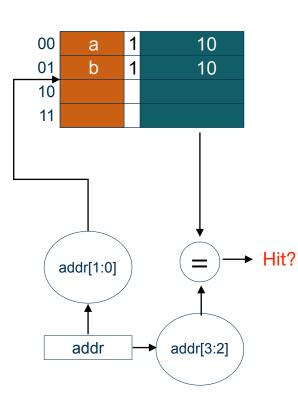

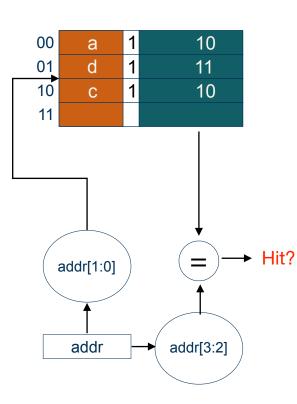

| 00            | addr [3:2] |  |  |  |  |

|---------------|------------|--|--|--|--|

| 01            | addr [3:2] |  |  |  |  |

| 10            | addr [3:2] |  |  |  |  |

| 11            | addr [3:2] |  |  |  |  |

|               |            |  |  |  |  |

|               |            |  |  |  |  |

|               |            |  |  |  |  |

|               | <          |  |  |  |  |

|               |            |  |  |  |  |

| ( addr[1:0] ) |            |  |  |  |  |

|               |            |  |  |  |  |

| <b>▲</b>      |            |  |  |  |  |

| Mem addr      |            |  |  |  |  |

|               |            |  |  |  |  |

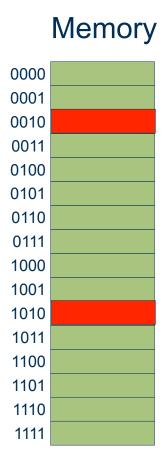

- Direct-Mapped Cache

- CA = ADDR[1],ADDR[0]

- Always use the lower order address bits

- Multiple addresses can be mapped to the same location

- E.g., 0010 and 1010

- How do we differentiate between different memory locations that are mapped to the same cache location?

- Add a tag field for that purpose

- ADDR[3] and ADDR[2] in this particular example

Cache

0101

0110

0111

1000

1001

1010 1011

1100

1101

1110 1111

#### • Direct-Mapped Cache

- CA = ADDR[1],ADDR[0]

- Always use the lower order address bits

- Multiple addresses can be mapped to the same location

- E.g., 0010 and 1010

- How do we differentiate between different memory locations that are mapped to the same cache location?

- Add a tag field for that purpose

- ADDR[3] and ADDR[2] in this particular example

#### Memory 00 01 10 11

- Direct-Mapped Cache

- CA = ADDR[1],ADDR[0]

- Always use the lower order address bits

- Multiple addresses can be mapped to the same location

- E.g., 0010 and 1010

- How do we differentiate between different memory locations that are mapped to the same cache location?

- Add a tag field for that purpose

- ADDR[3] and ADDR[2] in this particular example

Cache

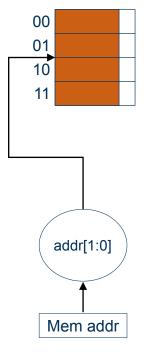

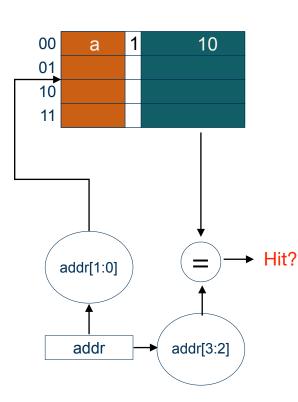

- Assume mem == 0b1000

- Read 0b1000

- Read 0b1001

- Read 0b1010

- Read 0b1011

- Read 0b1000; cache hit?

Cache

- Assume mem == 0b1000

- Read 0b1000

- Read 0b1001

- Read 0b1010

- Read 0b1011

- Read 0b1000; cache hit?

Cache

- Assume mem == 0b1000

- Read 0b1000

- Read 0b1001

- Read 0b1010

- Read 0b1011

- Read 0b1000; cache hit?

Cache

- Assume mem == 0b1000

- Read 0b1000

- Read 0b1001

- Read 0b1010

- Read 0b1011

- Read 0b1000; cache hit?

Cache

- Assume mem == 0b1000

- Read 0b1000

- Read 0b1001

- Read 0b1010

- Read 0b1011

- Read 0b1000; cache hit?

Cache

- Assume mem == 0b1000

- Read 0b1000

- Read 0b1001

- Read 0b1010

- Read 0b1011

- Read 0b1000; cache hit?

Cache

Cache

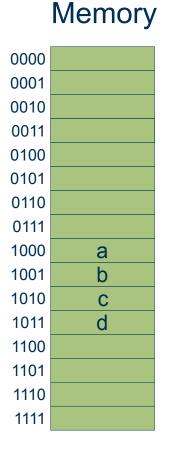

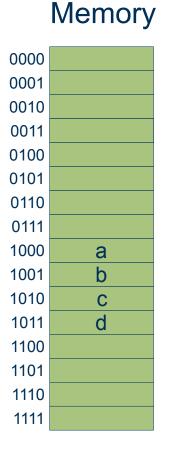

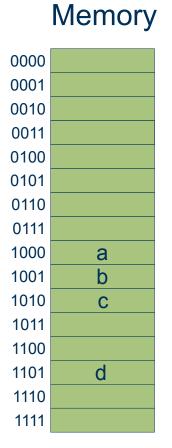

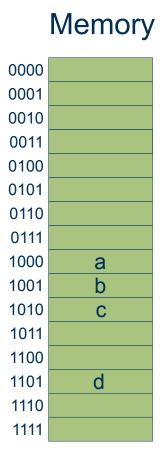

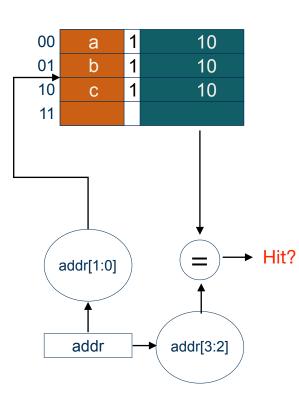

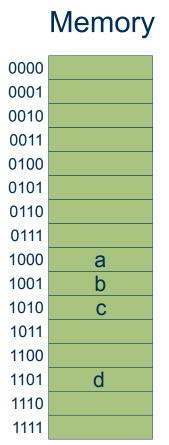

Assume the following memory access stream:

• Read 1000

Cache

Assume the following memory access stream:

• Read 1000

Cache

- Read 1000

- Read 1001

Cache

- Read 1000

- Read 1001

Cache

- Read 1000

- Read 1001

- Read 1010

Cache

- Read 1000

- Read 1001

- Read 1010

Cache

- Read 1000

- Read 1001

- Read 1010

- Read 1101 (kick out 1001)

Cache

- Read 1000

- Read 1001

- Read 1010

- Read 1101 (kick out 1001)

- addr[1:0]: 01

Cache

- Read 1000

- Read 1001

- Read 1010

- Read 1101 (kick out 1001)

- addr[1:0]: 01

- addr[3:2]: 11

Cache

- Read 1000

- Read 1001

- Read 1010

- Read 1101 (kick out 1001)

- addr[1:0]: 01

- addr[3:2]: 11

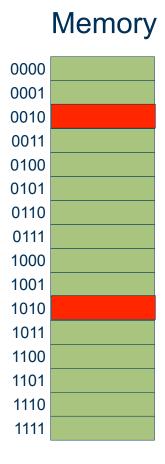

Cache

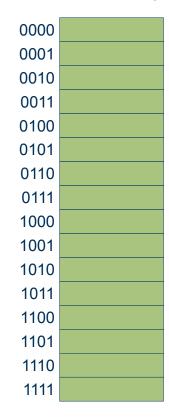

#### Memory

- Read 1000

- Read 1001

- Read 1010

- Read 1101 (kick out 1001)

- addr[1:0]: 01

- addr[3:2]: 11

- Read 1001 -> Miss!

Cache

- Read 1000

- Read 1001

- Read 1010

- Read 1101 (kick out 1001)

- addr[1:0]: 01

- addr[3:2]: 11

- Read 1001 -> Miss!

- Why? Each memory location is mapped to only one cache location

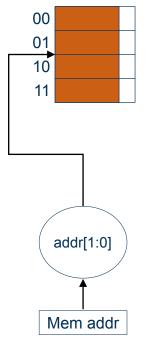

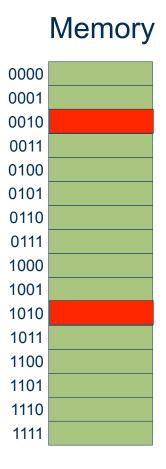

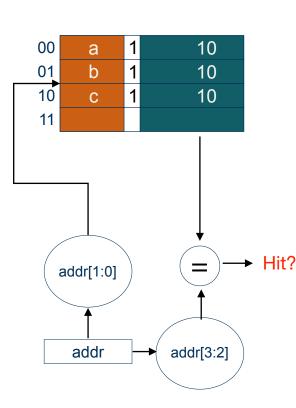

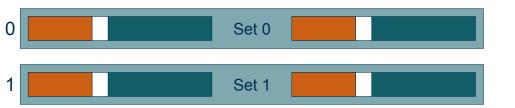

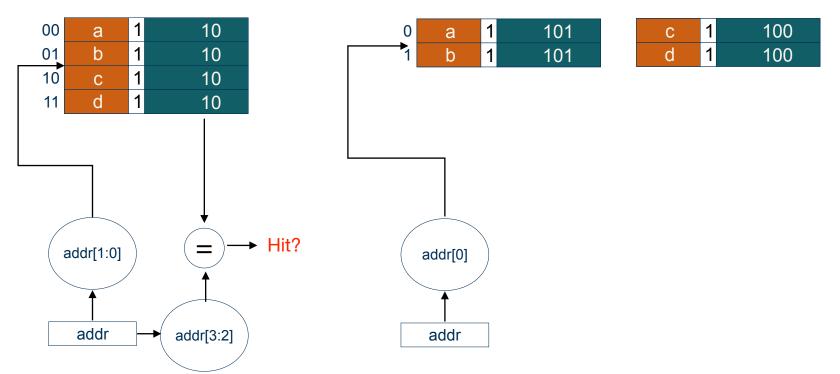

#### Sets

Cache

| 00 |  |  |

|----|--|--|

| 01 |  |  |

| 10 |  |  |

| 11 |  |  |

#### Memory

- Each cacheable memory location is mapped to **a set of cache locations**

- A set is one or more cache locations

- Set size is the number of locations in a set, also called **associativity**

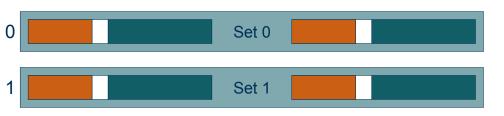

• 2 sets, each set has two entries

- 2 sets, each set has two entries

- Only need one bit, addr[0] to index into the cache now

- 2 sets, each set has two entries

- Only need one bit, addr[0] to index into the cache now

- Correspondingly, the tag needs 3 bits: Addr[3:1]

- 2 sets, each set has two entries

- Only need one bit, addr[0] to index into the cache now

- Correspondingly, the tag needs 3 bits: Addr[3:1]

- Either entry can store any address that gets mapped to that set

- 2 sets, each set has two entries

- Only need one bit, addr[0] to index into the cache now

- Correspondingly, the tag needs 3 bits: Addr[3:1]

- Either entry can store any address that gets mapped to that set

- Now with the same access stream:

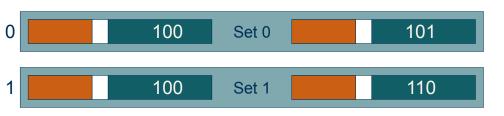

- 2 sets, each set has two entries

- Only need one bit, addr[0] to index into the cache now

- Correspondingly, the tag needs 3 bits: Addr[3:1]

- Either entry can store any address that gets mapped to that set

- Now with the same access stream:

- Read 1000

0 100 Set 0 100 1 100 Set 1

- 2 sets, each set has two entries

- Only need one bit, addr[0] to index into the cache now

- Correspondingly, the tag needs 3 bits: Addr[3:1]

- Either entry can store any address that gets mapped to that set

- Now with the same access stream:

- Read 1000

- Read 1001

0 100 Set 0 101 1 100 Set 1

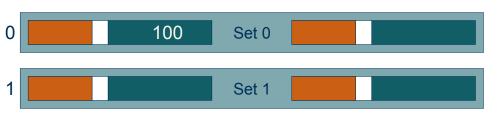

- 2 sets, each set has two entries

- Only need one bit, addr[0] to index into the cache now

- Correspondingly, the tag needs 3 bits: Addr[3:1]

- Either entry can store any address that gets mapped to that set

- Now with the same access stream:

- Read 1000

- Read 1001

- Read 1010

0 100 Set 0 101 1 100 Set 1

- 2 sets, each set has two entries

- Only need one bit, addr[0] to index into the cache now

- Correspondingly, the tag needs 3 bits: Addr[3:1]

- Either entry can store any address that gets mapped to that set

- Now with the same access stream:

- Read 1000

- Read 1001

- Read 1010

- Read 1101 (1001 can still stay)

- 2 sets, each set has two entries

- Only need one bit, addr[0] to index into the cache now

- Correspondingly, the tag needs 3 bits: Addr[3:1]

- Either entry can store any address that gets mapped to that set

- Now with the same access stream:

- Read 1000

- Read 1001

- Read 1010

- Read 1101 (1001 can still stay)

- Read 1001 -> Hit!

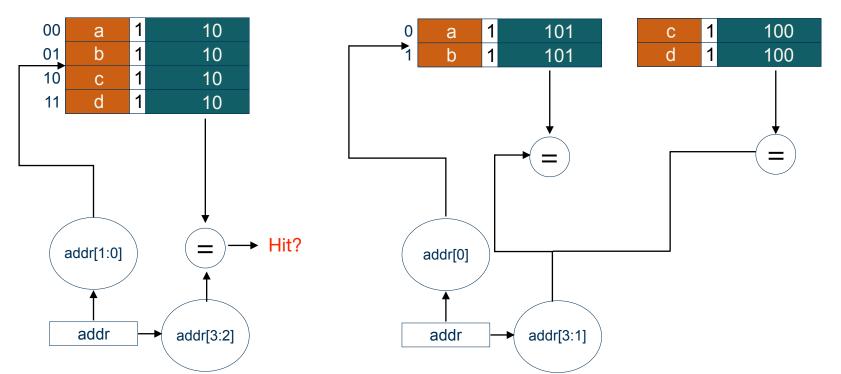

- One single set that contains all the cache locations

- Also called Fully-Associative Cache

- Every entry can store any cache-line that maps to that set

- One single set that contains all the cache locations

- Also called Fully-Associative Cache

- Every entry can store any cache-line that maps to that set

- One single set that contains all the cache locations

- Also called Fully-Associative Cache

- Every entry can store any cache-line that maps to that set

Assuming the same access stream

• Read 1000

- One single set that contains all the cache locations

- Also called Fully-Associative Cache

- Every entry can store any cache-line that maps to that set

- Read 1000

- Read 1001

- One single set that contains all the cache locations

- Also called Fully-Associative Cache

- Every entry can store any cache-line that maps to that set

- Read 1000

- Read 1001

- Read 1010

- One single set that contains all the cache locations

- Also called Fully-Associative Cache

- Every entry can store any cache-line that maps to that set

- Read 1000

- Read 1001

- Read 1010

- Read 1101

- One single set that contains all the cache locations

- Also called Fully-Associative Cache

- Every entry can store any cache-line that maps to that set

- Read 1000

- Read 1001

- Read 1010

- Read 1101

- Read 1001 -> Hit!

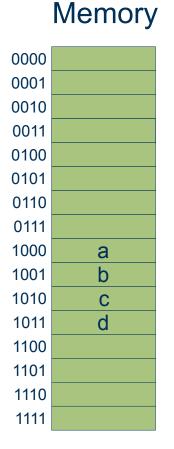

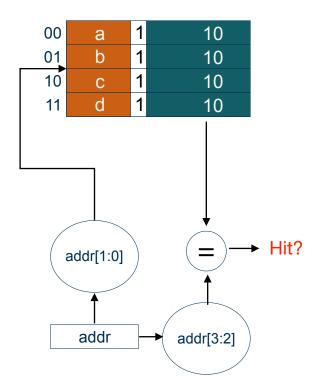

- Direct-Mapped cache

- Generally lower hit rate

- Simpler, Faster

- Direct-Mapped cache

- Generally lower hit rate

- Simpler, Faster

- Direct-Mapped cache

- Generally lower hit rate

- Simpler, Faster

- Associative cache

- Generally higher hit rate. Better utilization of cache resources

- Slower. Why?

| 0 | а | 1 | 101 | С | 1 | 100 |

|---|---|---|-----|---|---|-----|

| 1 | b | 1 | 101 | d | 1 | 100 |

- Direct-Mapped cache

- Generally lower hit rate

- Simpler, Faster

- Associative cache

- Generally higher hit rate. Better utilization of cache resources

- Slower. Why?

- Direct-Mapped cache

- Generally lower hit rate

- Simpler, Faster

- Associative cache

- Generally higher hit rate. Better utilization of cache resources

- Slower. Why?

- Direct-Mapped cache

- Generally lower hit rate

- Simpler, Faster

- Associative cache

- Generally higher hit rate. Better utilization of cache resources

- Slower. Why?