# CSC 252: Computer Organization Spring 2020: Lecture 17

Instructor: Yuhao Zhu

Department of Computer Science University of Rochester

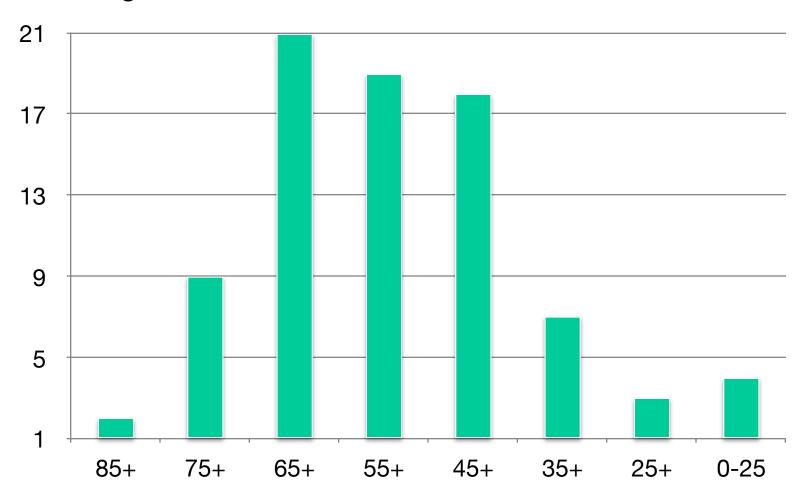

• Recall: 75 full score + 20 extra credit

• Max: 90

• Min: 11.3

• Median: 58.25

• Mean: 57.71

• Standard Deviation: 16.23

• Mid-term grade distribution

- Point distribution:

- 8% per lab: 40% in total

- 22% for mid-term

- 38% for final

- Point distribution:

- 8% per lab: 40% in total

- 22% for mid-term

- 38% for final

- If you can't make an office hour (mine or TAs), feel free to email and/or schedule a different time at your convenience

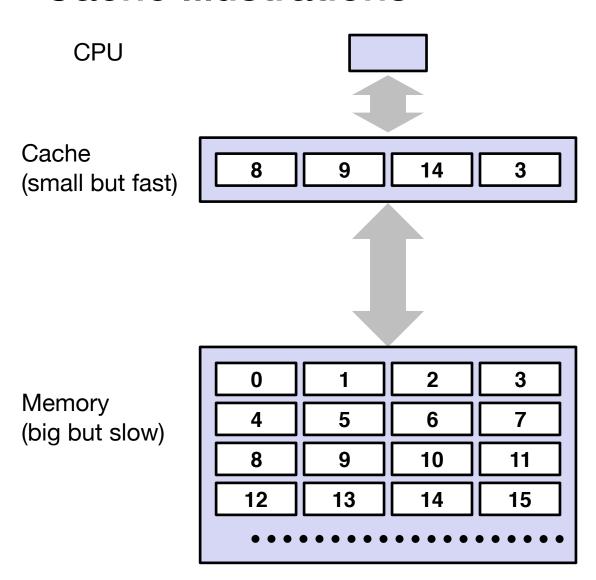

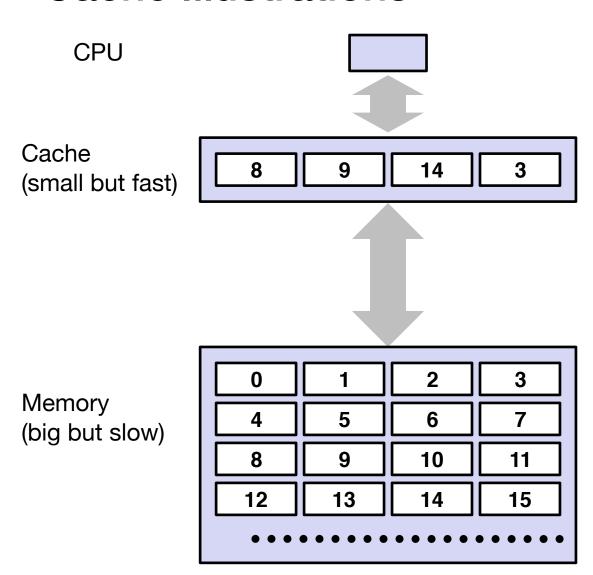

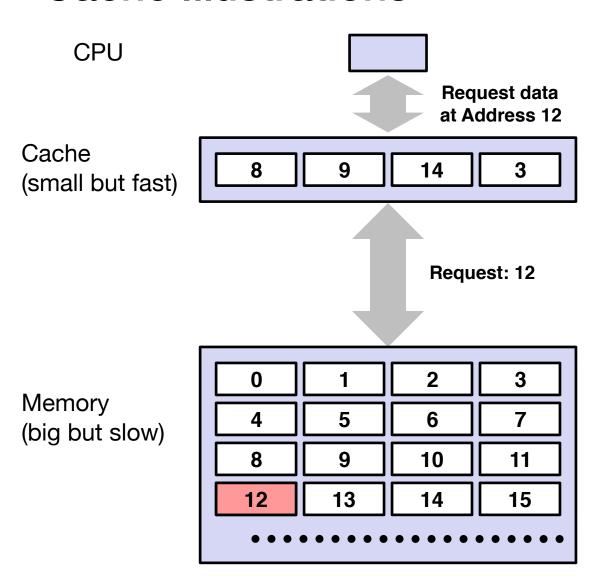

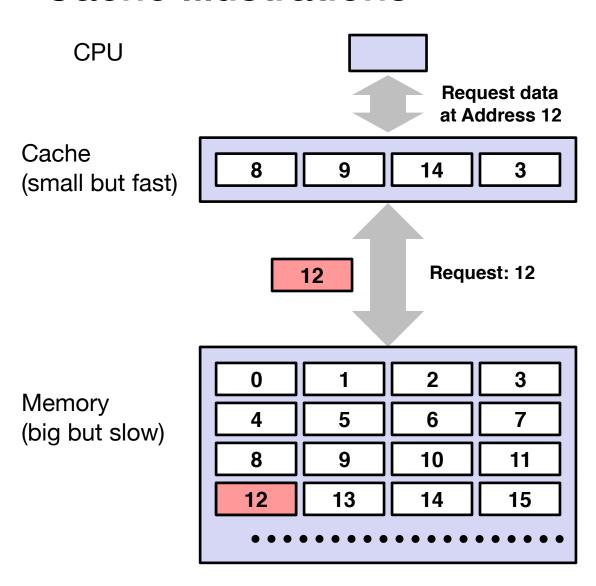

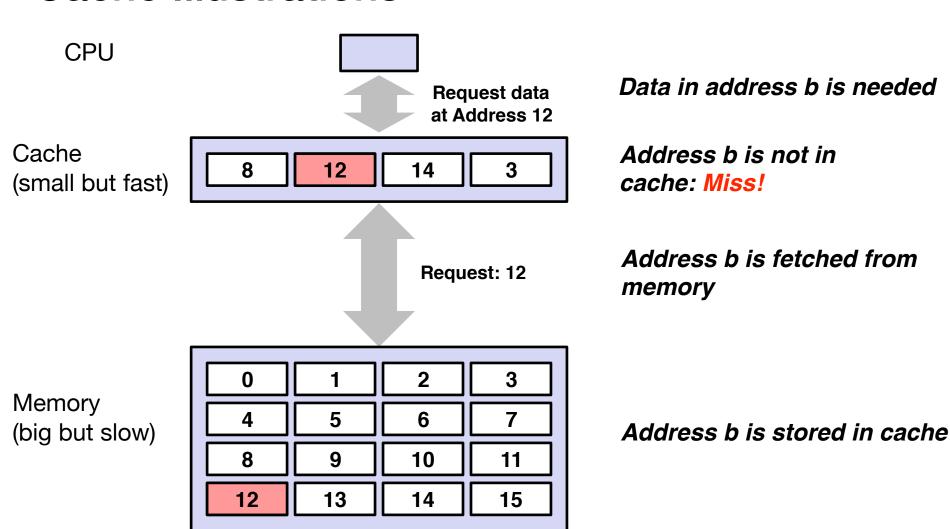

CPU

Memory (big but slow)

| 0                                       | 1  | 2  | 3  |  |

|-----------------------------------------|----|----|----|--|

| 4                                       | 5  | 6  | 7  |  |

| 8                                       | 9  | 10 | 11 |  |

| 12                                      | 13 | 14 | 15 |  |

| • • • • • • • • • • • • • • • • • • • • |    |    |    |  |

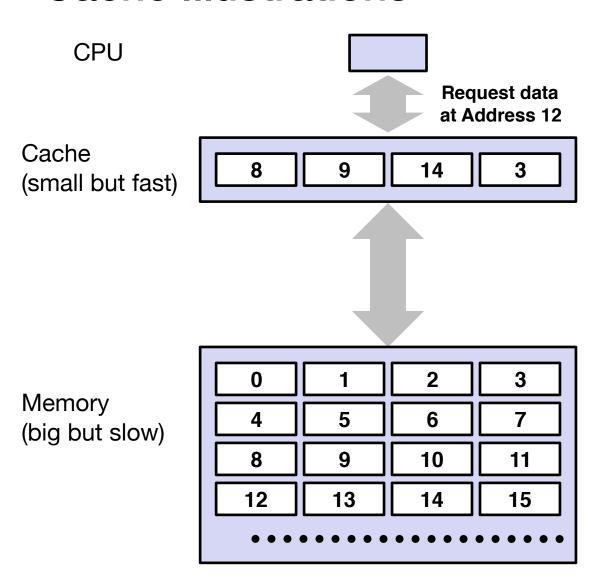

Data in address b is needed

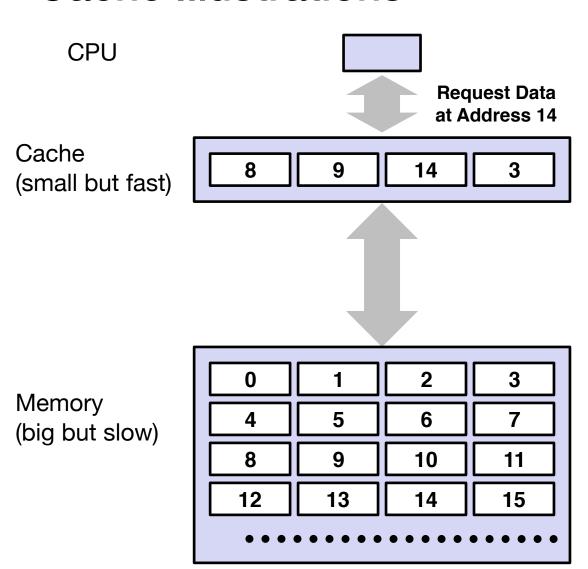

Data in address b is needed

Address b is in cache: Hit!

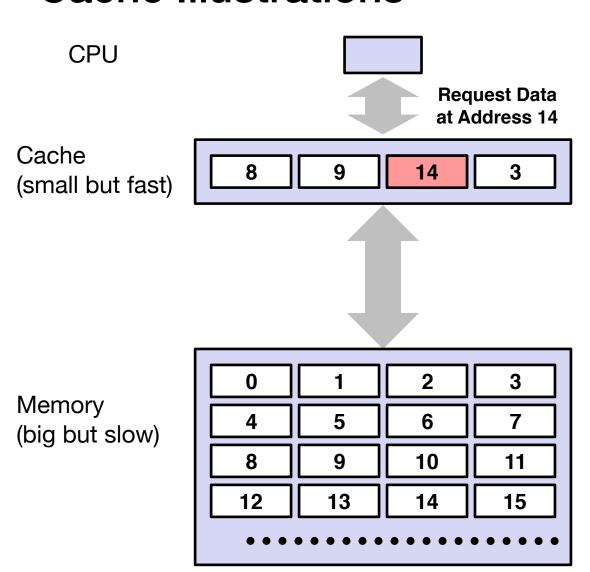

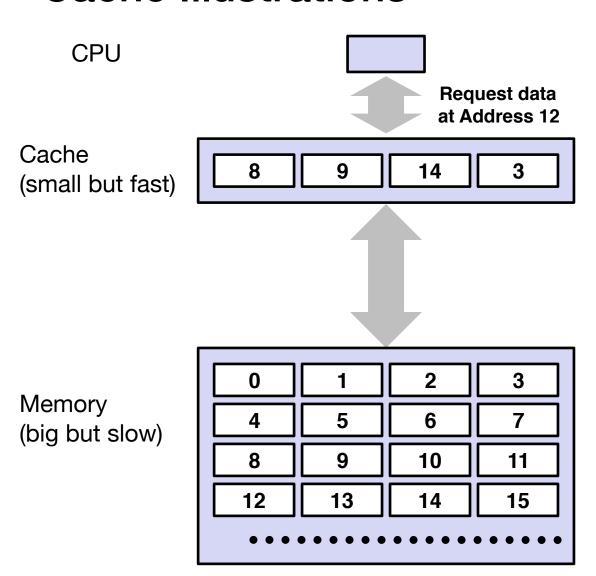

Data in address b is needed

Address b is not in cache: Miss!

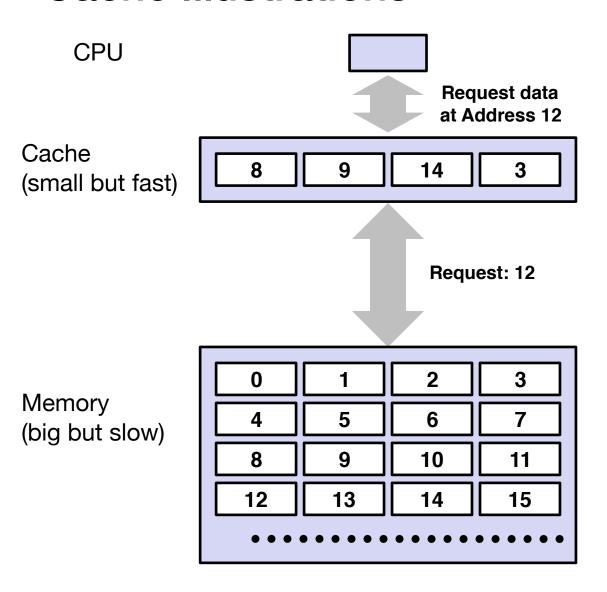

Data in address b is needed

Address b is not in cache: Miss!

Address b is fetched from memory

Data in address b is needed

Address b is not in cache: Miss!

Address b is fetched from memory

Data in address b is needed

Address b is not in cache: Miss!

Address b is fetched from memory

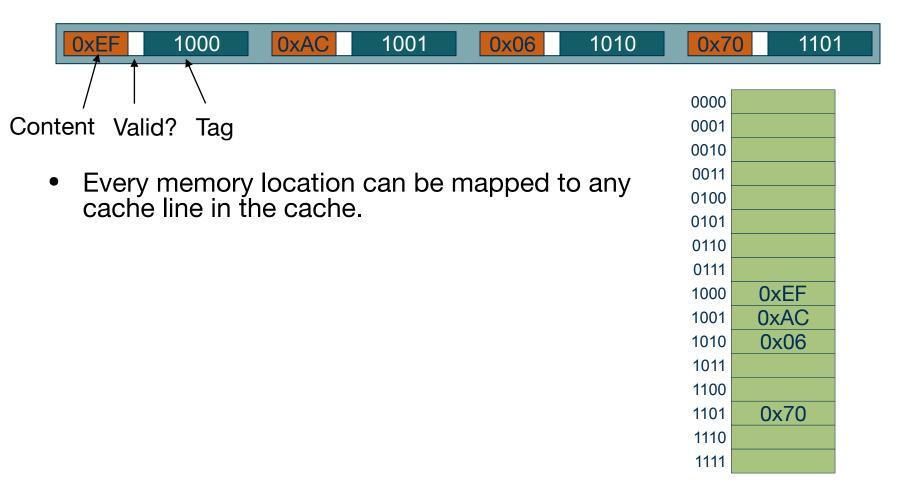

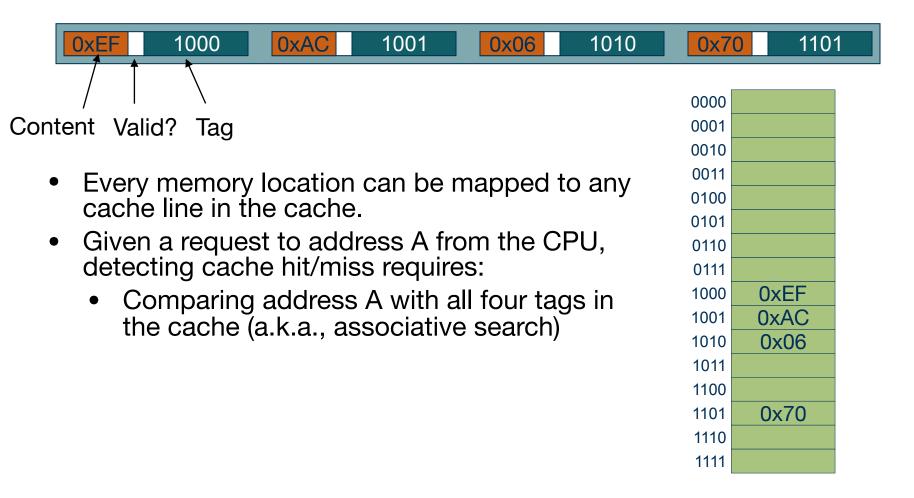

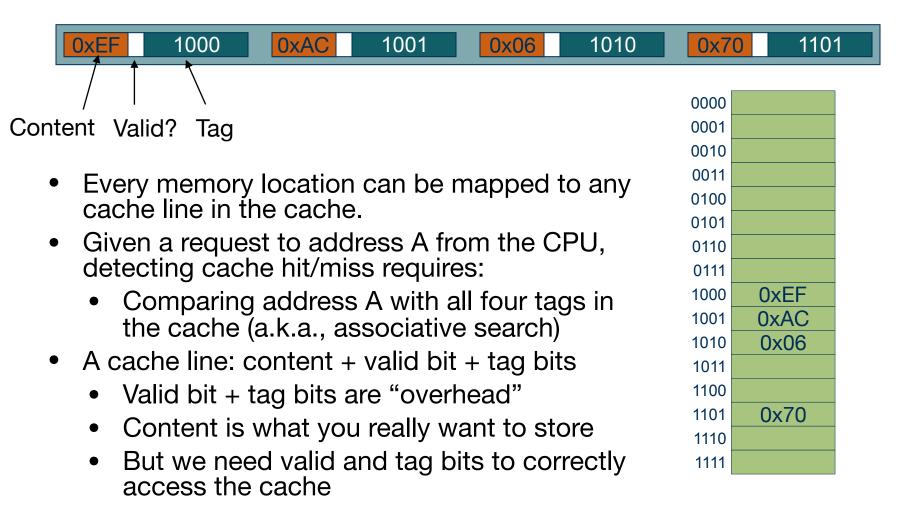

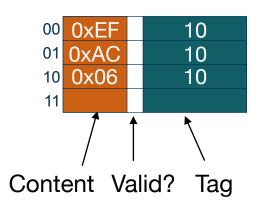

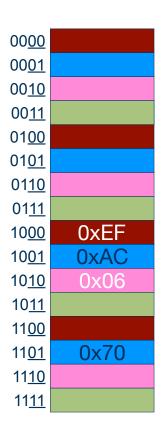

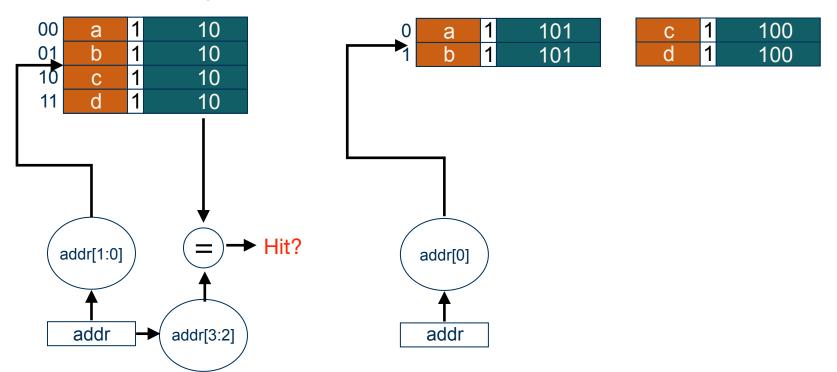

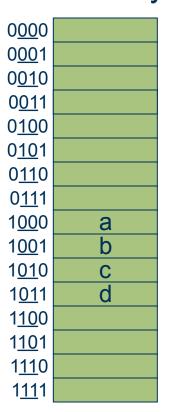

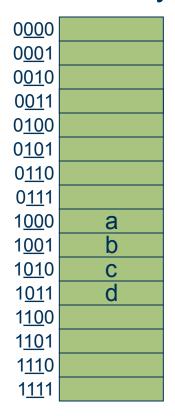

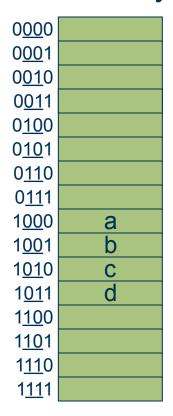

# **Fully Associative Cache**

# **Fully Associative Cache**

# **Fully Associative Cache**

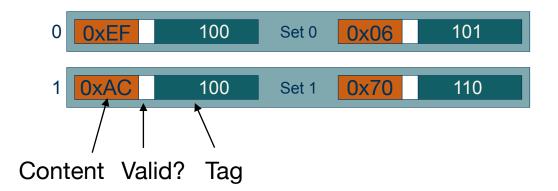

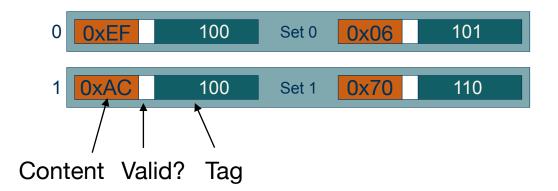

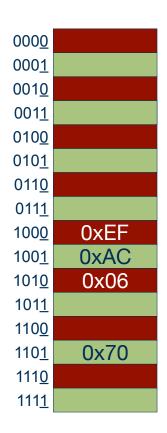

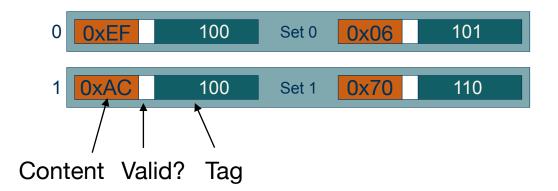

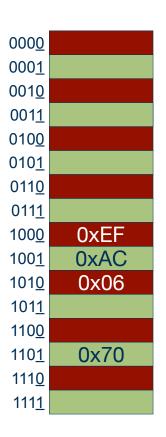

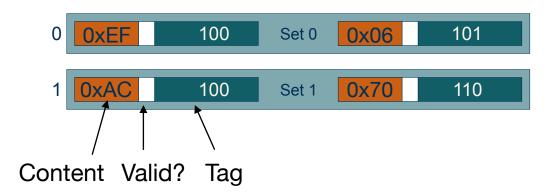

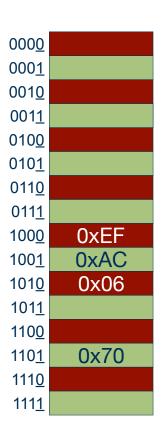

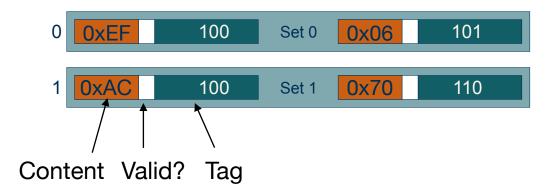

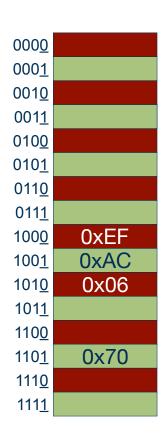

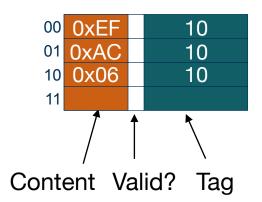

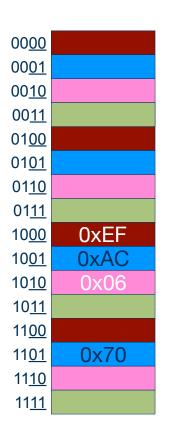

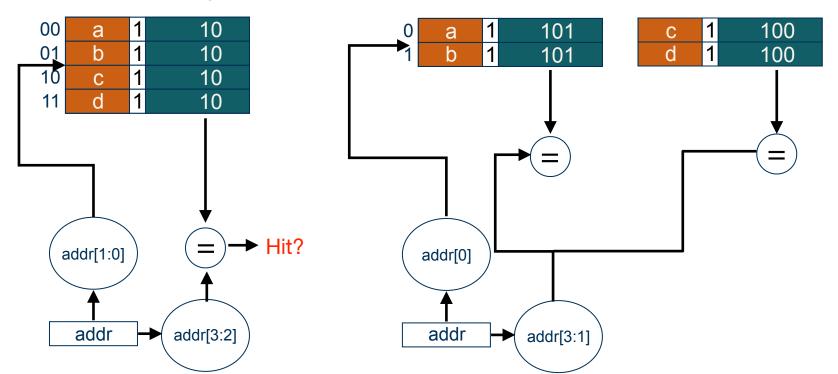

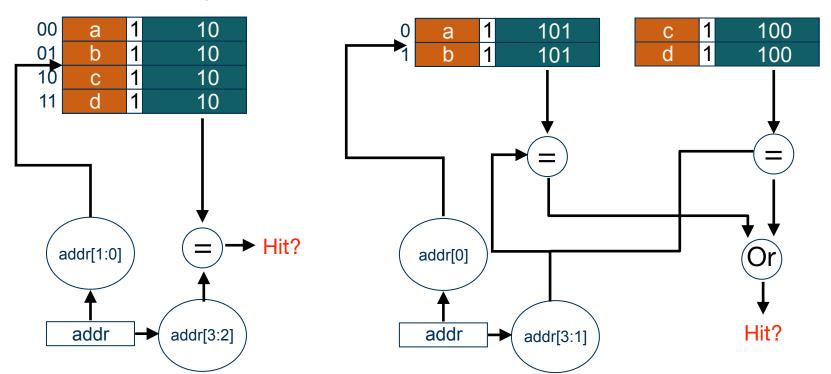

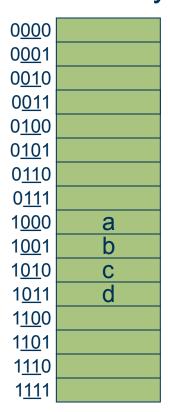

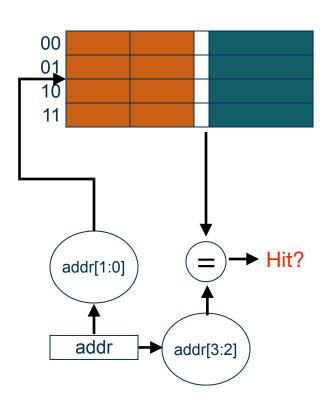

4 cache lines are organized into two sets; each set has 2 cache lines (i.e., 2 ways)

- 4 cache lines are organized into two sets; each set has 2 cache lines (i.e., 2 ways)

- Even address go to first set and odd addresses go to the second set

- 4 cache lines are organized into two sets; each set has 2 cache lines (i.e., 2 ways)

- Even address go to first set and odd addresses go to the second set

- Each address can be mapped to either cache line in the same set

- Using the LSB to find the set (i.e., odd vs. even)

- Tag now stores the higher 3 bits instead of the entire address

Given a request to address, say 1011, from the CPU, detecting cache hit/miss requires:

- Given a request to address, say 1011, from the CPU, detecting cache hit/miss requires:

- Using the LSB to index into the cache and find the corresponding set, in this case set 1

- Given a request to address, say 1011, from the CPU, detecting cache hit/miss requires:

- Using the LSB to index into the cache and find the corresponding set, in this case set 1

- Then do an associative search in that set, i.e., compare the highest 3 bits 101 with both tags in set 1

- Given a request to address, say 1011, from the CPU, detecting cache hit/miss requires:

- Using the LSB to index into the cache and find the corresponding set, in this case set 1

- Then do an associative search in that set, i.e., compare the highest 3 bits 101 with both tags in set 1

- Only two comparisons required

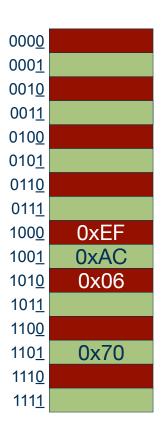

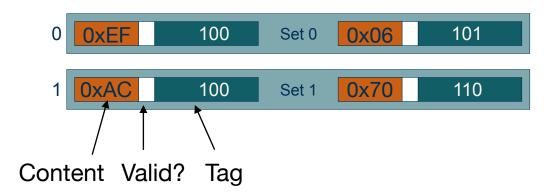

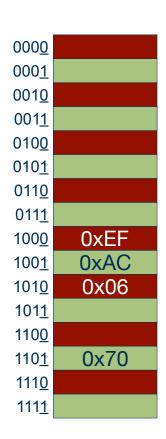

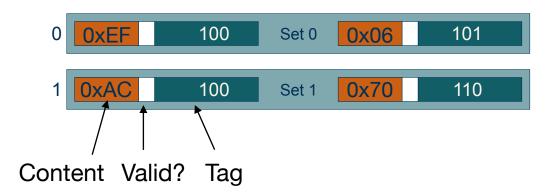

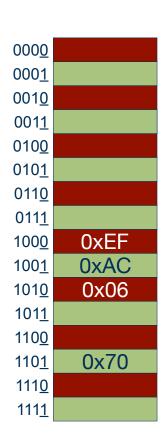

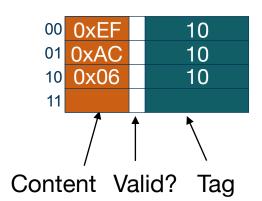

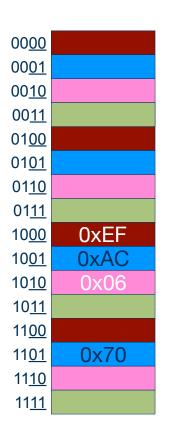

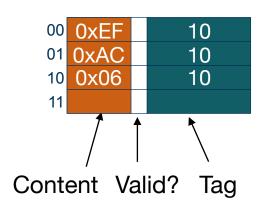

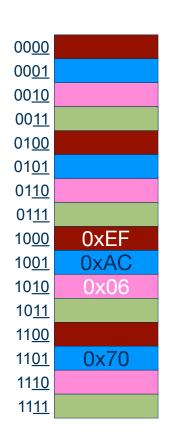

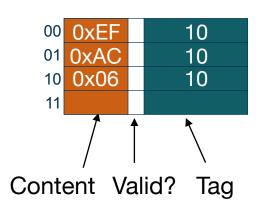

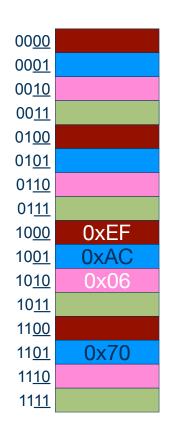

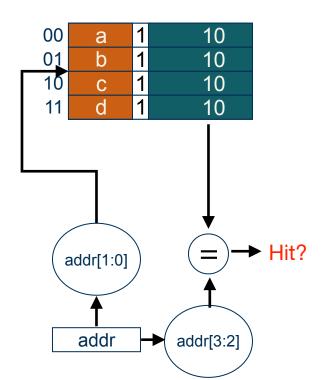

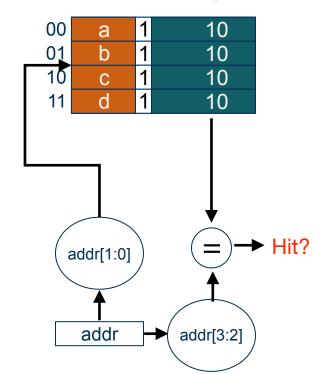

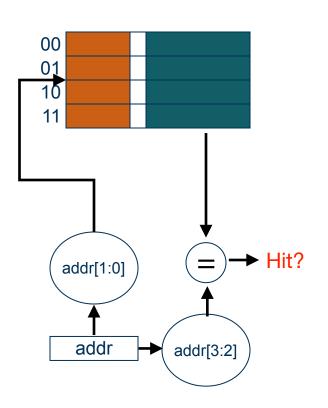

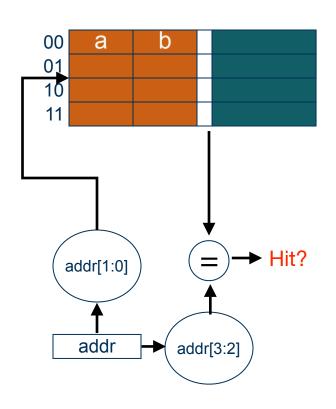

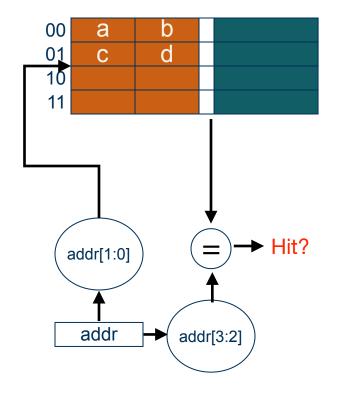

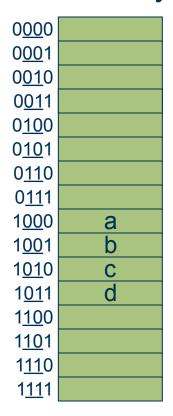

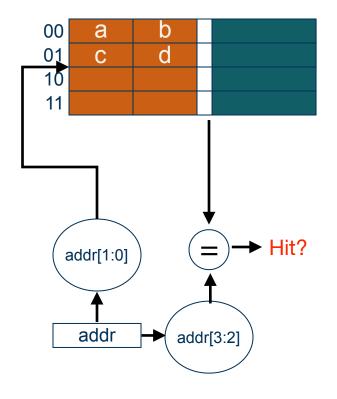

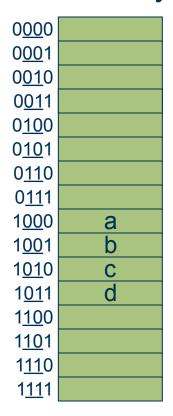

- 4 cache lines are organized into four sets

- Each memory localization can only be mapped to one set

- Using the 2 LSBs to find the set

- Tag now stores the higher 2 bits

Given a request to address, say 1101, from the CPU, detecting cache hit/miss requires:

- Given a request to address, say 1101, from the CPU, detecting cache hit/miss requires:

- Using the 2 LSBs to index into the cache and find the set, in this case set 01

- Given a request to address, say 1101, from the CPU, detecting cache hit/miss requires:

- Using the 2 LSBs to index into the cache and find the set, in this case set 01

- Then do an associative search in that set, i.e., compare the highest 2 bits 11 in the address with the tag in set 01 —> miss

- Given a request to address, say 1101, from the CPU, detecting cache hit/miss requires:

- Using the 2 LSBs to index into the cache and find the set, in this case set 01

- Then do an associative search in that set, i.e., compare the highest 2 bits 11 in the address with the tag in set 01 —> miss

- Only one comparison required

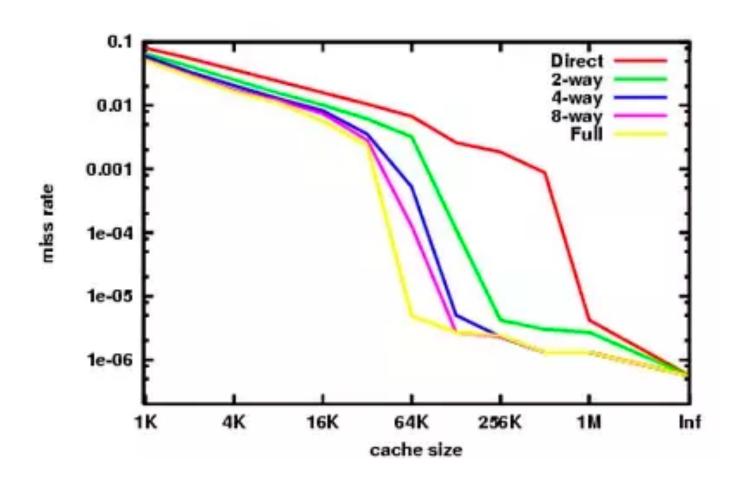

- Direct-Mapped cache

- Generally lower hit rate

- Simpler, Faster

- Direct-Mapped cache

- Generally lower hit rate

- Simpler, Faster

- Direct-Mapped cache

- Generally lower hit rate

- Simpler, Faster

- Associative cache

- Generally higher hit rate. Better utilization of cache resources

- Slower and higher power consumption. Why?

| 0 | а | 1 | 101 |

|---|---|---|-----|

| 1 | b | 1 | 101 |

- Direct-Mapped cache

- Generally lower hit rate

- Simpler, Faster

- Associative cache

- Generally higher hit rate. Better utilization of cache resources

- Slower and higher power consumption. Why?

- Direct-Mapped cache

- Generally lower hit rate

- Simpler, Faster

- Associative cache

- Generally higher hit rate. Better utilization of cache resources

- Slower and higher power consumption. Why?

- Direct-Mapped cache

- Generally lower hit rate

- Simpler, Faster

- Associative cache

- Generally higher hit rate. Better utilization of cache resources

- Slower and higher power consumption. Why?

## **Cache Organization**

- Finding a name in a roster

- If the roster is completely unorganized

- Need to compare the name with all the names in the roster

- Same as a fully-associative cache

- If the roster is ordered by last name, and within the same last name different first names are unordered

- First find the last name group

- Then compare the first name with all the first names in the same group

- Same as a set-associative cache

# Cache Access Summary (So far...)

- Assuming b bits in a memory address

- The b bits are split into two halves:

- Lower s bits used as index to find a set. Total sets S = 2<sup>s</sup>

- The higher (b s) bits are used for the tag

- Associativity n (i.e., the number of ways in a cache set) is independent of the the split between index and tag

# Locality again

- So far: temporal locality

- What about spatial?

- Idea: Each cache location (cache line) store multiple bytes

### Cache

### Cache

### Cache

## Memory

• Read 1000

### Cache

- Read 1000

- Read 1001 (Hit!)

### Cache

- Read 1000

- Read 1001 (Hit!)

- Read 1010

#### Cache

- Read 1000

- Read 1001 (Hit!)

- Read 1010

- Read 1011 (Hit!)

# Cache Access Summary

- Assuming b bits in a memory address

- The b bits are split into three fields:

- Lower / bits are used for byte offset within a cache line. Cache line size  $L = 2^{l}$

- Next s bits used as index to find a set. Total sets S = 2<sup>s</sup>

- The higher (b I s) bits are used for the tag

- Associativity n is independent of the split between index and tag

• Read miss: Put into cache

- Read miss: Put into cache

- Any reason not to put into cache?

- Read miss: Put into cache

- Any reason not to put into cache?

- Read hit: Nothing special. Enjoy the hit!

- Intricacy: data value is modified!

- Implication: value in cache will be different from that in memory!

- When do we write the modified data in a cache to the next level?

- Write through: At the time the write happens

- Intricacy: data value is modified!

- Implication: value in cache will be different from that in memory!

- When do we write the modified data in a cache to the next level?

- Write through: At the time the write happens

- Write back: When the cache line is evicted

- Intricacy: data value is modified!

- Implication: value in cache will be different from that in memory!

- When do we write the modified data in a cache to the next level?

- Write through: At the time the write happens

- Write back: When the cache line is evicted

- Write-back

- + Can consolidate multiple writes to the same block before eviction. Potentially saves bandwidth between cache and memory + saves energy

- - Need a bit in the tag store indicating the block is "dirty/modified"

- Intricacy: data value is modified!

- Implication: value in cache will be different from that in memory!

- When do we write the modified data in a cache to the next level?

- Write through: At the time the write happens

- Write back: When the cache line is evicted

- Write-back

- + Can consolidate multiple writes to the same block before eviction. Potentially saves bandwidth between cache and memory + saves energy

- - Need a bit in the tag store indicating the block is "dirty/modified"

- Intricacy: data value is modified!

- Implication: value in cache will be different from that in memory!

- When do we write the modified data in a cache to the next level?

- Write through: At the time the write happens

- Write back: When the cache line is evicted

- Write-back

- + Can consolidate multiple writes to the same block before eviction. Potentially saves bandwidth between cache and memory + saves energy

- - Need a bit in the tag store indicating the block is "dirty/modified"

- Write-through

- Intricacy: data value is modified!

- Implication: value in cache will be different from that in memory!

- When do we write the modified data in a cache to the next level?

- Write through: At the time the write happens

- Write back: When the cache line is evicted

- Write-back

- + Can consolidate multiple writes to the same block before eviction. Potentially saves bandwidth between cache and memory + saves energy

- - Need a bit in the tag store indicating the block is "dirty/modified"

- Write-through

- + Simpler

- Intricacy: data value is modified!

- Implication: value in cache will be different from that in memory!

- When do we write the modified data in a cache to the next level?

- Write through: At the time the write happens

- Write back: When the cache line is evicted

- Write-back

- + Can consolidate multiple writes to the same block before eviction. Potentially saves bandwidth between cache and memory + saves energy

- - Need a bit in the tag store indicating the block is "dirty/modified"

- Write-through

- + Simpler

- + Memory is up to date

- Intricacy: data value is modified!

- Implication: value in cache will be different from that in memory!

- When do we write the modified data in a cache to the next level?

- Write through: At the time the write happens

- Write back: When the cache line is evicted

- Write-back

- + Can consolidate multiple writes to the same block before eviction. Potentially saves bandwidth between cache and memory + saves energy

- - Need a bit in the tag store indicating the block is "dirty/modified"

- Write-through

- + Simpler

- + Memory is up to date

- More bandwidth intensive; no coalescing of writes

- Intricacy: data value is modified!

- Implication: value in cache will be different from that in memory!

- When do we write the modified data in a cache to the next level?

- Write through: At the time the write happens

- Write back: When the cache line is evicted

- Write-back

- + Can consolidate multiple writes to the same block before eviction. Potentially saves bandwidth between cache and memory + saves energy

- - Need a bit in the tag store indicating the block is "dirty/modified"

- Write-through

- + Simpler

- + Memory is up to date

- - More bandwidth intensive; no coalescing of writes

- Requires transfer of the whole cache line (although only one byte might have been modified)

- Do we allocate a cache line on a write miss?

- Write-allocate: Allocate on write miss

- Non-Write-Allocate: No-allocate on write miss

- Allocate on write miss

- Do we allocate a cache line on a write miss?

- Write-allocate: Allocate on write miss

- Non-Write-Allocate: No-allocate on write miss

- Allocate on write miss

- + Can consolidate writes instead of writing each of them individually to memory

- Do we allocate a cache line on a write miss?

- Write-allocate: Allocate on write miss

- Non-Write-Allocate: No-allocate on write miss

- Allocate on write miss

- + Can consolidate writes instead of writing each of them individually to memory

- + Simpler because write misses can be treated the same way as read misses

- Do we allocate a cache line on a write miss?

- Write-allocate: Allocate on write miss

- Non-Write-Allocate: No-allocate on write miss

- Allocate on write miss

- + Can consolidate writes instead of writing each of them individually to memory

- + Simpler because write misses can be treated the same way as read misses

- Non-allocate

- + Conserves cache space if locality of writes is low (potentially better cache hit rate)

• Separate or Unified?

• Separate or Unified?

• Unified:

- Separate or Unified?

- Unified:

- + Dynamic sharing of cache space: no overprovisioning that might happen with static partitioning (i.e., split Inst and Data caches)

Separate or Unified?

- Unified:

- + Dynamic sharing of cache space: no overprovisioning that might happen with static partitioning (i.e., split Inst and Data caches)

- Instructions and data can thrash each other (i.e., no guaranteed space for either)

Separate or Unified?

#### Unified:

- + Dynamic sharing of cache space: no overprovisioning that might happen with static partitioning (i.e., split Inst and Data caches)

- Instructions and data can thrash each other (i.e., no guaranteed space for either)

- Inst and Data are accessed in different places in the pipeline.

Where do we place the unified cache for fast access?

### Instruction vs. Data Caches

- Separate or Unified?

- Unified:

- + Dynamic sharing of cache space: no overprovisioning that might happen with static partitioning (i.e., split Inst and Data caches)

- Instructions and data can thrash each other (i.e., no guaranteed space for either)

- - Inst and Data are accessed in different places in the pipeline. Where do we place the unified cache for fast access?

- First level caches are almost always split

- Mainly for the last reason above

- Second and higher levels are almost always unified

Which cache line should be replaced?

- Which cache line should be replaced?

- Direct mapped? Only one place!

- Which cache line should be replaced?

- Direct mapped? Only one place!

- Associative caches? Multiple places!

- Which cache line should be replaced?

- Direct mapped? Only one place!

- Associative caches? Multiple places!

- For associative cache:

- Which cache line should be replaced?

- Direct mapped? Only one place!

- Associative caches? Multiple places!

- For associative cache:

- Any invalid cache line first

- Which cache line should be replaced?

- Direct mapped? Only one place!

- Associative caches? Multiple places!

- For associative cache:

- Any invalid cache line first

- If all are valid, consult the replacement policy

- Which cache line should be replaced?

- Direct mapped? Only one place!

- Associative caches? Multiple places!

- For associative cache:

- Any invalid cache line first

- If all are valid, consult the replacement policy

- Randomly pick one????

- Which cache line should be replaced?

- Direct mapped? Only one place!

- Associative caches? Multiple places!

- For associative cache:

- Any invalid cache line first

- If all are valid, consult the replacement policy

- Randomly pick one????

- Ideally: Replace the cache line that's least likely going to be used again

- Which cache line should be replaced?

- Direct mapped? Only one place!

- Associative caches? Multiple places!

- For associative cache:

- Any invalid cache line first

- If all are valid, consult the replacement policy

- Randomly pick one???

- Ideally: Replace the cache line that's least likely going to be used again

- Approximation: Least recently used (LRU)

- Idea: Evict the least recently accessed block

- Challenge: Need to keep track of access ordering of blocks

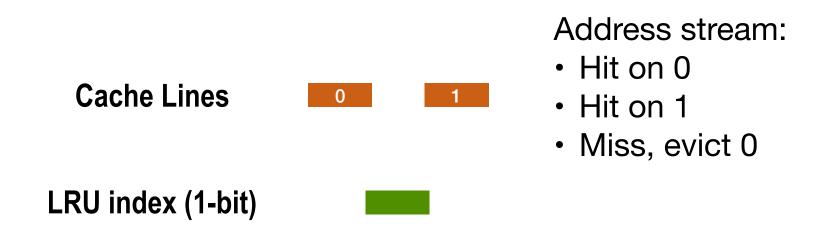

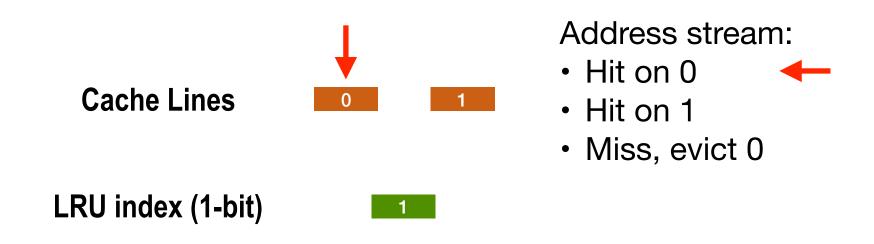

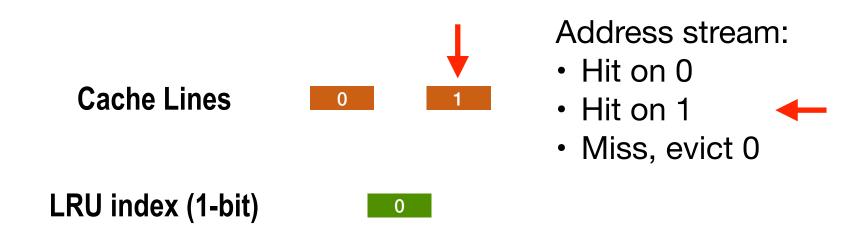

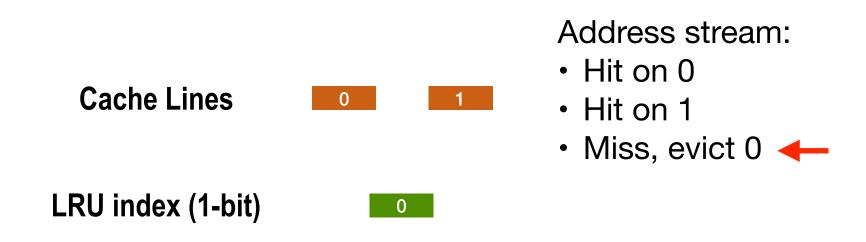

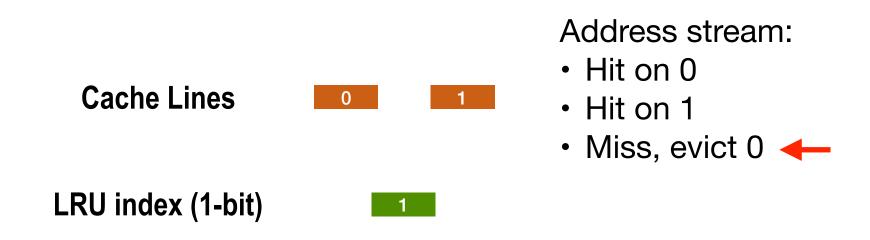

- Question: 2-way set associative cache:

- What do you need to implement LRU perfectly? One bit?

- Idea: Evict the least recently accessed block

- Challenge: Need to keep track of access ordering of blocks

- Question: 2-way set associative cache:

- What do you need to implement LRU perfectly? One bit?

- Idea: Evict the least recently accessed block

- Challenge: Need to keep track of access ordering of blocks

- Question: 2-way set associative cache:

- What do you need to implement LRU perfectly? One bit?

- Idea: Evict the least recently accessed block

- Challenge: Need to keep track of access ordering of blocks

- Question: 2-way set associative cache:

- What do you need to implement LRU perfectly? One bit?

- Idea: Evict the least recently accessed block

- Challenge: Need to keep track of access ordering of blocks

- Question: 2-way set associative cache:

- What do you need to implement LRU perfectly? One bit?

- Idea: Evict the least recently accessed block

- Challenge: Need to keep track of access ordering of blocks

- Question: 2-way set associative cache:

- What do you need to implement LRU perfectly? One bit?

- Hit on 0

- Hit on 2

- Hit on 3

- Miss, evict 1

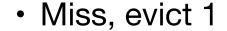

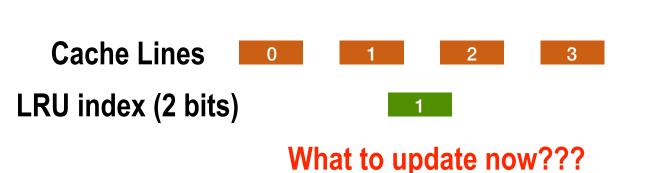

- Question: 4-way set associative cache:

- What do you need to implement LRU perfectly?

- Will the same mechanism work?

- Hit on 0

- Hit on 2

- Hit on 3

- Miss, evict 1

- Question: 4-way set associative cache:

- What do you need to implement LRU perfectly?

- Will the same mechanism work?

- Hit on 0

- Hit on 2

- Hit on 3

- Miss, evict 1

- Question: 4-way set associative cache:

- What do you need to implement LRU perfectly?

- Will the same mechanism work?

- Hit on 0

- Hit on 2

- Hit on 3

- Miss, evict 1

- Question: 4-way set associative cache:

- What do you need to implement LRU perfectly?

- Will the same mechanism work?

- Hit on 0

- Hit on 2

- Hit on 3

- Question: 4-way set associative cache:

- What do you need to implement LRU perfectly?

- Will the same mechanism work?

- Hit on 0

- Hit on 2

- Hit on 3

- Miss, evict 1

- Question: 4-way set associative cache:

- What do you need to implement LRU perfectly?

- Will the same mechanism work?

What to update now???

- Hit on 0

- Hit on 2

- Hit on 3

- Miss, evict 1

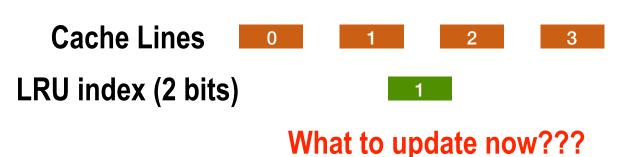

- Question: 4-way set associative cache:

- What do you need to implement LRU perfectly?

- Will the same mechanism work?

- Essentially have to track the ordering of all cache lines

- Hit on 0

- Hit on 2

- Hit on 3

- Miss, evict 1

- Question: 4-way set associative cache:

- What do you need to implement LRU perfectly?

- Will the same mechanism work?

- Essentially have to track the ordering of all cache lines

- How many possible orderings are there?

What to update now????

- Hit on 0

- Hit on 2

- Hit on 3

- Miss, evict 1

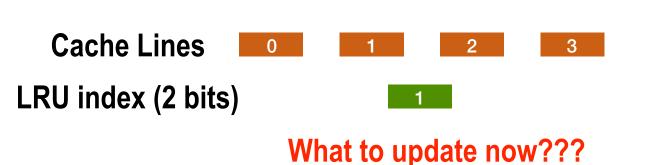

- Question: 4-way set associative cache:

- What do you need to implement LRU perfectly?

- Will the same mechanism work?

- Essentially have to track the ordering of all cache lines

- How many possible orderings are there?

- What are the hardware structures needed?

- Hit on 0

- Hit on 2

- Hit on 3

- Miss, evict 1

- Question: 4-way set associative cache:

- What do you need to implement LRU perfectly?

- Will the same mechanism work?

- Essentially have to track the ordering of all cache lines

- How many possible orderings are there?

- What are the hardware structures needed?

- In reality, true LRU is never implemented. Too complex.

- Hit on 0

- Hit on 2

- Hit on 3

- Miss, evict 1

- Question: 4-way set associative cache:

- What do you need to implement LRU perfectly?

- Will the same mechanism work?

- Essentially have to track the ordering of all cache lines

- How many possible orderings are there?

- What are the hardware structures needed?

- In reality, true LRU is never implemented. Too complex.

- Google Pseudo-LRU

What to update now????

- Hit on 0

- Hit on 2

- Hit on 3

- Miss, evict 1