# CSC 252: Computer Organization Spring 2022: Lecture 5

#### Instructor: Yuhao Zhu

Department of Computer Science University of Rochester

#### Announcement

- Programming Assignment 1 is out

- Details: <u>https://www.cs.rochester.edu/courses/252/</u> <u>spring2022/labs/assignment1.html</u>

- Due on Jan. 30, 11:59 PM (extended)

- You have 3 slip days

| 23  | 24 | 25    | 26 | 27    | 28 | 29 |

|-----|----|-------|----|-------|----|----|

|     |    |       |    | Today |    |    |

| 30  | 31 | Feb 1 | 2  | 3     | 4  | 5  |

| Due |    |       |    |       |    |    |

### Announcement

- Programming assignment 1 is in C language. Seek help from TAs.

- TAs are best positioned to answer your questions about programming assignments!!!

- Programming assignments do NOT repeat the lecture materials. They ask you to synthesize what you have learned from the lectures and work out something new.

# **IEEE 754 Floating Point Standard**

• Single precision: 32 bits

• Double precision: 64 bits

#### • In C language

- •float single precision

- •double double precision

# Floating Point in C

Fixed point (implicit binary point)

> SP floating point DP floating point

| C Data<br>Type | Bits | Max Value                                   | Max Value<br>(Decimal)   |

|----------------|------|---------------------------------------------|--------------------------|

| char           | 8    | 2 <sup>7</sup> - 1                          | 127                      |

| short          | 16   | 2 <sup>15</sup> - 1                         | 32767                    |

| int            | 32   | 2 <sup>31</sup> - 1                         | 2147483647               |

| long           | 64   | 2 <sup>63</sup> - 1                         | ~9.2 × 10 <sup>18</sup>  |

| float          | 32   | (2 - 2 <sup>-23</sup> ) × 2 <sup>127</sup>  | ~3.4 × 10 <sup>38</sup>  |

| double         | 64   | (2 - 2 <sup>-52</sup> ) × 2 <sup>1023</sup> | ~1.8 × 10 <sup>308</sup> |

**32-bit Machine**

| Floating Point in C<br>C Data<br>Type |        |    | 32-bit Machine                              |                          |  |

|---------------------------------------|--------|----|---------------------------------------------|--------------------------|--|

|                                       |        |    | Max Value                                   | Max Value<br>(Decimal)   |  |

| ſ                                     | char   | 8  | 2 <sup>7</sup> - 1                          | 127                      |  |

| Fixed point                           | short  | 16 | 2 <sup>15</sup> - 1                         | 32767                    |  |

| (implicit binary point)               | int    | 32 | 2 <sup>31</sup> - 1                         | 2147483647               |  |

|                                       | long   | 64 | 2 <sup>63</sup> - 1                         | ~9.2 × 10 <sup>18</sup>  |  |

| SP floating point                     | float  | 32 | (2 - 2 <sup>-23</sup> ) × 2 <sup>127</sup>  | ~3.4 × 10 <sup>38</sup>  |  |

| DP floating point                     | double | 64 | (2 - 2 <sup>-52</sup> ) × 2 <sup>1023</sup> | ~1.8 × 10 <sup>308</sup> |  |

• To represent 2<sup>31</sup> in fixed-point, you need at least 32 bits

- Because fixed-point is a weighted positional representation

- In floating-point, we directly encode the exponent

- Floating point is based on scientific notation

- Encoding 31 only needs 7 bits in the exp field

#### • double/float $\rightarrow$ int

- Truncates fractional part

- Like rounding toward zero

- Not defined when out of range or NaN

#### • double/float $\rightarrow$ int

- Truncates fractional part

- Like rounding toward zero

- Not defined when out of range or NaN

- int  $\rightarrow$  float

#### • double/float $\rightarrow$ int

- Truncates fractional part

- Like rounding toward zero

- Not defined when out of range or NaN

#### • int $\rightarrow$ float

Can't guarantee exact casting. Will round according to rounding mode

#### • double/float $\rightarrow$ int

- Truncates fractional part

- Like rounding toward zero

- Not defined when out of range or NaN

#### • int $\rightarrow$ float

Can't guarantee exact casting. Will round according to rounding mode

| S | exp   | frac   |

|---|-------|--------|

| 1 | 8-bit | 23-bit |

• int  $\rightarrow$  double

| S | exp    | frac   |

|---|--------|--------|

| 1 | 11-bit | 52-bit |

#### • double/float $\rightarrow$ int

- Truncates fractional part

- Like rounding toward zero

- Not defined when out of range or NaN

#### • int $\rightarrow$ float

Can't guarantee exact casting. Will round according to rounding mode

| S | exp   | frac   |

|---|-------|--------|

| 1 | 8-bit | 23-bit |

- int → double

- Exact conversion

| S | exp    | frac   |

|---|--------|--------|

| 1 | 11-bit | 52-bit |

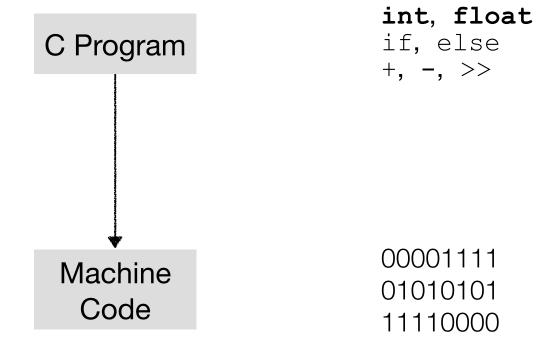

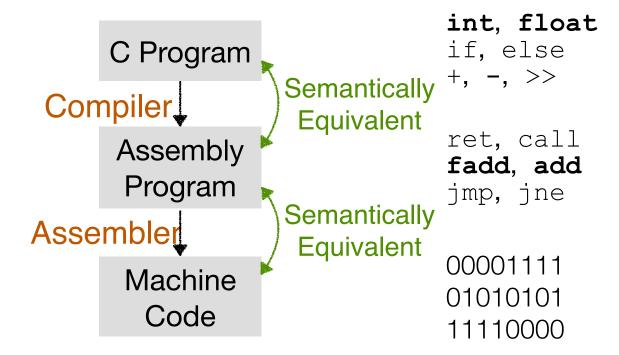

#### C Program

int, float

if, else

+, -, >>

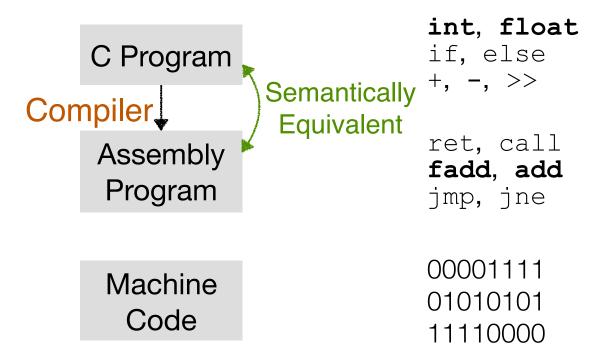

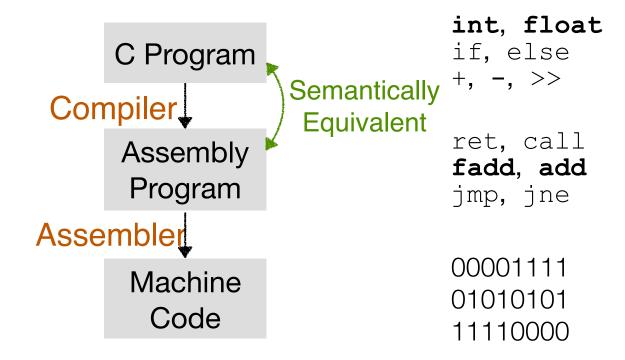

C Program Compiler Assembly Program

> Machine Code

int, float

if, else

+, -, >>

ret, call **fadd, add** jmp, jne

00001111 01010101 11110000

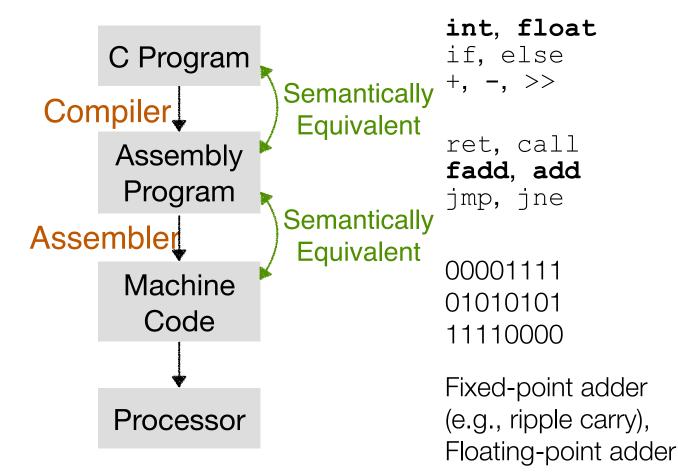

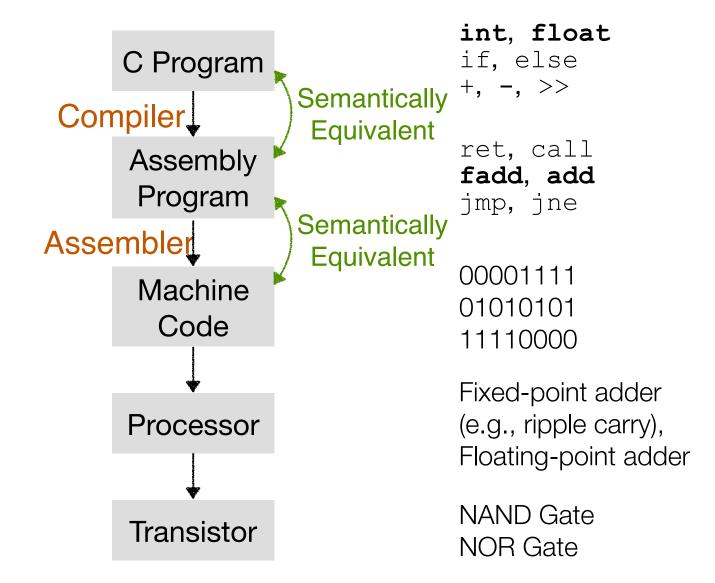

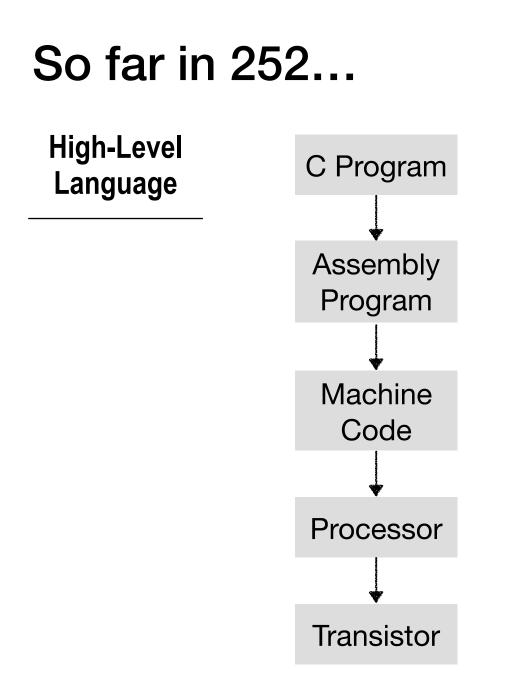

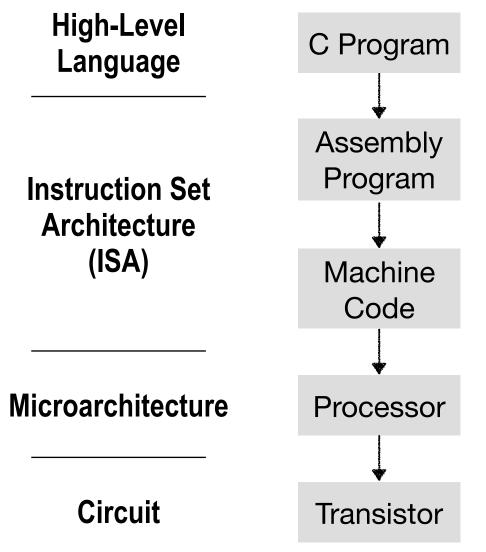

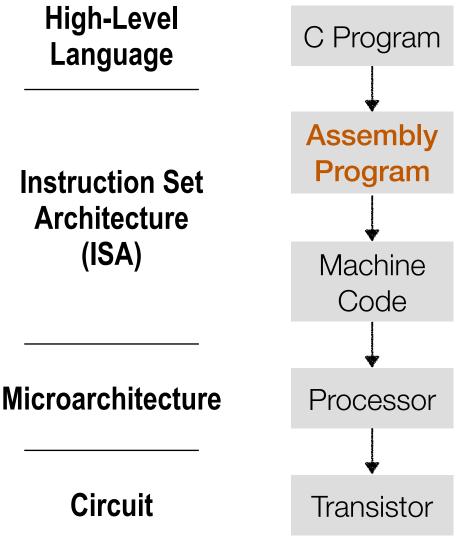

**High-Level** C Program Language Assembly Program **Instruction Set** Architecture (ISA) Machine Code Processor Transistor

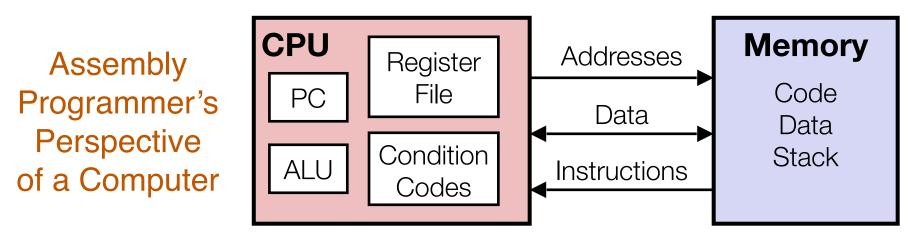

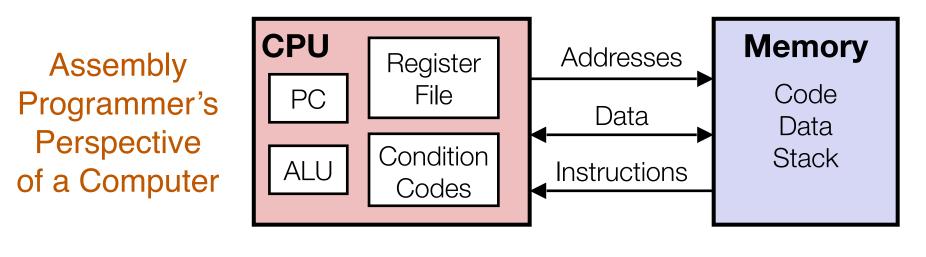

• ISA: Software programmers' view of a computer

- Provide all info for someone wants to write assembly/machine code

- "Contract" between assembly/ machine code and processor

**High-Level** C Program Language Assembly Program Instruction Set Architecture (ISA) Machine Code Processor

Transistor

- ISA: Software programmers' view of a computer

- Provide all info for someone wants to write assembly/machine code

- "Contract" between assembly/ machine code and processor

- Processors execute machine code (binary). Assembly program is merely a text representation of machine code

- ISA: Software programmers' view of a computer

- Provide all info for someone wants to write assembly/machine code

- "Contract" between assembly/ machine code and processor

- Processors execute machine code (binary). Assembly program is merely a text representation of machine code

- Microarchitecture: Hardware implementation of the ISA (with the help of circuit technologies)

# This Module (4 Lectures)

- Assembly Programming

- Explain how various C constructs are implemented in assembly code

- Effectively translating from C to assembly program manually

- Helps us understand how compilers work

- Helps us understand how assemblers work

- Microarchitecture is the topic of the next module

#### **Today: Assembly Programming I: Basics**

- Different ISAs and history behind them

- C, assembly, machine code

- Move operations (and addressing modes)

- There used to be many ISAs

- x86, ARM, Power/PowerPC, Sparc, MIPS, IA64, z

- Very consolidated today: ARM for mobile, x86 for others

- There used to be many ISAs

- x86, ARM, Power/PowerPC, Sparc, MIPS, IA64, z

- Very consolidated today: ARM for mobile, x86 for others

- There are even more microarchitectures

- Apple/Samsung/Qualcomm have their own microarchitecture (implementation) of the ARM ISA

- Intel and AMD have different microarchitectures for x86

- There used to be many ISAs

- x86, ARM, Power/PowerPC, Sparc, MIPS, IA64, z

- Very consolidated today: ARM for mobile, x86 for others

- There are even more microarchitectures

- Apple/Samsung/Qualcomm have their own microarchitecture (implementation) of the ARM ISA

- Intel and AMD have different microarchitectures for x86

- ISA is lucrative business: ARM's Business Model

- Patent the ISA, and then license the ISA

- Every implementer pays a royalty to ARM

- Apple/Samsung pays ARM whenever they sell a smartphone

The ARM Diaries, Part 1: How ARM's Business Model Works: <u>https://www.anandtech.com/show/7112/</u> <u>the-arm-diaries-part-1-how-arms-business-model-works</u>

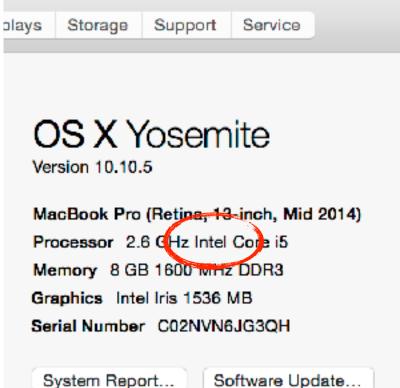

# Intel x86 ISA

• Dominate laptop/desktop/cloud market

# Intel x86 ISA

Dominate laptop/desktop/cloud market

Software Update...

# Intel x86 ISA

• Dominate laptop/desktop/cloud market

# Aside: Dynamic Binary Translation

#### macOS Monterey

Version 12.0.1

MacBook Pro (16-inch, 2021) Chip Apple M1 Pro Memory 16 GB Serial Number VQ4GVYVN6F

- Apple M1 is based on the Arm ISA. A program compiled to x86 ISA is dynamically translated to Arm ISA by Rosetta.

- Not the first time Apple plays this trick.

Fast performance Translated at install time Dynamic translation for JITs Transparent to user

#### **Aside: Dynamic Binary Translation**

#### **Circa 2006: PowerPC to x86 translation**

# Rosetta

Translates PowerPC to Intel

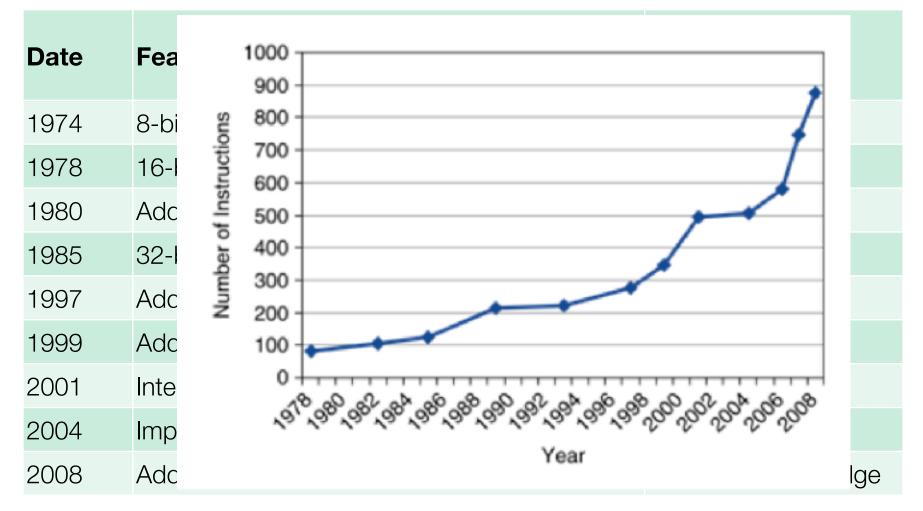

# Intel x86 ISA Evolution (Milestones)

• Evolutionary design: Added more features as time goes on

# Intel x86 ISA Evolution (Milestones)

• Evolutionary design: Added more features as time goes on

| Date | Feature                                            | Notable<br>Implementation |

|------|----------------------------------------------------|---------------------------|

| 1974 | 8-bit ISA                                          | 8080                      |

| 1978 | 16-bit ISA (Basis for IBM PC & DOS)                | 8086                      |

| 1980 | Add Floating Point instructions                    | 8087                      |

| 1985 | 32-bit ISA (Refer to as IA32)                      | 386                       |

| 1997 | Add Multi-Media eXtension (MMX)                    | Pentium/MMX               |

| 1999 | Add Streaming SIMD Extension (SSE)                 | Pentium III               |

| 2001 | Intel's first attempt at 64-bit ISA (IA64, failed) | Itanium                   |

| 2004 | Implement AMD's 64-bit ISA (x86-64, AMD64)         | Pentium 4E                |

| 2008 | Add Advanced Vector Extension (AVE)                | Core i7 Sandy Bridge      |

# Intel x86 ISA Evolution (Milestones)

• Evolutionary design: Added more features as time goes on

# **Backward Compatibility**

- Binary executable generated for an older processor can execute on a newer processor

- Allows legacy code to be executed on newer machines

- Buy new machines without changing the software

- x86 is backward compatible up until 8086 (16-bit ISA)

- i.e., an 8086 binary executable can be executed on any of today's x86 machines

- Great for users, nasty for processor implementers

- Every instruction you put into the ISA, you are stuck with it FOREVER

#### Historically

- AMD build processors for x86 ISA

- A little bit slower, a lot cheaper

#### •Then

- Recruited top circuit designers from Digital Equipment Corp. and other downward trending companies

- Developed x86-64, their own 64-bit x86 extension to IA32

- Built first 1 GHz CPU

- Intel felt hard to admit mistake or that AMD was better

- 2004: Intel Announces EM64T extension to IA32

- Almost identical to x86-64!

- Today's 64-bit x86 ISA is basically AMD's original proposal

•Today: Holding up not too badly

•Today: Holding up not too badly

•Today: Holding up not too badly

# Our Coverage

- IA32

- The traditional x86

- 2<sup>nd</sup> edition of the textbook

- x86-64

- The standard

- CSUG machine

- 3<sup>rd</sup> edition of the textbook

- Our focus

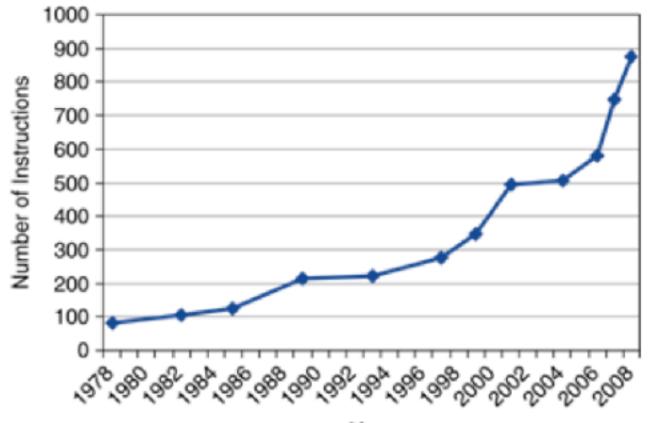

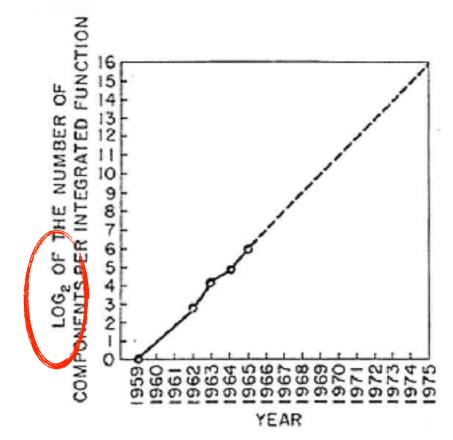

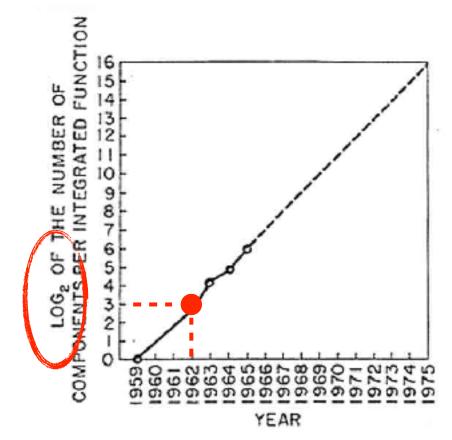

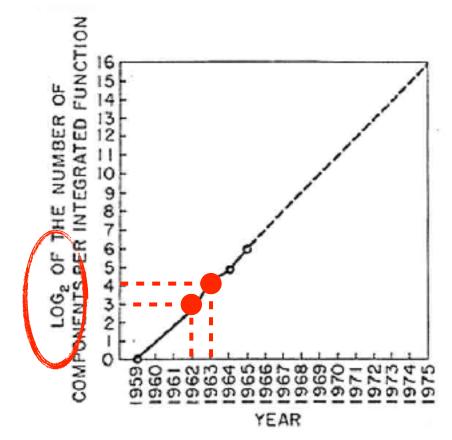

• More instructions typically require more transistors to implement

• More instructions typically require more transistors to implement

Year

• More instructions typically require more transistors to implement

• More instructions require more transistors to implement

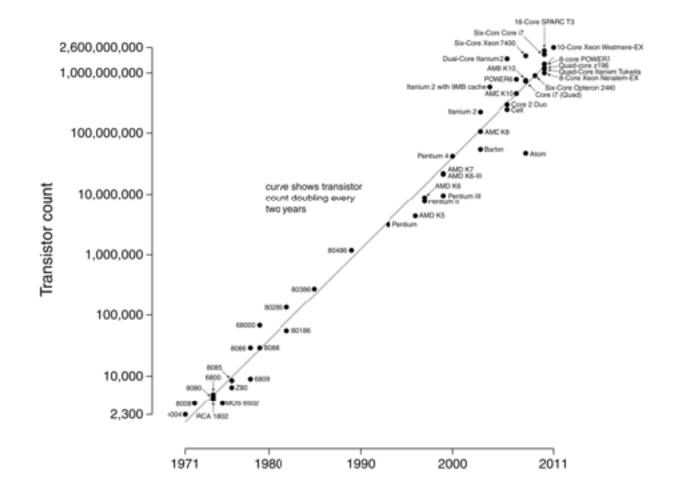

- More instructions require more transistors to implement

- Gordon Moore in 1965 predicted that the number of transistors doubles every year

- More instructions require more transistors to implement

- Gordon Moore in 1965 predicted that the number of transistors doubles every year

- More instructions require more transistors to implement

- Gordon Moore in 1965 predicted that the number of transistors doubles every year

- More instructions require more transistors to implement

- Gordon Moore in 1965 predicted that the number of transistors doubles every year

- More instructions require more transistors to implement

- Gordon Moore in 1965 predicted that the number of transistors doubles every year

- In 1975 he revised the prediction to doubling every 2 years

- More instructions require more transistors to implement

- Gordon Moore in 1965 predicted that the number of transistors doubles every year

- In 1975 he revised the prediction to doubling every 2 years

- Today's widely-known Moore's Law: number of transistors double about every 18 months

- Moore never used the number 18...

• Question: why is transistor count increasing but computers are becoming smaller?

- Question: why is transistor count increasing but computers are becoming smaller?

- Because transistors are becoming smaller

- Question: why is transistor count increasing but computers are becoming smaller?

- Because transistors are becoming smaller

- ~1.4x smaller each dimension(1.4<sup>2</sup> ~ 2)

- Question: why is transistor count increasing but computers are becoming smaller?

- Because transistors are becoming smaller

- ~1.4x smaller each dimension(1.4<sup>2</sup> ~ 2)

- Moore's Law is:

- Question: why is transistor count increasing but computers are becoming smaller?

- Because transistors are becoming smaller

- ~1.4x smaller each dimension(1.4<sup>2</sup> ~ 2)

- Moore's Law is:

- A law of physics?

• Question: why is transistor count increasing but computers are becoming smaller?

- Because transistors are becoming smaller

- ~1.4x smaller each dimension(1.4<sup>2</sup> ~ 2)

- Moore's Law is:

- A law of physics?

• Question: why is transistor count increasing but computers are becoming smaller?

- Because transistors are becoming smaller

- ~1.4x smaller each dimension(1.4<sup>2</sup> ~ 2)

- Moore's Law is:

- A law of physics?

- A law of math?

• Question: why is transistor count increasing but computers are becoming smaller?

No

- Because transistors are becoming smaller

- ~1.4x smaller each dimension(1.4<sup>2</sup> ~ 2)

- Moore's Law is:

- A law of physics?

- A law of math?

• Question: why is transistor count increasing but computers are becoming smaller?

No

- Because transistors are becoming smaller

- ~1.4x smaller each dimension(1.4<sup>2</sup> ~ 2)

- Moore's Law is:

- A law of physics?

- A law of math?

- A law of economy?

• Question: why is transistor count increasing but computers are becoming smaller?

Yes

- Because transistors are becoming smaller

- ~1.4x smaller each dimension(1.4<sup>2</sup> ~ 2)

- Moore's Law is:

- A law of physics?

No

- A law of math?

No

- A law of economy?

ars TECHNICA

BIZ & IT TECH SCIENCE POLICY CARS GAMING & CULTURE

#### TECH-

#### Transistors will stop shrinking in 2021, but Moore's law will live on

Final semiconductor industry roadmap says the future is 3D packaging and cooling.

The first problem has been known about for a long while. Basically, starting at around the 65nm node in 2006, the economic gains from moving to smaller transistors have been slowly dribbling away. Previously, moving to a smaller node meant you could cram tons more chips onto a single silicon wafer, at a reasonably small price increase. With recent nodes like 22 or 14nm, though, there are so many additional steps required that it costs a lot more to manufacture a completed wafer—not to mention additional costs for things like package-on-package (PoP) and through-silicon vias (TSV) packaging.

ars TECHNICA

BIZ & IT TECH SCIENCE POLICY CARS GAMING & CULTURE

#### TECH-

#### Transistors will stop shrinking in 2021, but Moore's law will live on

Final semiconductor industry roadmap says the future is 3D packaging and cooling.

The first problem has been known about for a long while. Basically, starting at around the 65nm node in 2006, the economic gains from moving to smaller transistors have been slowly dribbling away. Previously, moving to a smaller node meant you could cram tons more chips onto a single silicon wafer, at a reasonably small price increase. With recent nodes like 22 or 14nm, though, there are so many additional steps required that it costs a lot more to manufacture a completed wafer—not to mention additional costs for things like package-on-package (PoP) and through-silicon vias (TSV) packaging.

• Question: why is transistor count increasing but computers are becoming smaller?

No

No

Yes

- Because transistors are becoming smaller

- ~1.4x smaller each dimension(1.4<sup>2</sup> ~ 2)

- Moore's Law is:

- A law of physics?

- A law of math?

- A law of economy?

- A law of psychology?

- Question: why is transistor count increasing but computers are becoming smaller?

- Because transistors are becoming smaller

- ~1.4x smaller each dimension(1.4<sup>2</sup> ~ 2)

- Moore's Law is:

- A law of physics?

No

- A law of math?

No

- A law of economy?

Yes

- A law of psychology?

Yes

#### **Today: Assembly Programming I: Basics**

- Different ISAs and history behind them

- Memory, C, assembly, machine code

- Move operations (and addressing modes)

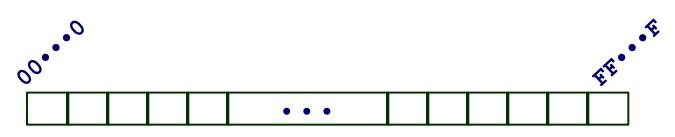

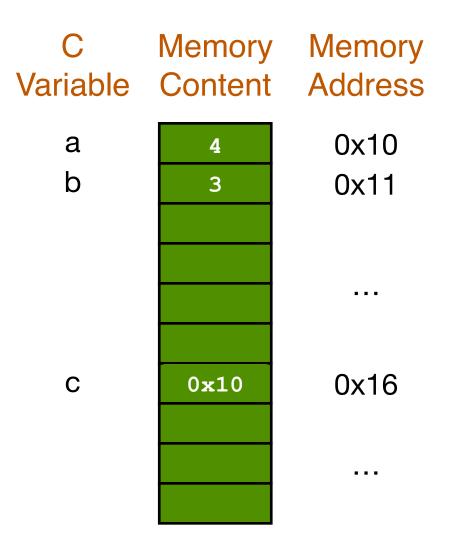

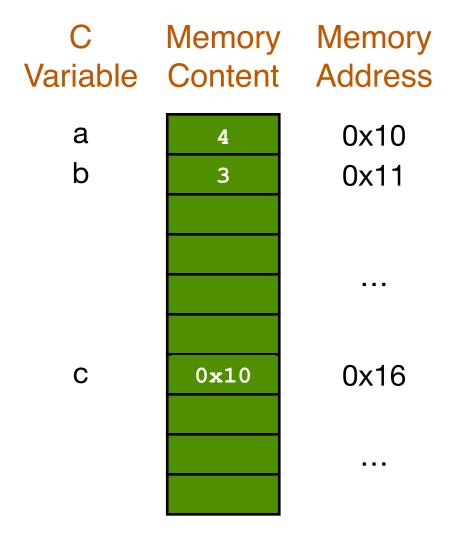

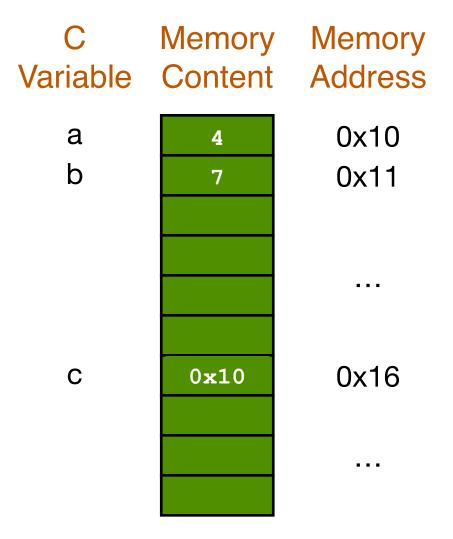

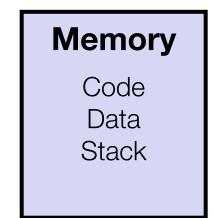

## **Byte-Oriented Memory Organization**

- Data in computers are stored in "memory"

- Conceptually, envision it as a very large array of bytes: byte-addressable

#### • Each byte has an address

- An address is like an index into that array

- A pointer variable is a variable that stores an address

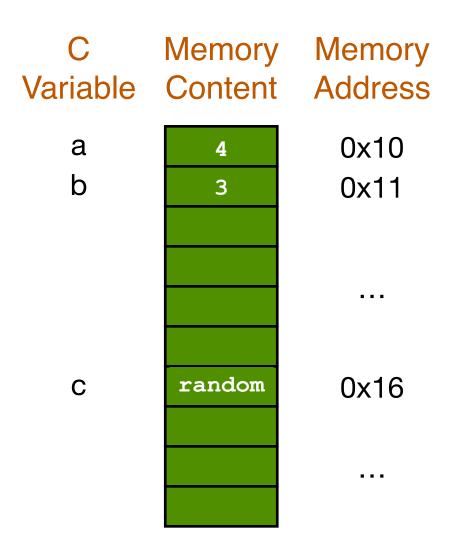

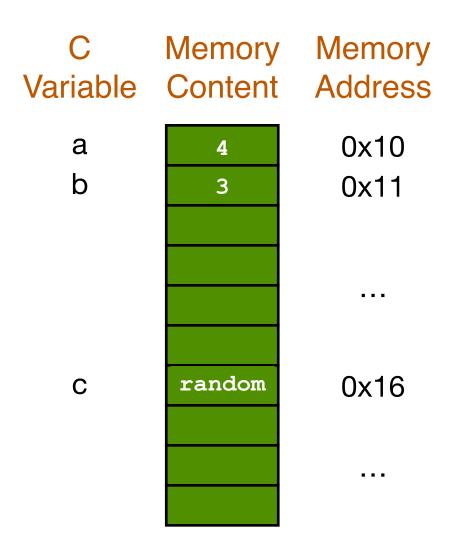

#### How Does Pointer Work in C???

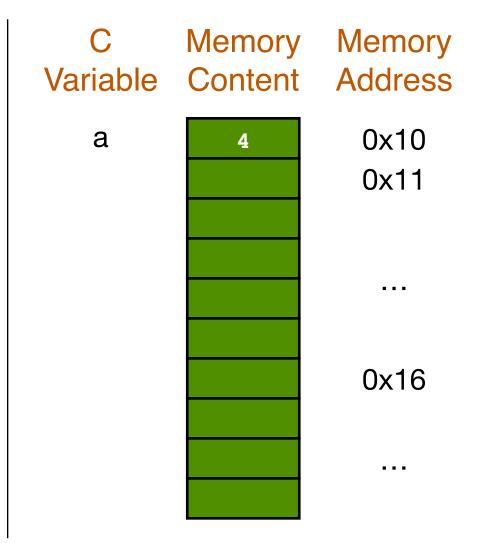

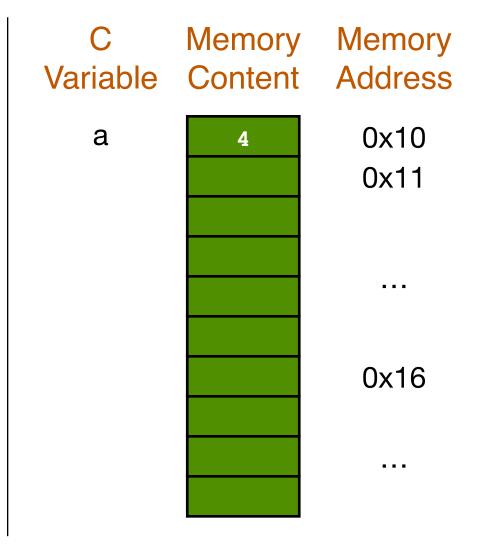

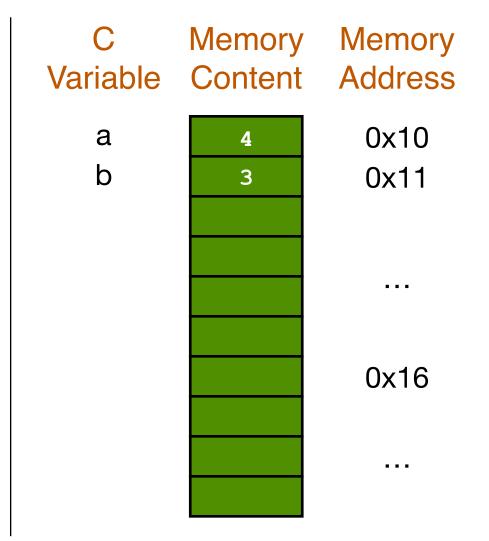

- char a = 4;

- char b = 3;

- char\* c;

- c = &a;

- b += (\*c);

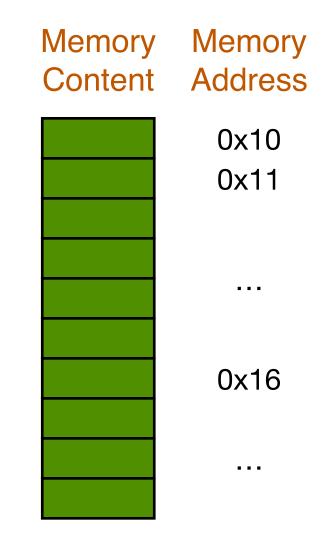

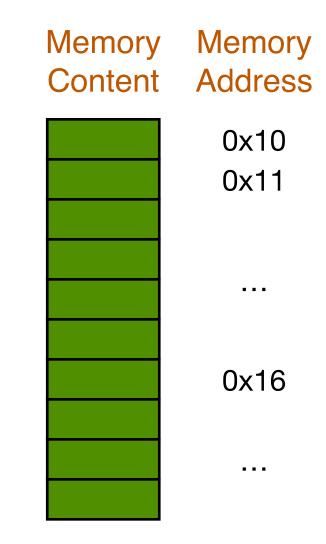

#### How Does Pointer Work in C???

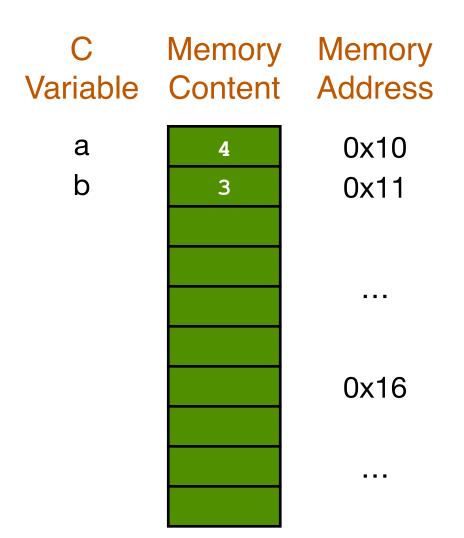

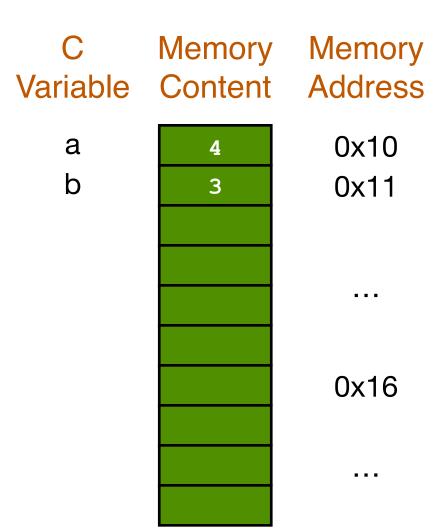

char a = 4; char b = 3; char\* c; c = &a; b += (\*c);

#### How Does Pointer Work in C???

char a = 4; char b = 3; char\* c; c = &a; b += (\*c);

| <br>char $a = 4;$ |

|-------------------|

| char $b = 3;$     |

| char* c;          |

| c = &a            |

| b += (*c);        |

char a = 4; char b = 3; char\* c; c = &a; b += (\*c);

char a = 4; char b = 3; char\* c; c = &a; b += (\*c);

char a = 4;

char

$$b = 3;$$

----> char\* c;

$$c = \&a$$

b += (\*c);

char a = 4;

char

$$b = 3;$$

----> char\* c;

c = &a;

- b += (\*c);

- The content of a pointer variable is memory address.

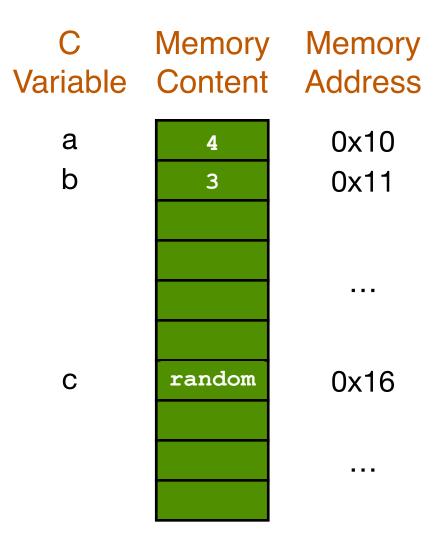

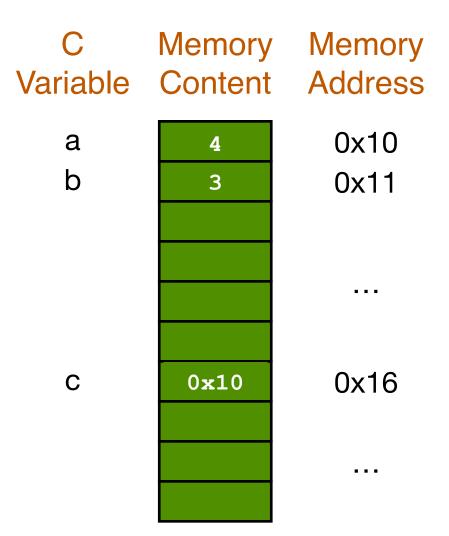

char a = 4;

char

$$b = 3;$$

char\* c;

c = &a;

- b += (\*c);

- The content of a pointer variable is memory address.

- char a = 4; char b = 3; char\* c; c = &a; b += (\*c);

- The content of a pointer variable is memory address.

- char a = 4; char b = 3; char\* c; c = &a; b += (\*c);

- The content of a pointer variable is memory address.

- The '&' operator (address-of operator) returns the memory address of a variable.

- char a = 4; char b = 3; char\* c; char\* c; c = &a; b += (\*c);

- The content of a pointer variable is memory address.

- The '&' operator (address-of operator) returns the memory address of a variable.

char a = 4; char b = 3; char\* c; c = &a; b += (\*c);

- The content of a pointer variable is memory address.

- The '&' operator (address-of operator) returns the memory address of a variable.

- char a = 4; char b = 3; char\* c; c = &a; b += (\*c);

- The content of a pointer variable is memory address.

- The '&' operator (address-of operator) returns the memory address of a variable.

- The '\*' operator returns the content stored at the memory location pointed by the pointer variable (dereferencing)

char a = 4; char b = 3; char\* c; c = &a; b += (\*c);

- The content of a pointer variable is memory address.

- The '&' operator (address-of operator) returns the memory address of a variable.

- The '\*' operator returns the content stored at the memory location pointed by the pointer variable (dereferencing)

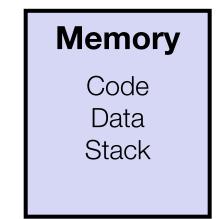

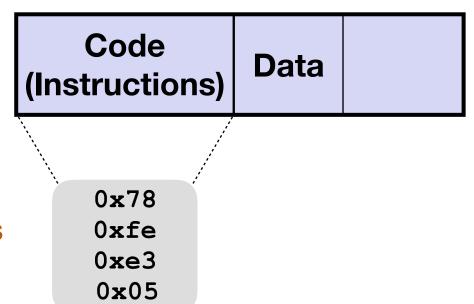

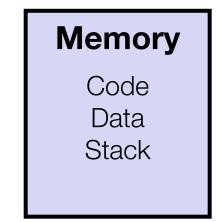

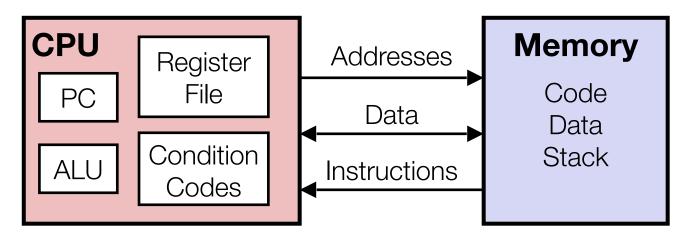

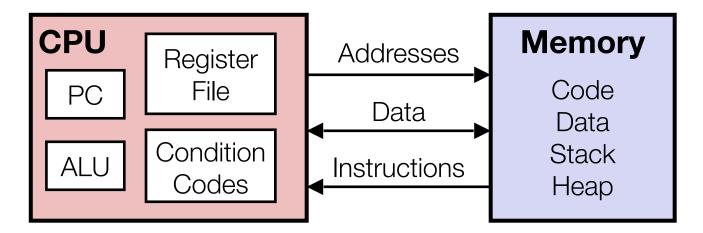

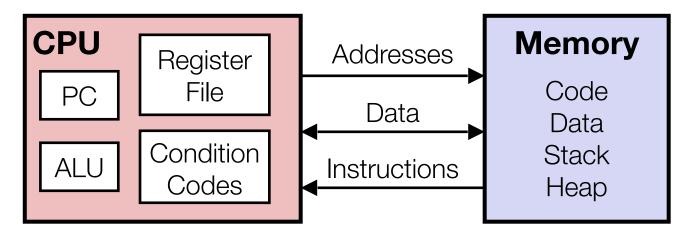

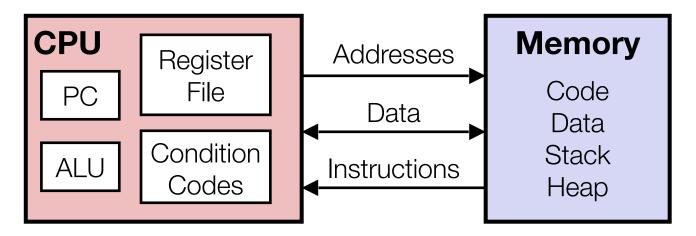

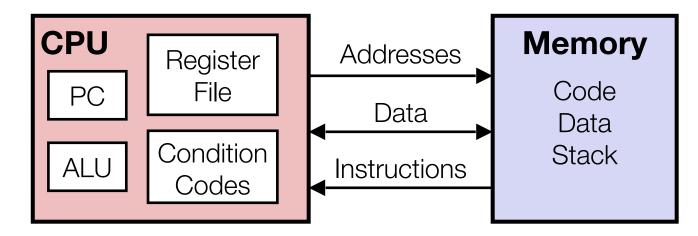

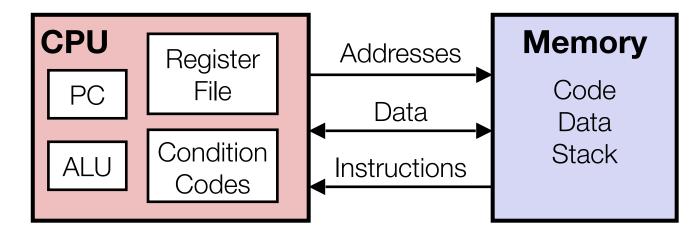

- (Byte Addressable) Memory

- Code: instructions

- Data

- Stack to support function call

- (Byte Addressable) Memory

- Code: instructions

- Data

- Stack to support function call

|  | Data |  |

|--|------|--|

|--|------|--|

- (Byte Addressable) Memory

- Code: instructions

- Data

- Stack to support function call

| Data          |  |

|---------------|--|

|               |  |

| 0 <b>x</b> 53 |  |

| 0 <b>x</b> 48 |  |

| <b>0x89</b>   |  |

| 0xd3          |  |

- (Byte Addressable) Memory

- Code: instructions

- Data

- Stack to support function call

```

Instruction is the fundamental

unit of work.

All instructions are encoded as

bits (just like data!)

```

- (Byte Addressable) Memory

- Code: instructions

- Data

- Stack to support function call

| Code<br>(Instructions) | Data | Stack         |

|------------------------|------|---------------|

|                        |      |               |

|                        | ÷    | 0x53          |

|                        |      | 0 <b>x</b> 48 |

|                        |      | 0x89          |

|                        |      | 0xd3          |

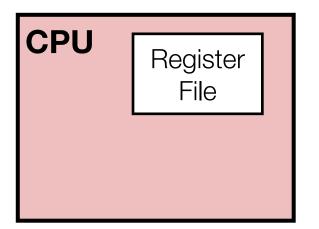

- (Byte Addressable) Memory

- Code: instructions

- Data

- Stack to support function call

- Register file

- Faster memory (e.g., 0.5 ns vs. 15 ns)

- Small memory (e.g., 128 B vs. 16 GB)

- Heavily used program data

| 8 Bytes      |              |  |

|--------------|--------------|--|

| %rax         | % <b>r8</b>  |  |

| %rbx         | % <b>r9</b>  |  |

| %rcx         | 8 <b>r10</b> |  |

| %rdx         | 8 <b>r11</b> |  |

| % <b>rsi</b> | % <b>r12</b> |  |

| %rdi         | % <b>r13</b> |  |

| %rsp         | 8 <b>r14</b> |  |

| %rbp         | %r15         |  |

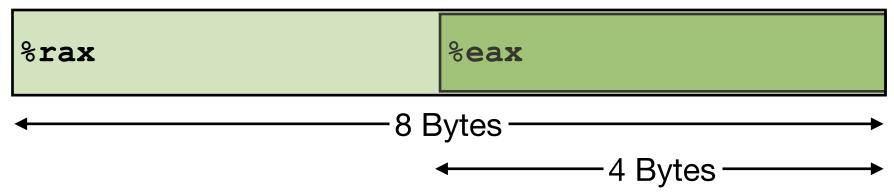

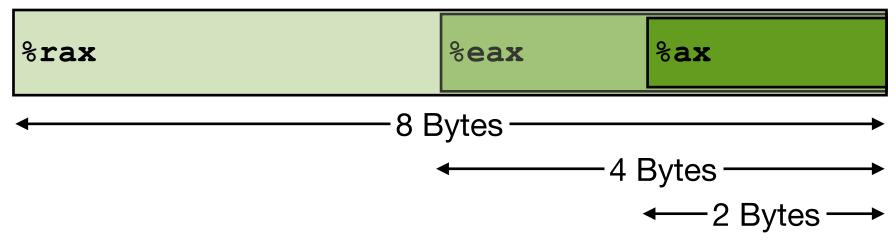

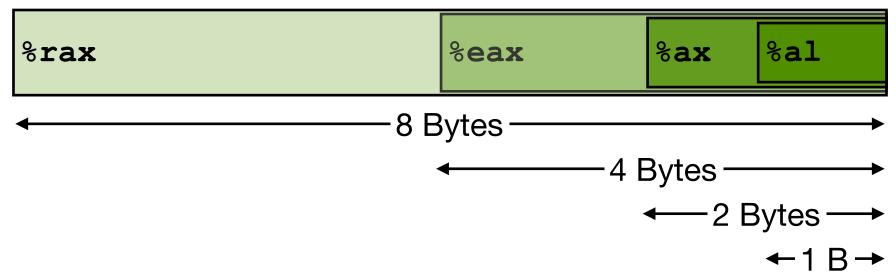

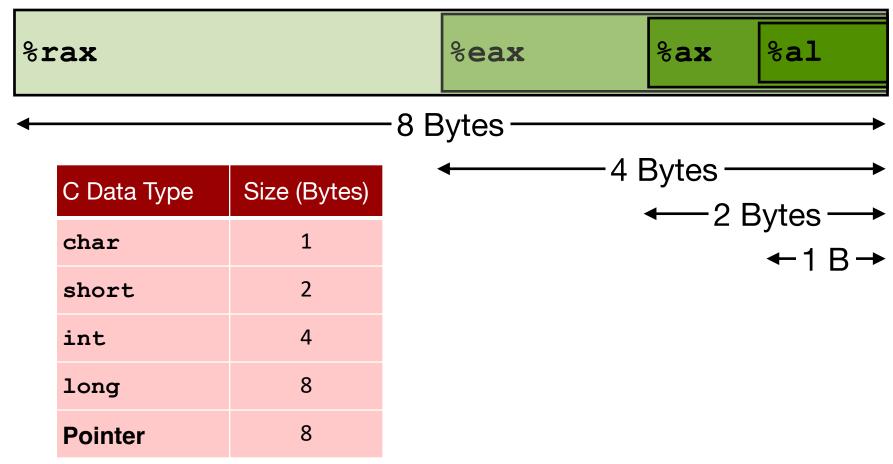

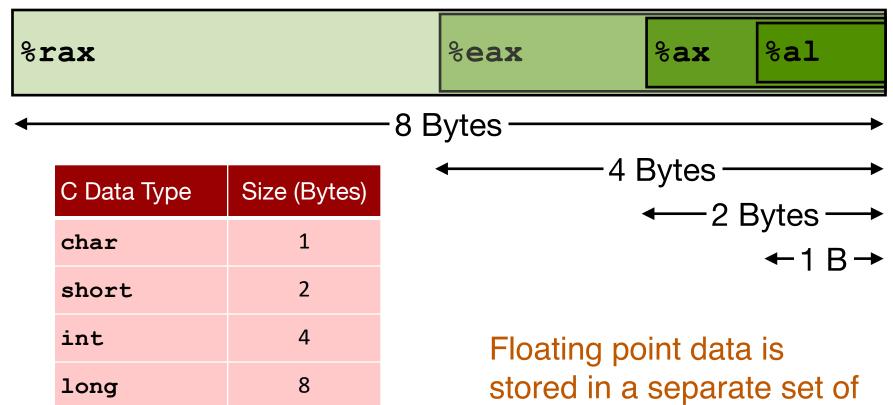

• Lower-half of each register can be independently addressed (until 1 bytes)

%rax

#### 8 Bytes

8

Pointer

• Lower-half of each register can be independently addressed (until 1 bytes)

register file

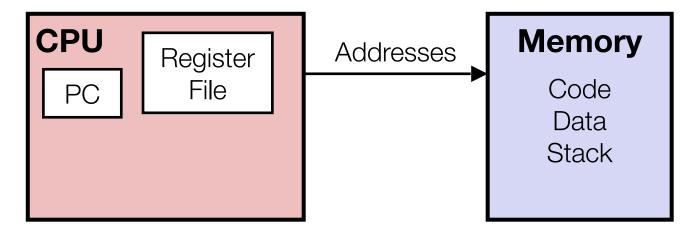

- (Byte Addressable) Memory

- Code: instructions

- Data

- Stack to support function call

- Register file

- Faster memory (e.g., 0.5 ns vs. 15 ns)

- Small memory (e.g., 128 B vs. 16 GB)

- Heavily used program data

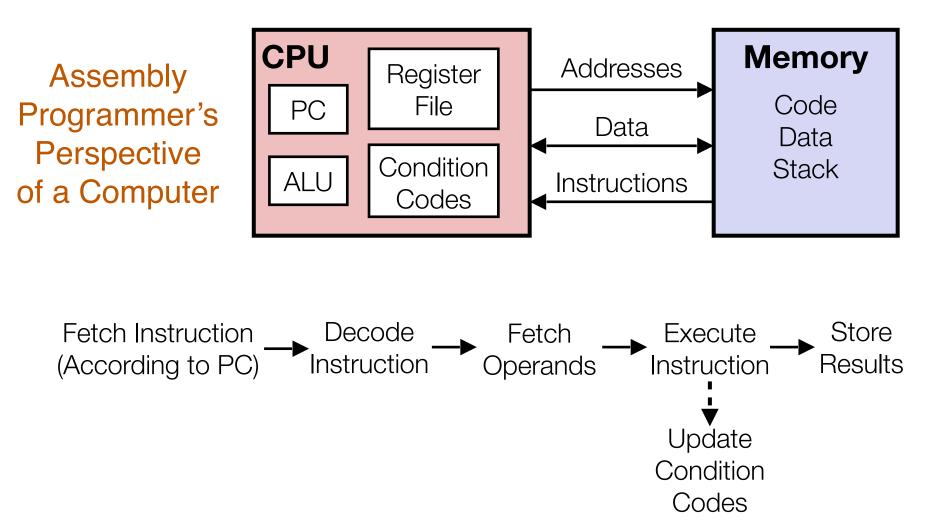

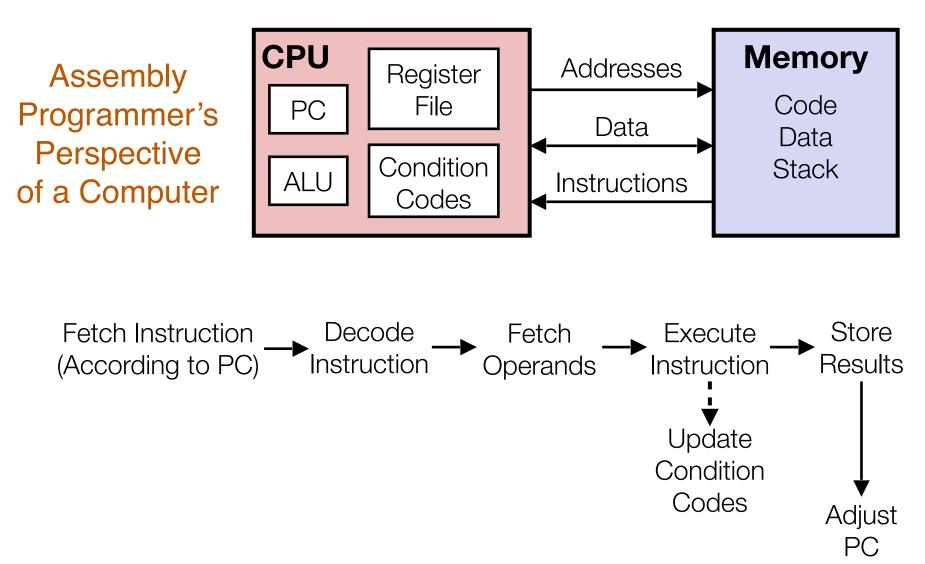

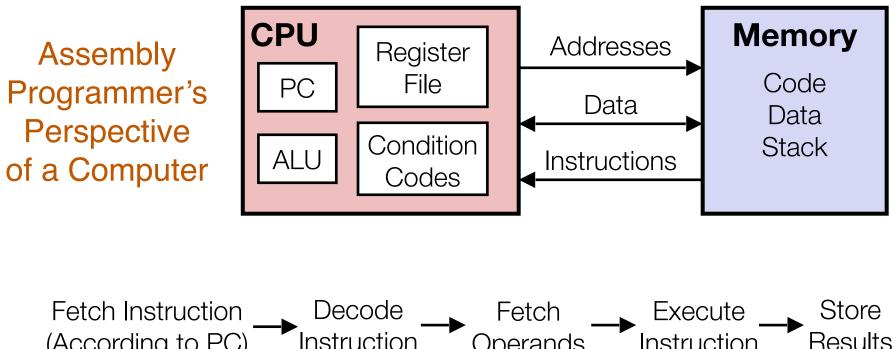

- (Byte Addressable) Memory

- Code: instructions

- Data

- Stack to support function call

- Register file

- Faster memory (e.g., 0.5 ns vs. 15 ns)

- Small memory (e.g., 128 B vs. 16 GB)

- Heavily used program data

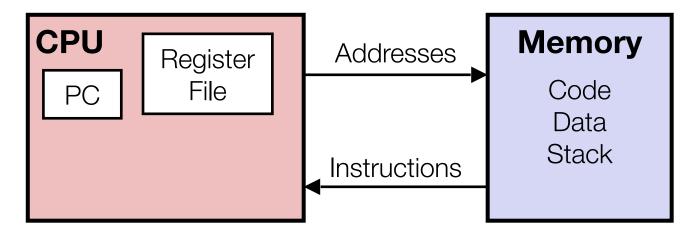

- PC: Program counter

- A special register containing address of next instruction

- Called "RIP" in x86-64

- (Byte Addressable) Memory

- Code: instructions

- Data

- Stack to support function call

- Register file

- Faster memory (e.g., 0.5 ns vs. 15 ns)

- Small memory (e.g., 128 B vs. 16 GB)

- Heavily used program data

- PC: Program counter

- A special register containing address of next instruction

- Called "RIP" in x86-64

- (Byte Addressable) Memory

- Code: instructions

- Data

- Stack to support function call

- Register file

- Faster memory (e.g., 0.5 ns vs. 15 ns)

- Small memory (e.g., 128 B vs. 16 GB)

- Heavily used program data

- PC: Program counter

- A special register containing address of next instruction

- Called "RIP" in x86-64

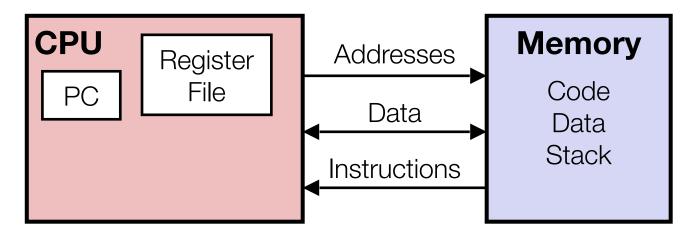

- (Byte Addressable) Memory

- Code: instructions

- Data

- Stack to support function call

- Register file

- Faster memory (e.g., 0.5 ns vs. 15 ns)

- Small memory (e.g., 128 B vs. 16 GB)

- Heavily used program data

- PC: Program counter

- A special register containing address of next instruction

- Called "RIP" in x86-64

- (Byte Addressable) Memory

- Code: instructions

- Data

- Stack to support function call

- Register file

- Faster memory (e.g., 0.5 ns vs. 15 ns)

- Small memory (e.g., 128 B vs. 16 GB)

- Heavily used program data

- PC: Program counter

- A special register containing address of next instruction

- Called "RIP" in x86-64

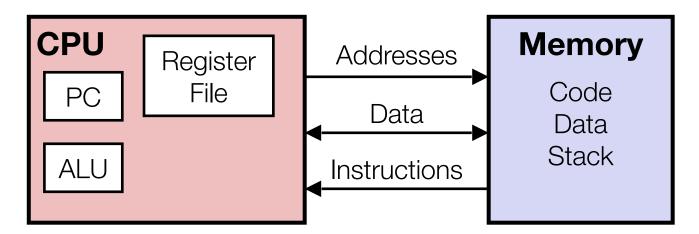

- Arithmetic logic unit (ALU)

- Where computation happens

- (Byte Addressable) Memory

- Code: instructions

- Data

- Stack to support function call

- Register file

- Faster memory (e.g., 0.5 ns vs. 15 ns)

- Small memory (e.g., 128 B vs. 16 GB)

- Heavily used program data

- PC: Program counter

- A special register containing address of next instruction

- Called "RIP" in x86-64

- Arithmetic logic unit (ALU)

- Where computation happens

- Condition codes

- Store status information about most recent arithmetic or logical operation

- Used for conditional branch

# **Assembly Program Instructions**

## **Assembly Program Instructions**

CPU Memory Addresses Assembly Register Code File PC **Programmer's** Data Data Perspective Condition Stack ALU Instructions of a Computer Codes Heap

- Compute Instruction: Perform arithmetics on register or memory data

- addq %eax, %ebx

- C constructs: +, -, >>, etc.

# **Assembly Program Instructions**

Assembly Programmer's Perspective of a Computer

- Compute Instruction: Perform arithmetics on register or memory data

- addq %eax, %ebx

- C constructs: +, -, >>, etc.

- Data Movement Instruction: Transfer data between memory and register

- movq %eax, (%ebx)

# **Assembly Program Instructions**

Assembly Programmer's Perspective of a Computer

- Compute Instruction: Perform arithmetics on register or memory data

- addq %eax, %ebx

- C constructs: +, -, >>, etc.

- Data Movement Instruction: Transfer data between memory and register

- movq %eax, (%ebx)

- Control Instruction: Alter the sequence of instructions (by changing PC)

- jmp, call

- C constructs: **if-else**, **do-while**, function call, etc.

```

C Code (sum.c)

```

```

C Code (sum.c)

```

Generated x86-64 Assembly

| sumstore: |                  |              |

|-----------|------------------|--------------|

| pushq     | % <b>rbx</b>     |              |

| movq      | <pre>%rdx,</pre> | % <b>rbx</b> |

| call      | plus             |              |

| movq      | %rax,            | (%rbx)       |

| popq      | % <b>rbx</b>     |              |

| ret       |                  |              |

Generated x86-64 Assembly

| sumstore: |                  |              |

|-----------|------------------|--------------|

| pushq     | % <b>rbx</b>     |              |

| movq      | <pre>%rdx,</pre> | % <b>rbx</b> |

| call      | plus             |              |

| movq      | <pre>%rax,</pre> | (%rbx)       |

| popq      | % <b>rbx</b>     |              |

| ret       |                  |              |

Obtain (on CSUG machine) with command gcc -Og -S sum.c -o sum.s

Generated x86-64 Assembly

#### sumstore:

| pushq | % <b>rbx</b>     |              |

|-------|------------------|--------------|

| movq  | <pre>%rdx,</pre> | % <b>rbx</b> |

| call  | plus             |              |

| movq  | <pre>%rax,</pre> | (%rbx)       |

| popq  | % <b>rbx</b>     |              |

| ret   |                  |              |

Generated x86-64 Assembly

| sumstore: |                  |              |

|-----------|------------------|--------------|

| pushq     | % <b>rbx</b>     |              |

| movq      | %rdx,            | % <b>rbx</b> |

| call      | plus             |              |

| movq      | <pre>%rax,</pre> | (%rbx)       |

| popq      | % <b>rbx</b>     |              |

| ret       |                  |              |

Generated x86-64 Assembly

| sumstore: |                  |              |

|-----------|------------------|--------------|

| pushq     | % <b>rbx</b>     |              |

| movq      | %rdx,            | % <b>rbx</b> |

| call      | plus             |              |

| movq      | <pre>%rax,</pre> | (%rbx)       |

| popq      | %rbx             |              |

| ret       |                  |              |

| Address   | Memory                                                                                                       |

|-----------|--------------------------------------------------------------------------------------------------------------|

| 0x0400595 | 0x53<br>0x48<br>0x89<br>0xd3<br>0xe8<br>0xf2<br>0xff<br>0xff<br>0xff<br>0xff<br>0x48<br>0x89<br>0x03<br>0x5b |

|           | 0xc3                                                                                                         |

32

### Turning C into Object Code

Generated x86-64 Assembly

| sumstore: |                  |              |

|-----------|------------------|--------------|

| pushq     | % <b>rbx</b>     |              |

| movq      | %rdx,            | % <b>rbx</b> |

| call      | plus             |              |

| movq      | <pre>%rax,</pre> | (%rbx)       |

| popq      | %rbx             |              |

| ret       |                  |              |

Obtain (on CSUG machine) with command

gcc -c sum.s -o sum.o

| Address   | Memory        |

|-----------|---------------|

| 0x0400595 | 0 <b>x</b> 53 |

|           | <b>0x48</b>   |

|           | 0x89          |

|           | 0xd3          |

|           | 0xe8          |

|           | 0xf2          |

| nd        | 0xff          |

|           | 0xff          |

|           | 0xff          |

|           | <b>0x48</b>   |

|           | 0x89          |

|           | 0x03          |

|           | 0x5b          |

|           | 0xc3          |

32

### Turning C into Object Code

Generated x86-64 Assembly

| sumstore: |                  |              |

|-----------|------------------|--------------|

| pushq     | % <b>rbx</b>     |              |

| movq      | %rdx,            | % <b>rbx</b> |

| call      | plus             |              |

| movq      | <pre>%rax,</pre> | (%rbx)       |

| popq      | % <b>rbx</b>     |              |

| ret       |                  |              |

0x0400595

Obtain (on CSUG machine) with command

gcc -c sum.s -o sum.o

Total of 14 bytes

Instructions have variable lengths: e.g., 1, 3, or 5 bytes

Code starts at memory address

| Address   | Memory      |

|-----------|-------------|

| 0x0400595 | 0x53        |

|           | <b>0x48</b> |

|           | 0x89        |

|           | 0xd3        |

|           | 0xe8        |

|           | 0xf2        |

| nd        | 0xff        |

|           | 0xff        |

|           | 0xff        |

|           | <b>0x48</b> |

|           | 0x89        |

|           | <b>0x03</b> |

|           | 0x5b        |

|           | 0xc3        |

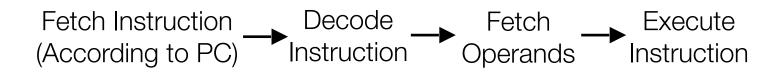

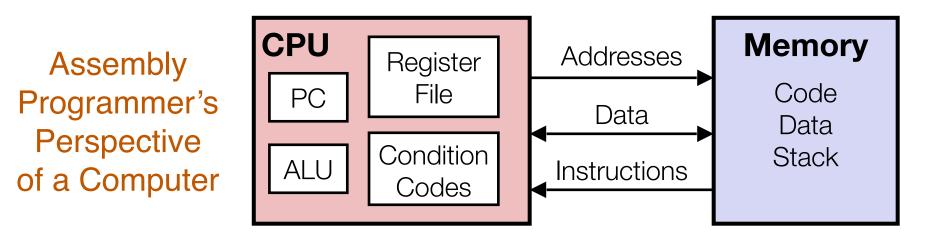

Assembly Programmer's Perspective of a Computer

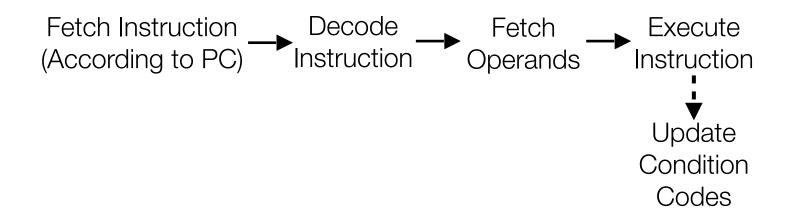

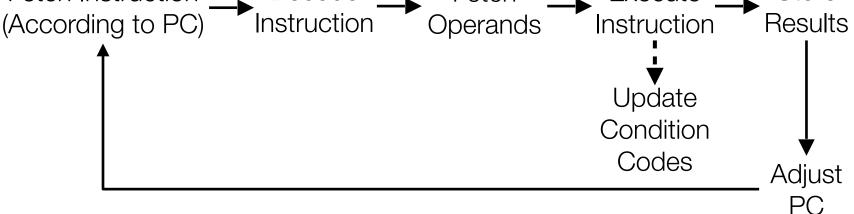

Fetch Instruction (According to PC)

Assembly Programmer's Perspective of a Computer

Fetch Instruction (According to PC)

0x4801d8

CPU Memory Addresses Assembly Register Code File PC Programmer's Data Data Perspective Condition Stack ALU Instructions of a Computer Codes

Fetch Instruction — Decode (According to PC) — Instruction

addq %rax,(%rbx)