# CSC 252: Computer Organization Spring 2024: Lecture 15

Instructor: Yuhao Zhu

Department of Computer Science

University of Rochester

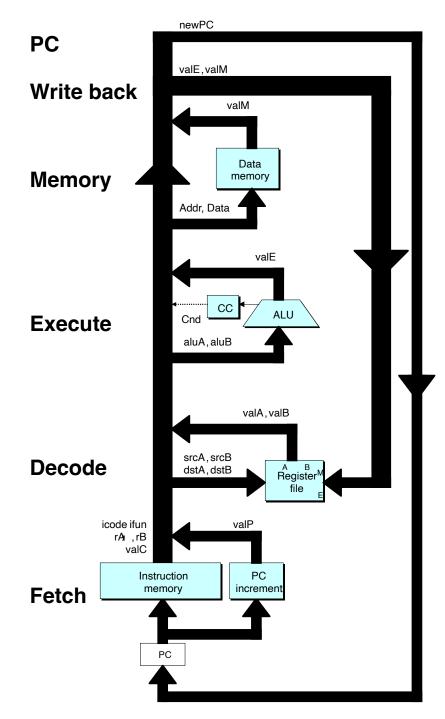

### Another Way to Look At the Microarchitecture

#### **Principles:**

- Execute each instruction one at a time, one after another

- Express every instruction as series of simple steps

- Dedicated hardware structure for completing each step

- Follow same general flow for each instruction type

Fetch: Read instruction from instruction memory

**Decode:** Read program registers

**Execute:** Compute value or address

**Memory:** Read or write data

Write Back: Write program registers

PC: Update program counter

#### **Fetch**

Read instruction from instruction memory

#### Decode

Read program registers

#### **Execute**

Compute value or address

#### Memory

Read or write data

#### Write Back

Write program registers

#### PC

Update program counter

# Stage Computation: Arith/Log. Ops

|           | OPq rA, rB                    |

|-----------|-------------------------------|

| Fetch     | icode:ifun ← M₁[PC]           |

|           | rA:rB ← M <sub>1</sub> [PC+1] |

|           | valP ← PC+2                   |

| Decode    | valA ← R[rA]                  |

|           | valB ← R[rB]                  |

| Execute   | valE ← valB OP valA           |

| Execute   | Set CC                        |

| Memory    |                               |

| Write     | R[rB] ← valE                  |

| back      |                               |

| PC update | PC ← valP                     |

Read instruction byte Read register byte

Compute next PC

Read operand A

Read operand B

Perform ALU operation

Set condition code register

Write back result

**Update PC**

### Stage Computation: rmmovq

rmmovq rA, D(rB) 4 0 rA rB D

|           | rmmovq rA, D(rB)              |

|-----------|-------------------------------|

| Fetch     | icode:ifun ← M₁[PC]           |

|           | rA:rB ← M <sub>1</sub> [PC+1] |

|           | valC ← M <sub>8</sub> [PC+2]  |

|           | valP ← PC+10                  |

| Decode    | valA ← R[rA]                  |

|           | valB ← R[rB]                  |

| Execute   | valE ← valB + valC            |

| Mamary    | BA FroiE1 wold                |

| Memory    | M <sub>8</sub> [valE] ← valA  |

| Write     |                               |

| back      |                               |

| PC update | PC ← valP                     |

Read instruction byte

Read register byte

Read displacement D

Compute next PC

Read operand A

Read operand B

Compute effective address

Write value to memory

**Update PC**

# Stage Computation: Jumps

|           | jXX Dest                     |                          |

|-----------|------------------------------|--------------------------|

|           | icode:ifun ← M₁[PC]          | Read instruction byte    |

| Fetch     |                              |                          |

|           | valC ← M <sub>8</sub> [PC+1] | Read destination address |

|           | valP ← PC+9                  | Fall through address     |

| Decode    |                              |                          |

| Execute   | Cnd ← Cond(CC,ifun)          | Take branch?             |

| Memory    |                              |                          |

| Write     |                              |                          |

| back      |                              |                          |

| PC update | PC ← Cnd ? valC : valP       | Update PC                |

- Compute both addresses

- Choose based on setting of condition codes and branch condition

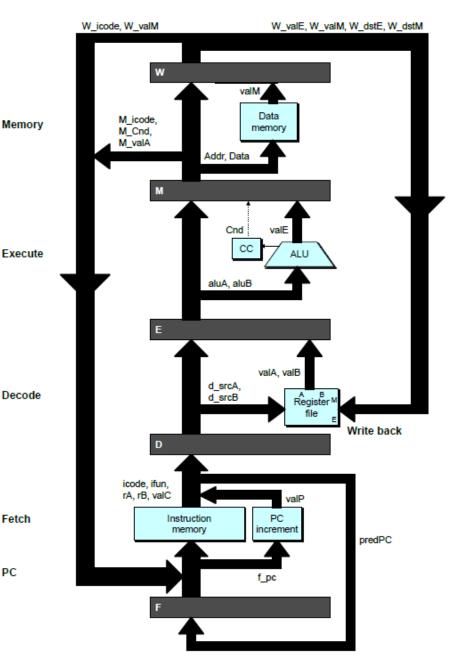

# Pipeline Stages

#### **Fetch**

- Select current PC

- Read instruction

- Compute incremented PC

#### Decode

Read program registers

#### Execute

Operate ALU

#### Memory

Read or write data memory

PC

#### Write Back

Update register file

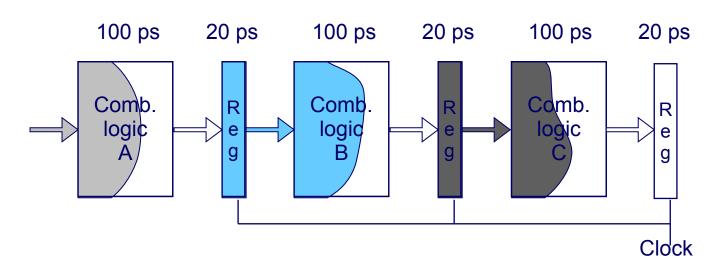

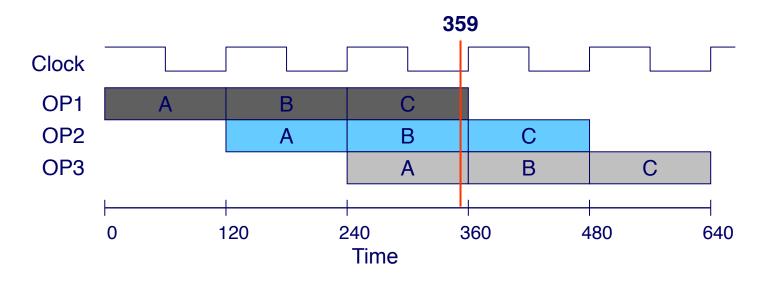

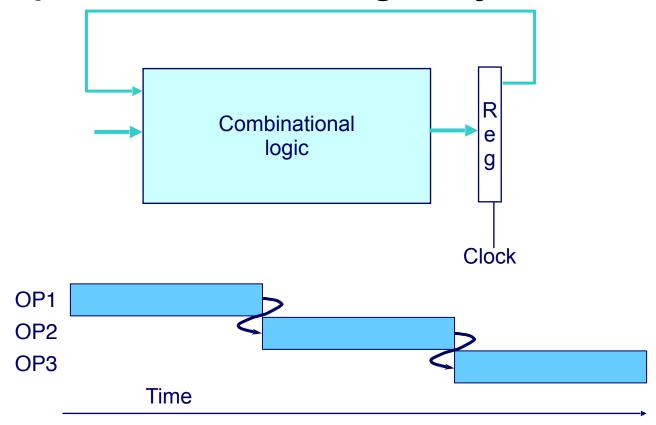

### Real-World Pipelines: Car Washes

#### **Sequential**

**Pipelined**

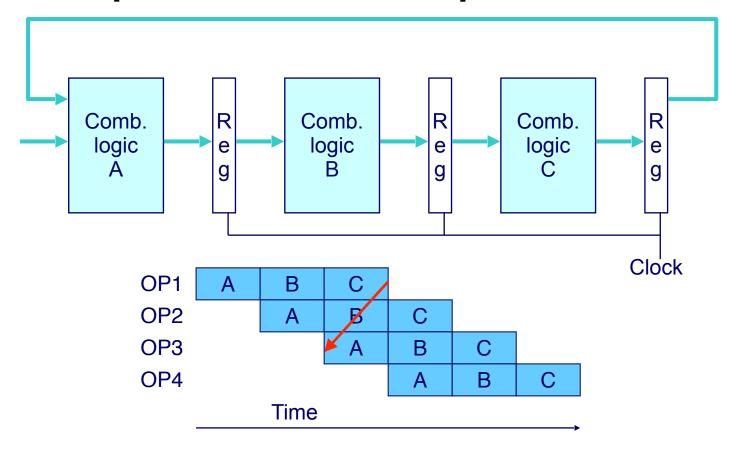

#### Idea

- Divide process into independent stages

- Move objects through stages in sequence

- At any given times, multiple objects being processed

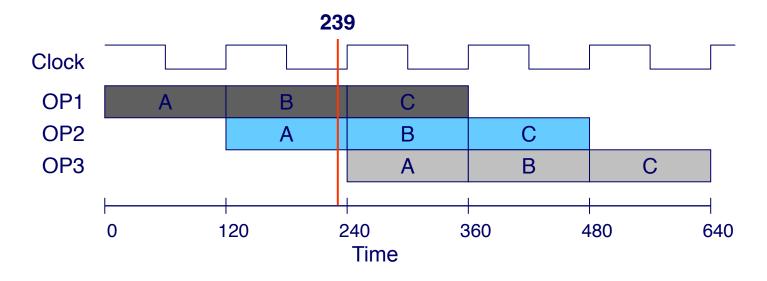

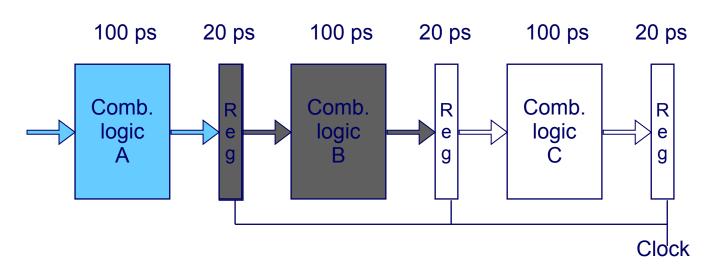

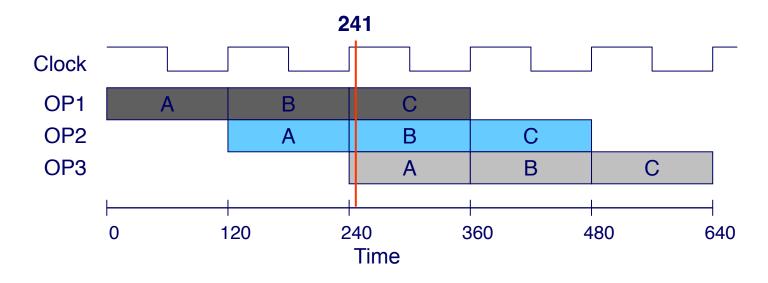

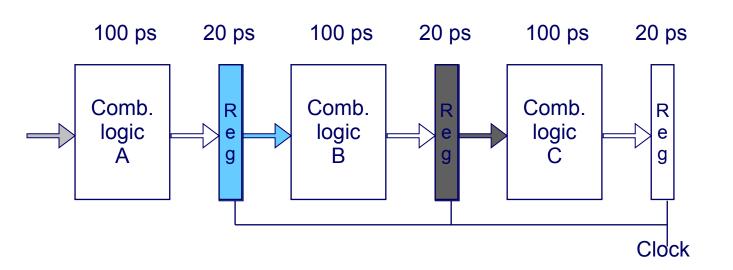

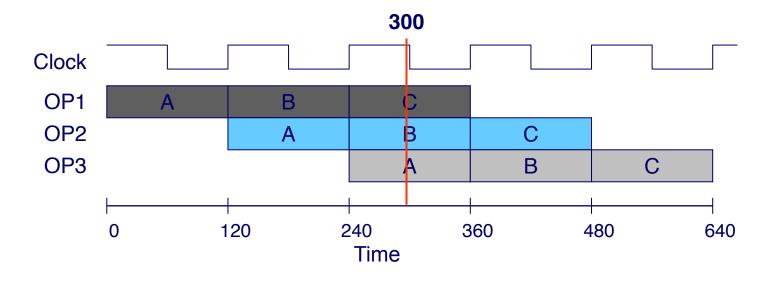

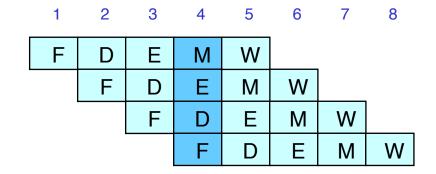

# Pipeline Illustration

#### **Inst**

Fetch Reg Decode Reg Execute Reg Memory Reg back Reg

# Making the Pipeline Really Work

- Control Dependencies

- What is it?

- Software mitigation: Inserting Nops

- Software mitigation: Delay Slots

- Data Dependencies

- What is it?

- Software mitigation: Inserting Nops

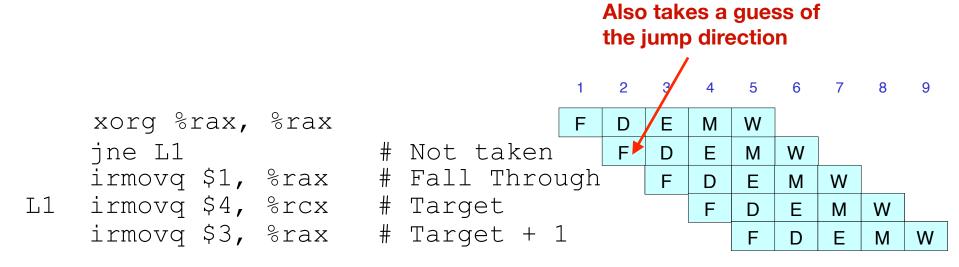

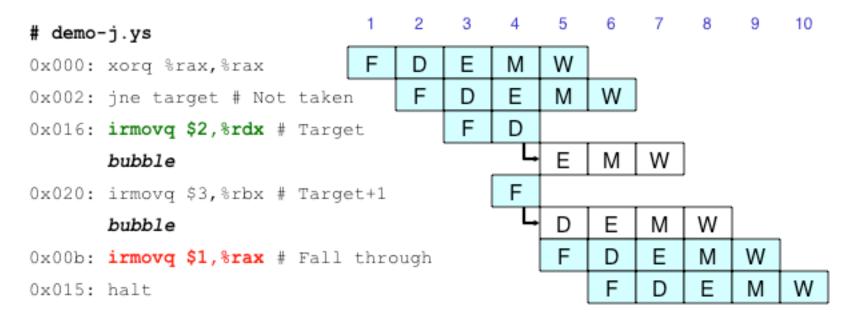

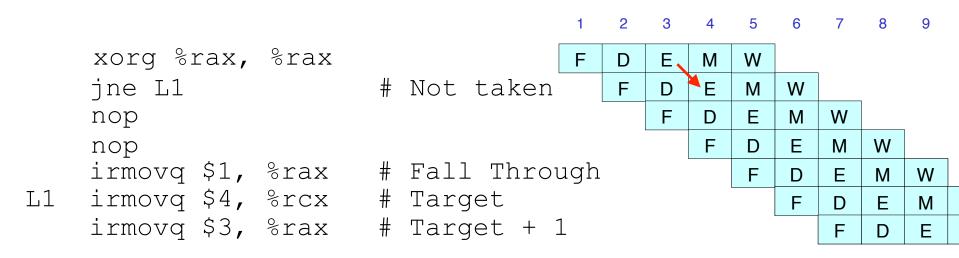

# **Control Dependency**

- Definition: Outcome of instruction A determines whether or not instruction B should be executed or not.

- Jump instruction example below:

- jne L1 determines whether irmovq \$1, %rax should be executed

- But jne doesn't know its outcome until after its Execute stage

```

xorg %rax, %rax

F

D

Ε

W

M

Not taken

jne L1

F

E

M

W

inomovq $1, %rax

# Fall Through

M

W

inomovq $4, %rcx

T<sub>1</sub>1

# Target

Ε

M

W

irmovq $3, %rax

# Target + 1

W

F

M

F

```

# **Delay Slots**

```

xorq %rax, %rax

F

D

Ε

M

W

ine L1

Ε

M

W

Can we make use of

nop

F

Ε

D

W

M

the 2 wasted slots?

nop

D

Ε

М

W

Fall Through

irmova $1, %rax

F

Ε

M

W

L1

irmovq $4, %rcx

# Target

D

Ε

М

irmovq $3, %rax

# Target + 1

F

D

Ε

```

Have to make sure do\_C doesn't depend on do\_A and do\_B!!!

```

if (cond) {

do_A();

} else {

do_B();

}

do_C();

```

2

4 5

7

# **Delay Slots**

```

xorq %rax, %rax

F

D

Ε

M

W

ine L1

Ε

M

W

Can we make use of

F

nop

D

Ε

W

M

the 2 wasted slots?

nop

D

Ε

M

W

irmovg $1, %rax

Fall Through

F

Ε

М

W

irmovq $4, %rcx

T<sub>1</sub>1

# Target

Ε

M

irmovg $3, %rax

Target + 1

F

D

Ε

```

2

# A less obvious example

```

do_C();

if (cond) {

do_A();

} else {

do_B();

}

```

```

add A, B add A, B

or C, D sub E, F

sub E, F jle 0x200

jle 0x200 or C, D

add A, C add A, C

Why don't we move the sub instruction?

```

4 5

7

### **Resolving Control Dependencies**

#### Software Mechanisms

- Adding NOPs: requires compiler to insert nops, which also take memory space — not a good idea

- Delay slot: insert instructions that do not depend on the effect of the preceding instruction. These instructions will execute even if the preceding branch is taken — old RISC approach

#### Hardware mechanisms

- Stalling (Think of it as hardware automatically inserting nops)

- Branch Prediction

- Return Address Stack

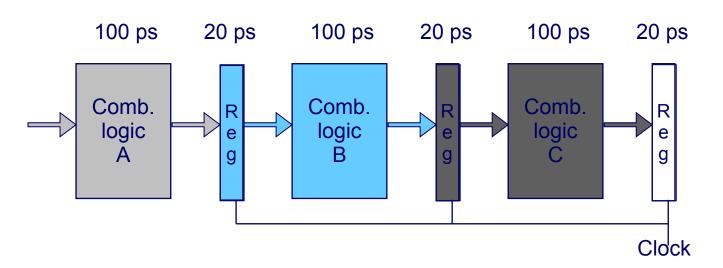

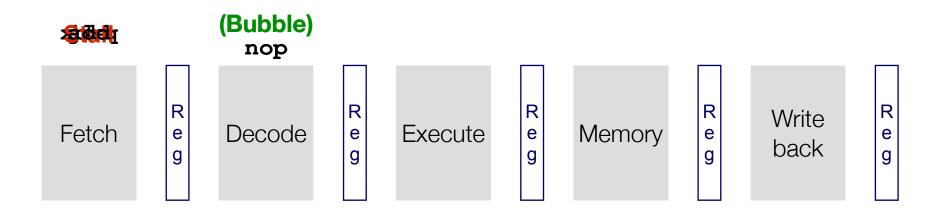

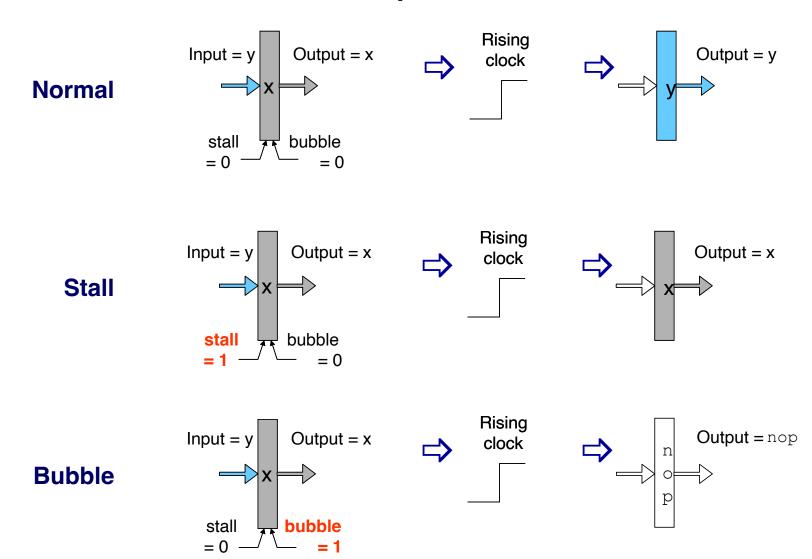

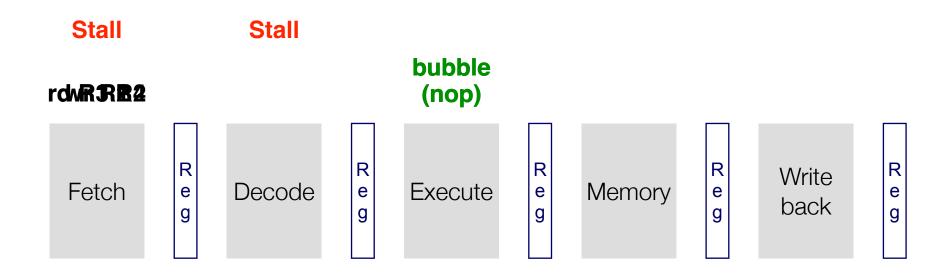

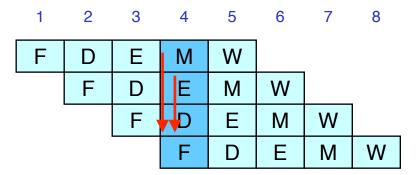

### Hardware Generated Nops (Bubble and Stalling)

- **Stall**: the pipeline register shouldn't be written

- Bubble: signals correspond to a nop

- Why is it good for the hardware to do so anyways?

### How are Stall and Bubble Implemented in Hardware?

### **Branch Prediction**

Idea: instead of waiting, why not just guess the direction of jump?

If prediction is correct: pipeline moves forward without stalling

If mispredicted: kill mis-executed instructions, start from the correct target

### **Branch Prediction**

Idea: instead of waiting, why not just guess the direction of jump?

If prediction is correct: pipeline moves forward without stalling

If mispredicted: kill mis-executed instructions, start from the correct target

#### Static Prediction

- Always Taken

- Always Not-taken

#### **Dynamic Prediction**

Dynamically predict taken/not-taken for each specific jump instruction

### **Static Prediction**

#### Observation (Assumption really): Two uses of jumps

- People use jumps to check corner cases. These branches are mostly not taken because corner cases are rare.

- People use jumps to implement loops. These branches are mostly taken because a loop takes multiple iterations.

#### Strategy:

- Forward jumps (i.e., if-else): always predict not-taken

- Backward jumps (i.e., loop): always predict taken

### Static Prediction

#### Knowing branch prediction strategy helps us write faster code

- Any difference between the following two code snippets?

- What if you know that hardware uses the always non-taken branch prediction?

```

if (cond) {

do_A()

do_B()

} else {

do_B()

do_A()

}

```

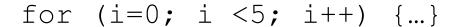

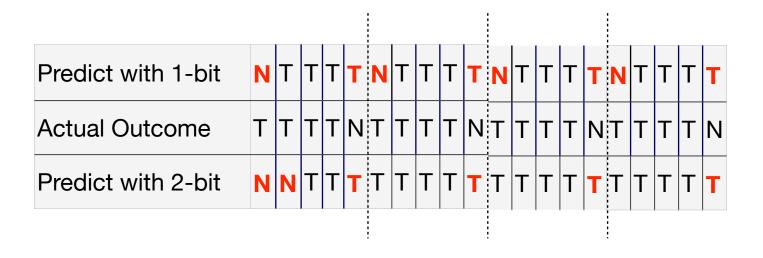

### **Dynamic Prediction**

#### Simplest idea:

- If last time taken, predict taken; if last time not-taken, predict not-taken

- Called 1-bit branch predictor

- Works nicely for loops

for

$$(i=0; i < 5; i++) {...}$$

| Iteration #1      | 0 | 1 | 2 | 3 | 4 |

|-------------------|---|---|---|---|---|

| Predicted Outcome | N | Ţ | Т | Т | Т |

| Actual Outcome    | Т | Т | Т | Т | N |

# **Dynamic Prediction**

- With 1-bit prediction, we change our mind instantly if mispredict

- Might be too quick. Thus 2-bit branch prediction: we have to mispredict twice in a row before changing our mind

# More Advanced Dynamic Prediction

- Look for past histories across instructions

- Branches are often correlated

- Direction of one branch determines another

cond1 branch nottaken means (x <=0) branch taken

$$x = 0$$

if (cond1)  $x = 3$

if (cond2)  $y = 19$

if (x <= 0)  $z = 13$

# What Happens If We Mispredict?

#### Cancel instructions when mispredicted

- Assuming we detect branch not-taken in execute stage

- On following cycle, replace instructions in execute and decode by **bubbles**

- No side effects have occurred yet

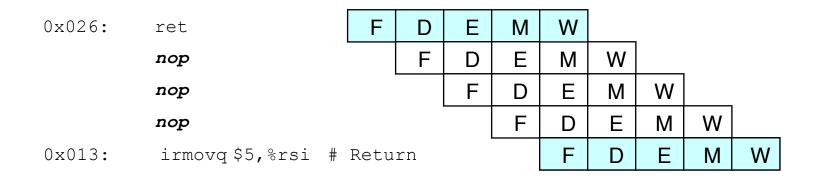

### **Return Instruction**

```

0x000:

irmovq Stack,%rsp # Intialize stack pointer

0x00a:

# Procedure call

call p

0x013:

irmovq $5,%rsi

# Return point

0x01d:

halt

0x020: pos 0x20

0x020: p: irmovq $-1,%rdi

# procedure

0x02a:

ret

0x02b:

irmovq $1,%rax

# Should not be executed

0x035:

irmovq $2,%rcx  # Should not be executed

0x03f: irmovq $3,%rdx  # Should not be executed

irmovq $4,%rbx

0x049:

# Should not be executed

0x100: .pos 0x100

0x100: Stack:

# Stack: Stack pointer

```

# Stalling for Return

- As ret passes through pipeline, stall at fetch stage

- While in decode, execute, and memory stage

- Inject bubble into decode stage

- Release stall when reach write-back stage

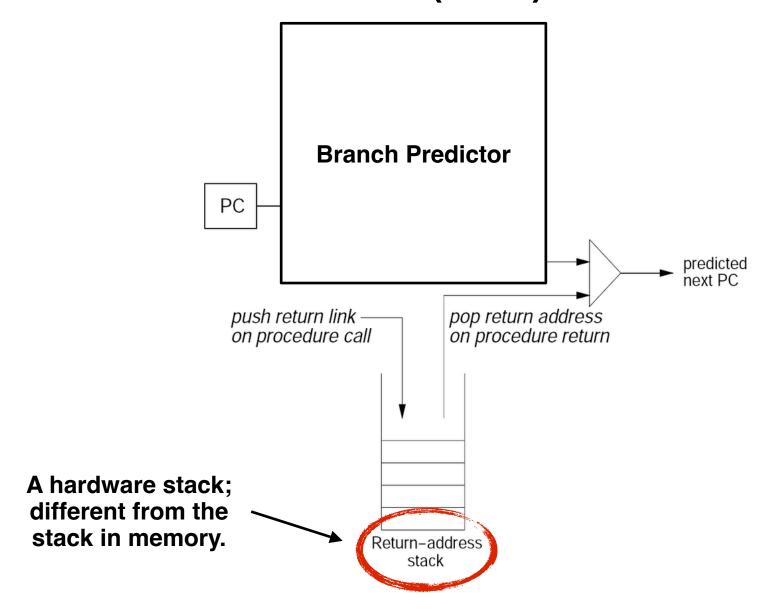

# Return Address Stack (RAS)

- Stalling for return is silly since we know where exactly we need to jump to, except the jump target is retrieved later in the memory stage.

- Can we get that sooner? Where should we get it?

# Return Address Stack (RAS)

# Today: Making the Pipeline Really Work

- Control Dependencies

- Inserting Nops

- Stalling

- Delay Slots

- Branch Prediction

- Data Dependencies

- Inserting Nops

- Stalling

- Out-of-order execution

### **Data Dependencies**

```

1 irmovq $50, %rax

2 addq %rax, %rbx

3 mrmovq 100(%rbx), %rdx

```

- Result from one instruction used as operand for another

- Read-after-write (RAW) dependency

- Very common in actual programs

- Must make sure our pipeline handles these properly

- Get correct results

- Minimize performance impact

# A Subtle Data Dependency

- Jump instruction example below:

- jne L1 determines whether irmovq \$1, %rax should be executed

- But jne doesn't know its outcome until after its Execute stage.

Why?

- There is a data dependency between xorg and jne. The "data" is the status flags.

### Data Dependencies in Single-Cycle Machines

#### In Single-Cycle Implementation:

Each operation starts only after the previous operation finishes.

Dependency always satisfied.

### Data Dependencies in Pipeline Machines

Data Hazards happen when:

Result does not feed back around in time for next operation

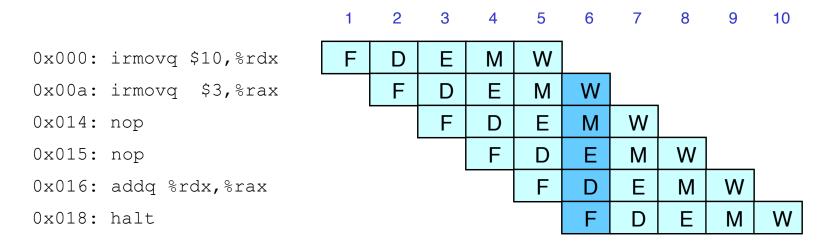

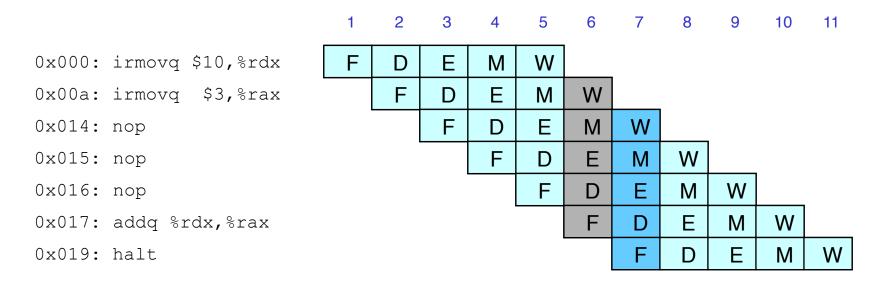

#### Data Dependencies: No Nop

0x000: irmovq \$10,%rdx

0x00a: irmovq \$3,%rax

0x014: addq %rdx,%rax

0x016: halt

Remember registers get updated in the Write-back stage

addq reads wrong %rdx and %rax

### Data Dependencies: 1 Nop

addq still reads wrong %rdx and %rax

### Data Dependencies: 2 Nop's

addq reads the correct %rdx, but %rax still wrong

### Data Dependencies: 3 Nop's

addq reads the correct %rdx and %rax

#### Resolving Data Dependencies

- Software Mechanisms

- Adding NOPs: requires compiler to insert nops, which also take memory space — not a good idea

- Hardware mechanisms

- Stalling

- Forwarding

- Out-of-order execution

#### Hardware Generated Nops (Bubble and Stalling)

### **Detecting Stall Condition**

- · Using a "scoreboard". Each register has a bit.

- Every instruction that writes to a register sets the bit.

- Every instruction that reads a register would have to check the bit first.

- If the bit is set, then generate a bubble

- Otherwise, free to go!!

### **Detecting Stall Condition**

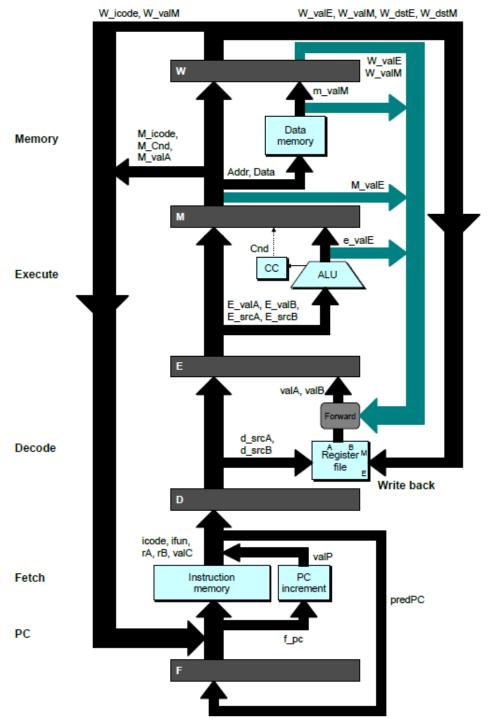

### **Data Forwarding**

#### Naïve Pipeline

- Register isn't written until completion of write-back stage

- Source operands read from register file in decode stage

- The decode stage can't start until the write-back stage finishes

#### Observation

Value generated in execute or memory stage

#### Trick

- Pass value directly from generating instruction to decode stage

- Needs to be available at end of decode stage

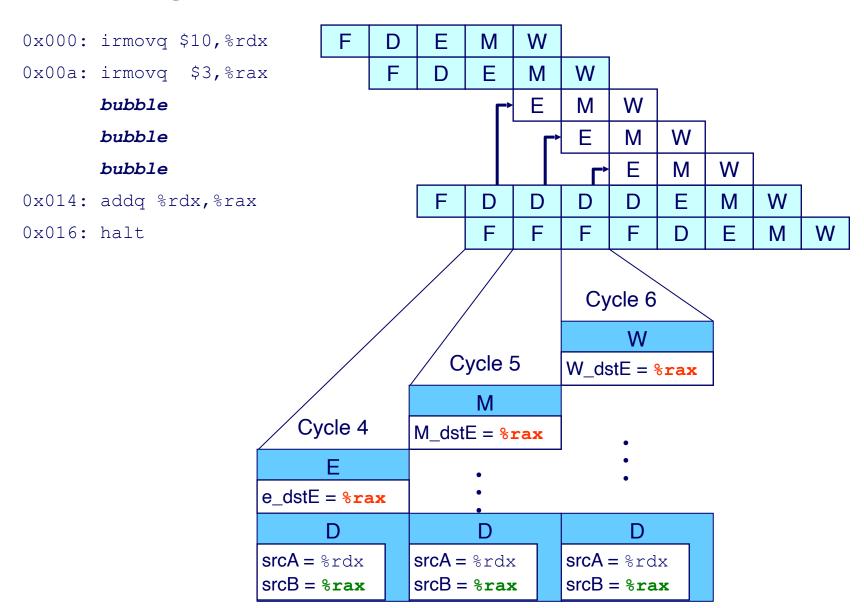

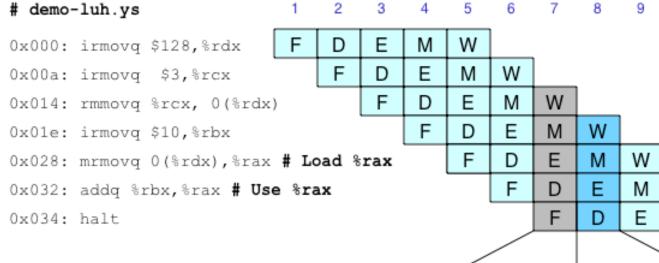

## Data Forwarding Example

- irmovq writes %rax to the register file at the end of the write-back stage

- But the value of %rax is already available at the beginning of the writeback stage

- Forward % rax to the decode stage of addq.

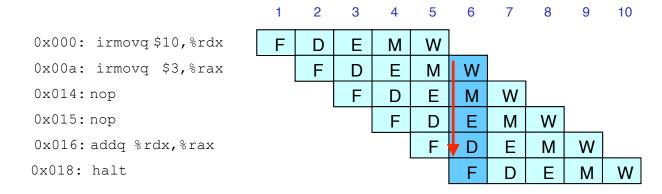

### Data Forwarding Example #2

0x000: irmovq \$10,%rdx

0x00a: irmovq \$3,%rax

0x014: addq %rdx,%rax

0x016: halt

#### Register %rdx

Forward from the memory stage

#### Register %rax

Forward from the execute stage

## Hardware Design

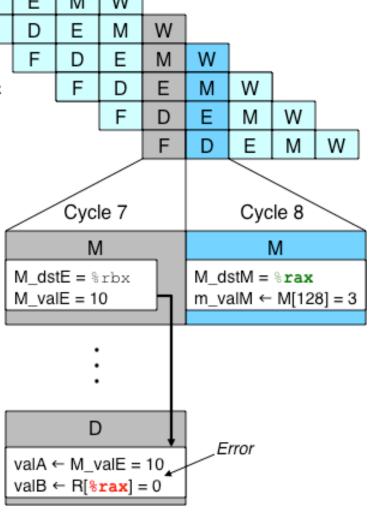

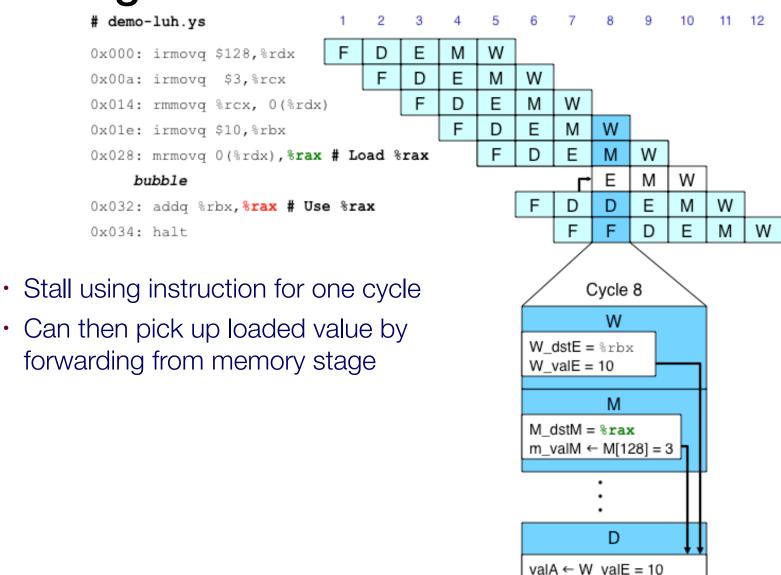

#### **Limitation of Forwarding**

#### Load-use dependency

- Value needed by end of decode stage in cycle 7

- Value read from memory in memory stage of cycle 8

11

10

## **Avoiding Load/Use Hazard**

valB ← m valM = 3

#### **Out-of-order Execution**

- Compiler could do this, but has limitations

- Generally done in hardware

# Long-latency instruction. Forces the pipeline to stall.

```

r0 = r1 + r2

r3 = MEM[r0]

r4 = r3 + r6

r7 = r5 + r1

...

r4 = r3 + r6

r2 = r1 + r2

r3 = MEM[r0]

r4 = r3 + r6

r7 = r5 + r1

...

r4 = r3 + r6

```

#### **Out-of-order Execution**

"Tomasolu Algorithm" is the algorithm that is most widely implemented in modern hardware to get out-of-order execution right.