# Low-Latency Proactive Continuous Vision

#### **Yiming Gan**

Department of Computer Science, University of Rochester

with

Yuxian Qiu, Shanghai Jiao Tong University

Lele Chen, University of Rochester

Jingwen Leng, Shanghai Jiao Tong University

Yuhao Zhu University of Rochester

# Continuous Vision: Long Frame Latency

# Bottleneck: Serialization

#### Sensor

### Bottleneck: Serialization

### Bottleneck: Serialization

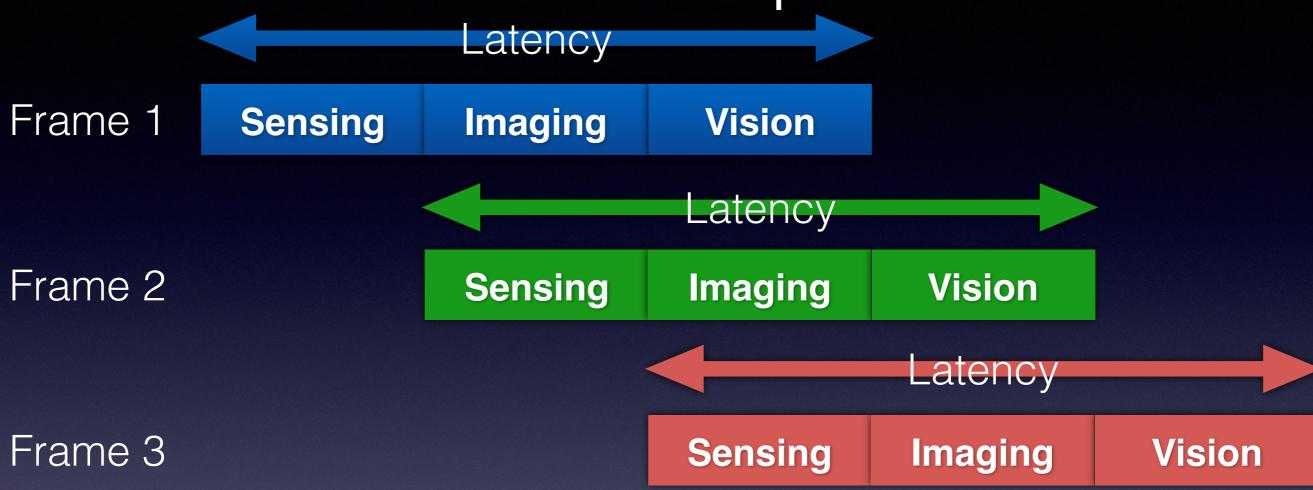

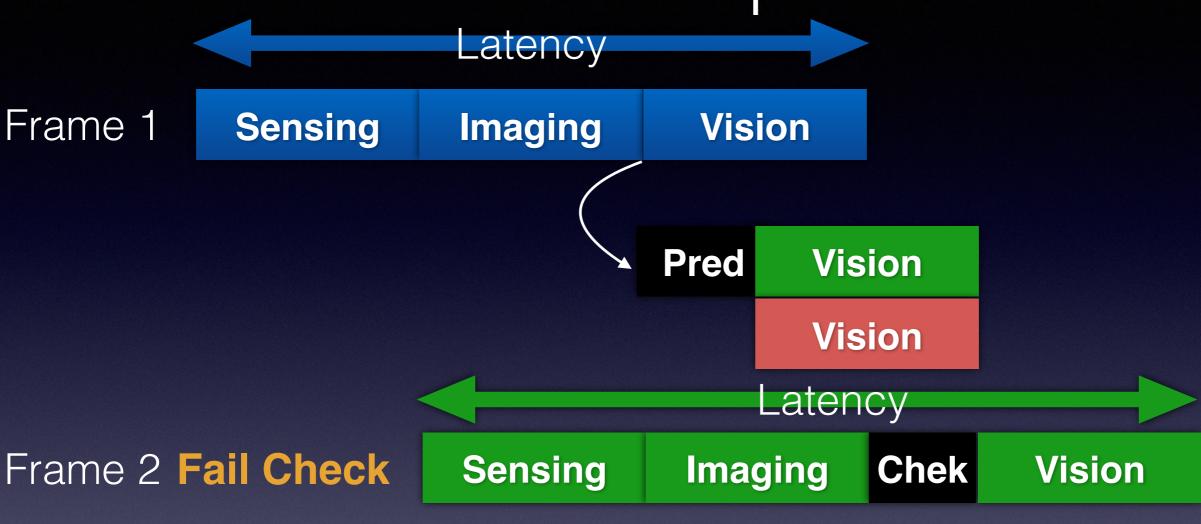

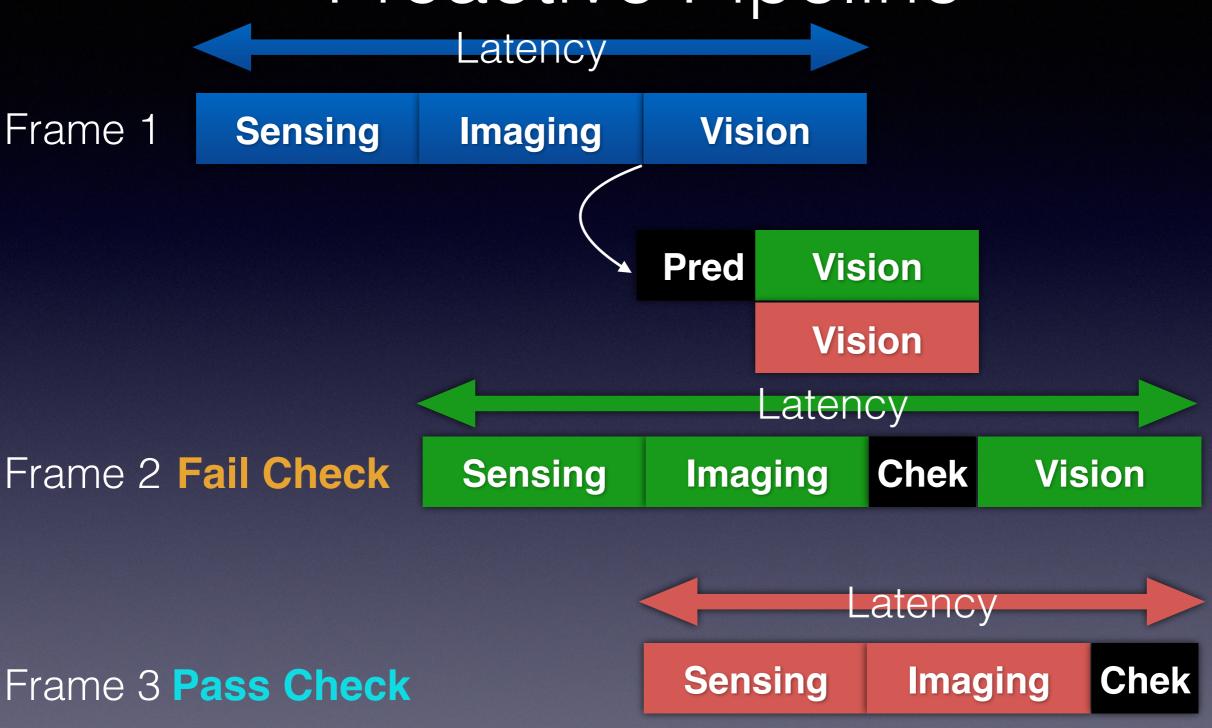

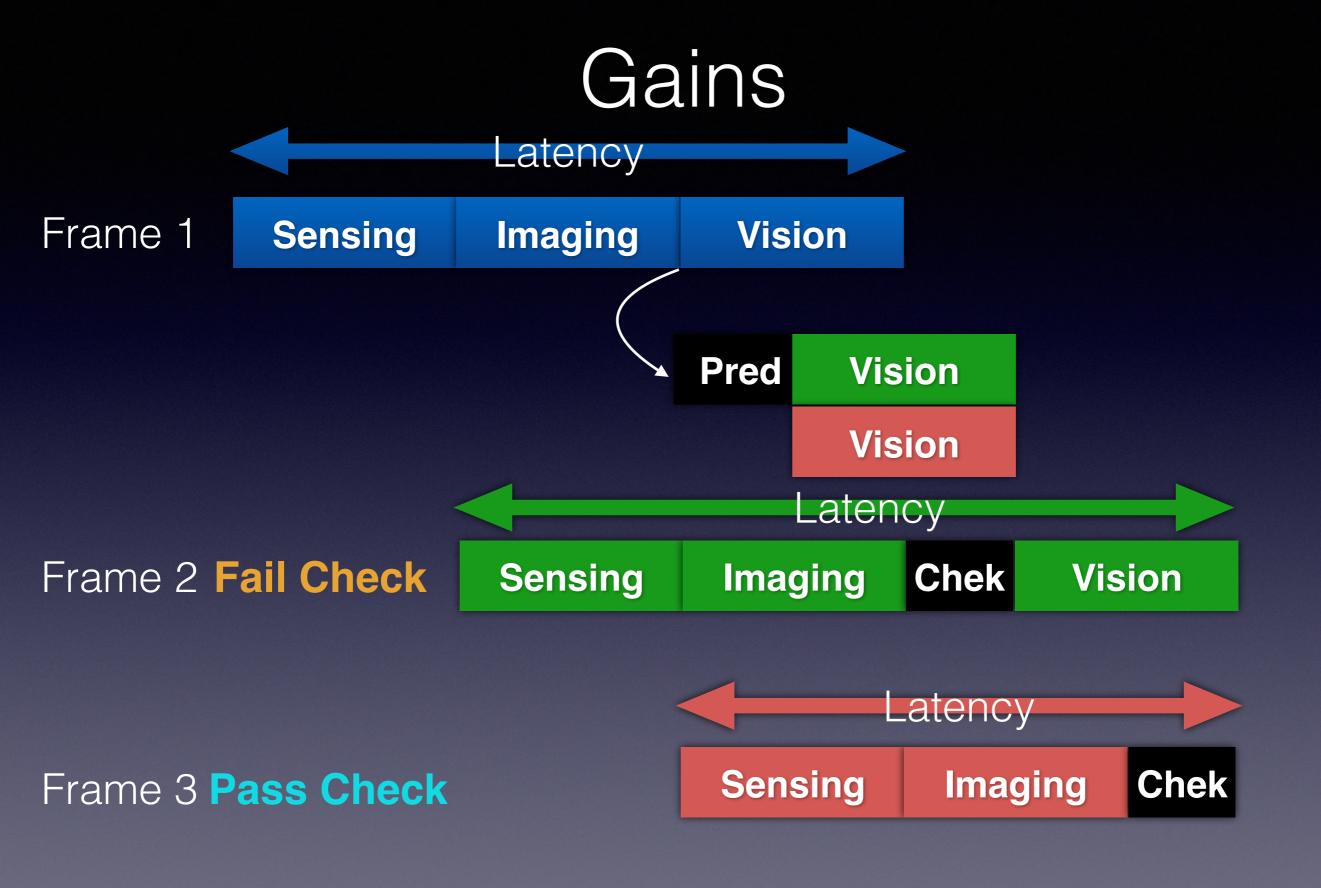

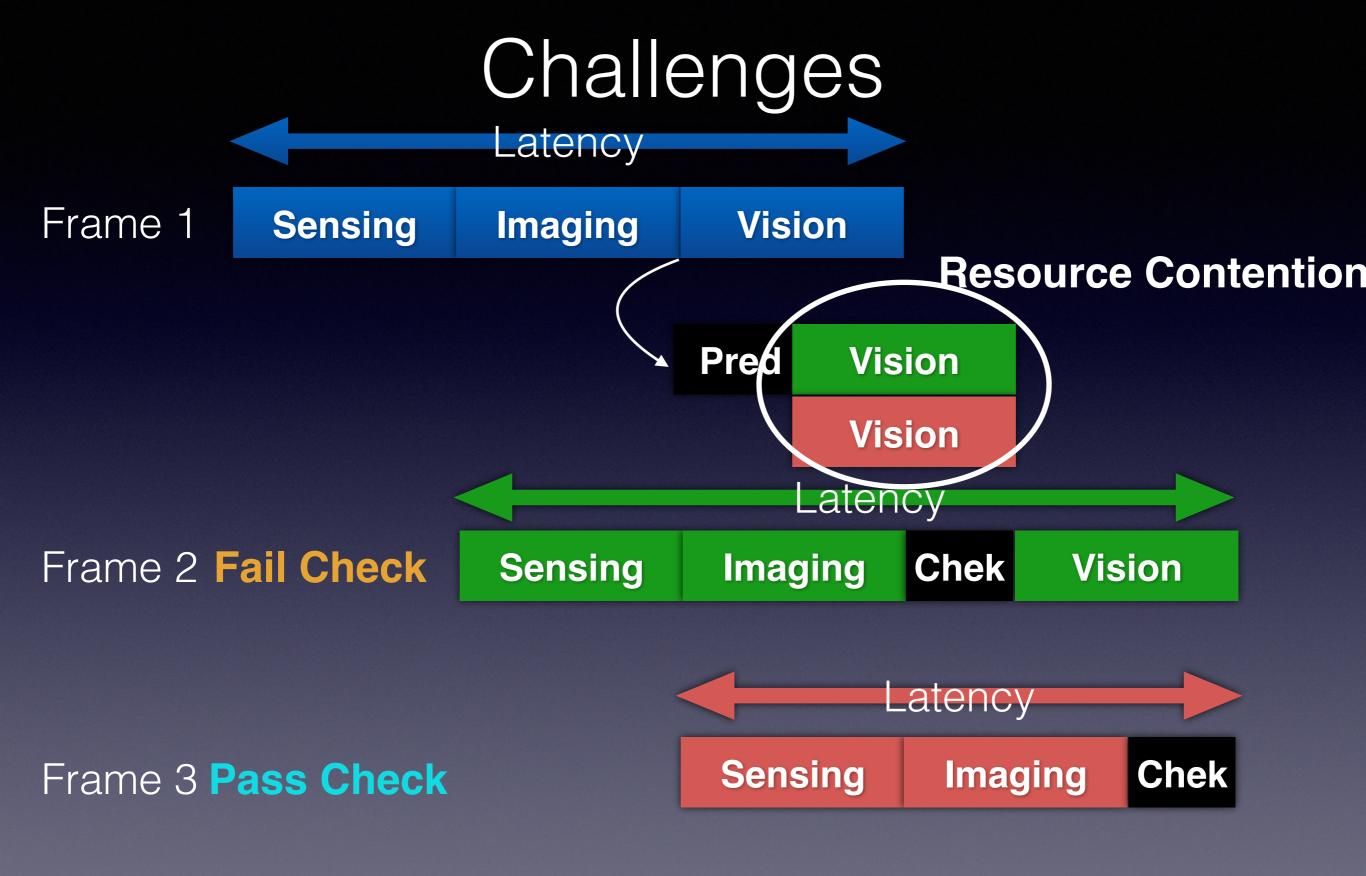

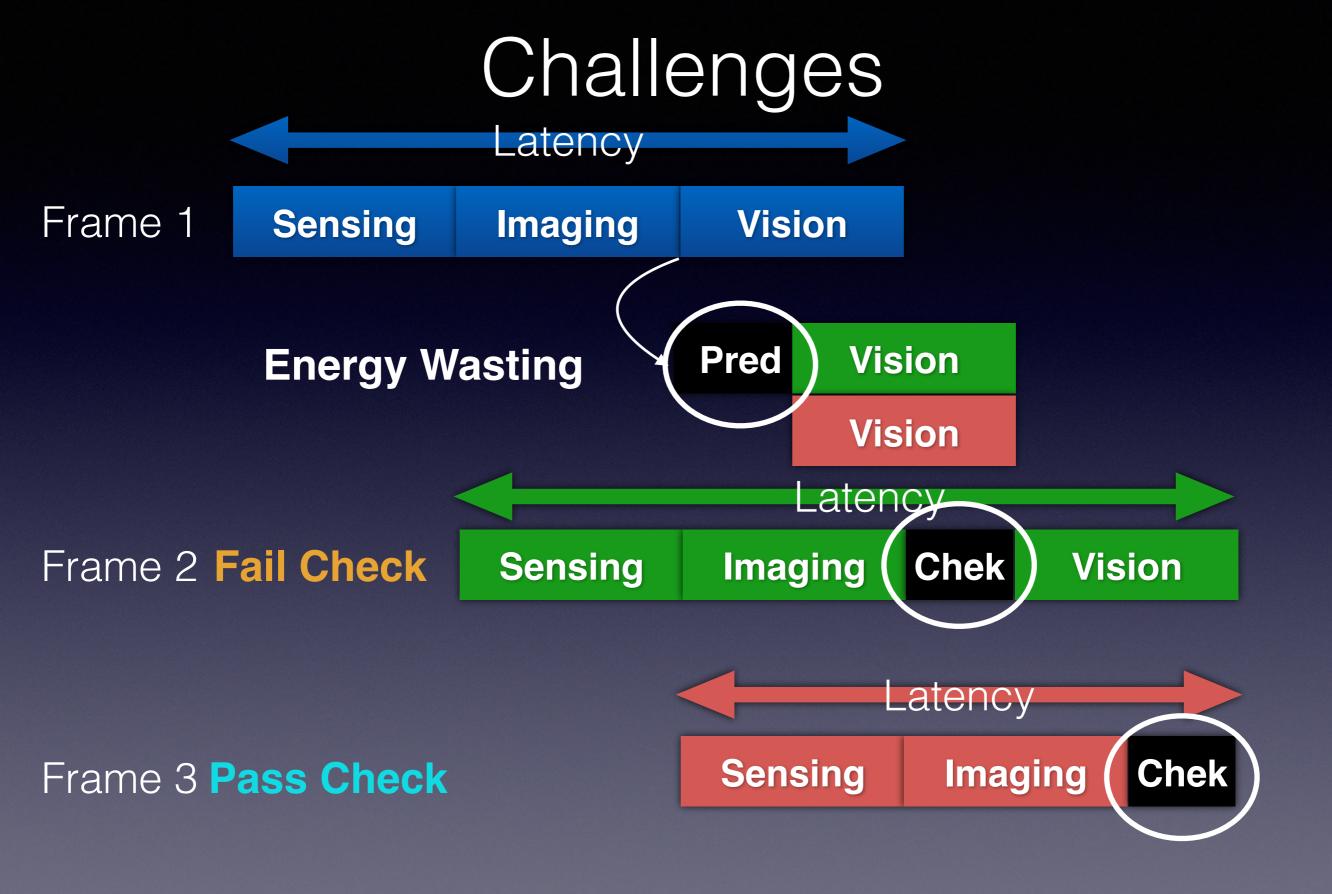

# Traditional Pipeline

Latency

Frame 1

Sensing

**Imaging**

Vision

Frame 1 Sensing Imaging Vision

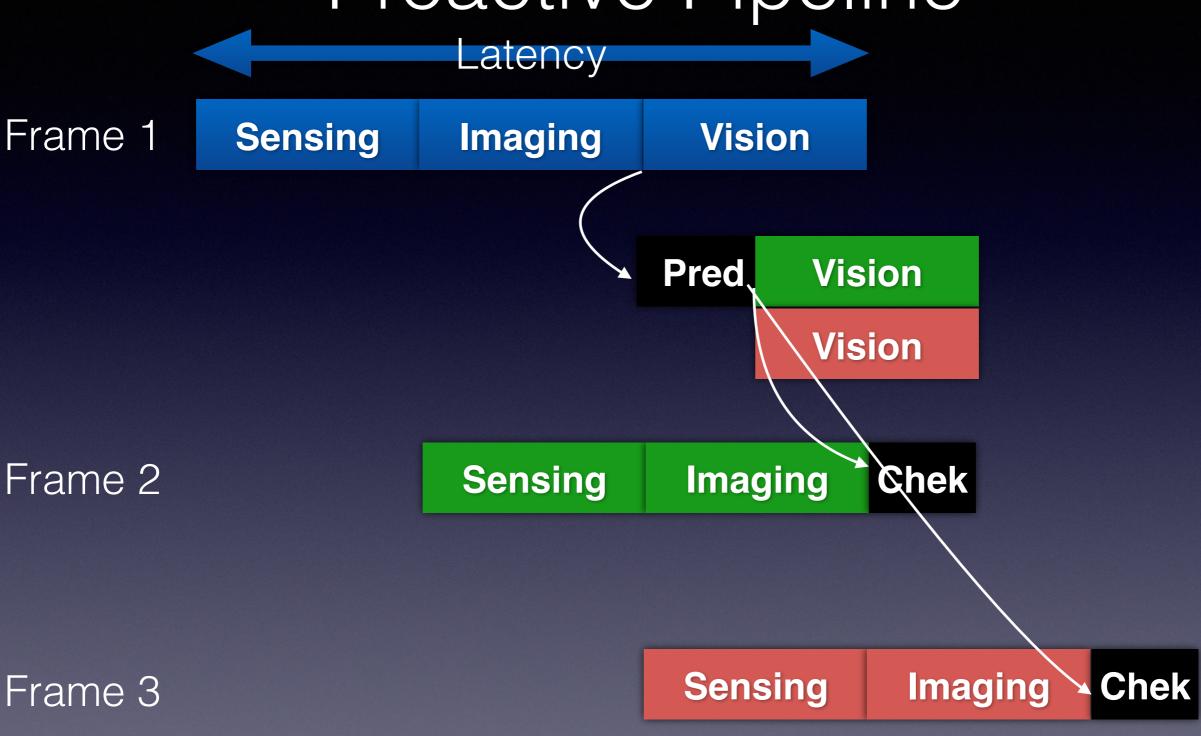

Pred

Frame 1 Sensing Imaging Vision

Pred Vision

Vision

Frame 2

Sensing

**Imaging**

Frame 3

Sensing

**Imaging**

Frame 3

Sensing Imaging Chek

#### Snapdragon 675

#### **CPU**

4<sup>th</sup> gen Kryo CPU Performance @ 2.0GHz Efficiency @ 1.7GHz

Artificial Intelligence

3rd gen Qualcomm® Al Engine

#### Modem

Snapdragon X12 Cat 12 DL, up to 600 Mbps

#### **Audio**

Qualcomm Aqstic<sup>™</sup> audio Qualcomm<sup>®</sup> aptX<sup>™</sup> audio

**Display**Up to FHD+ display

#### **GPU**

6th gen Adreno GPU

#### **DSP**

6<sup>th</sup> gen Hexagon DSP DSP Security

#### Camera

2<sup>nd</sup> gen Qualcomm Spectra ISP Up to 25 Megapixels @ 30fps ZSL 48 Megapixels snapshot

#### Charging

Qualcomm<sup>®</sup> Quick Charge<sup>™</sup> 4+ technology

Commercial devices expected in Q1 2019

Qualcomm Al Engine and Qualcomm Quick Charge are products of Qualcomm Technologies, Inc. and/or its subsidiaries.

#### Snapdragon 675

#### **CPU**

4<sup>th</sup> gen Kryo CPU Performance @ 2.0GHz Efficiency @ 1.7GHz

Artificial Intelligence

3rd gen Qualcomm® Al Engine

#### Modern

Snapdragon X12 Cat 12 DL, up to 600 Mbps

#### **Audio**

Qualcomm Aqstic<sup>™</sup> audio Qualcomm<sup>®</sup> aptX<sup>™</sup> audio

**Display**Up to FHD+ display

Qualcommus snapdragon

GPU

6th gen Adreno GPU

DSP

6<sup>th</sup> gen Hexagon DSP DSP Security

#### Camera

2<sup>nd</sup> gen Qualcomm Spectra ISP Up to 25 Megapixels @ 30fps ZSL 48 Megapixels snapshot

Charging

Qualcomm<sup>®</sup> Quick Charge<sup>™</sup> 4+ technology

Commercial devices expected in Q1 2019

Qualcomm Al Engine and Qualcomm Quick Charge are products of Qualcomm Technologies, Inc. and/or its subsidiaries.

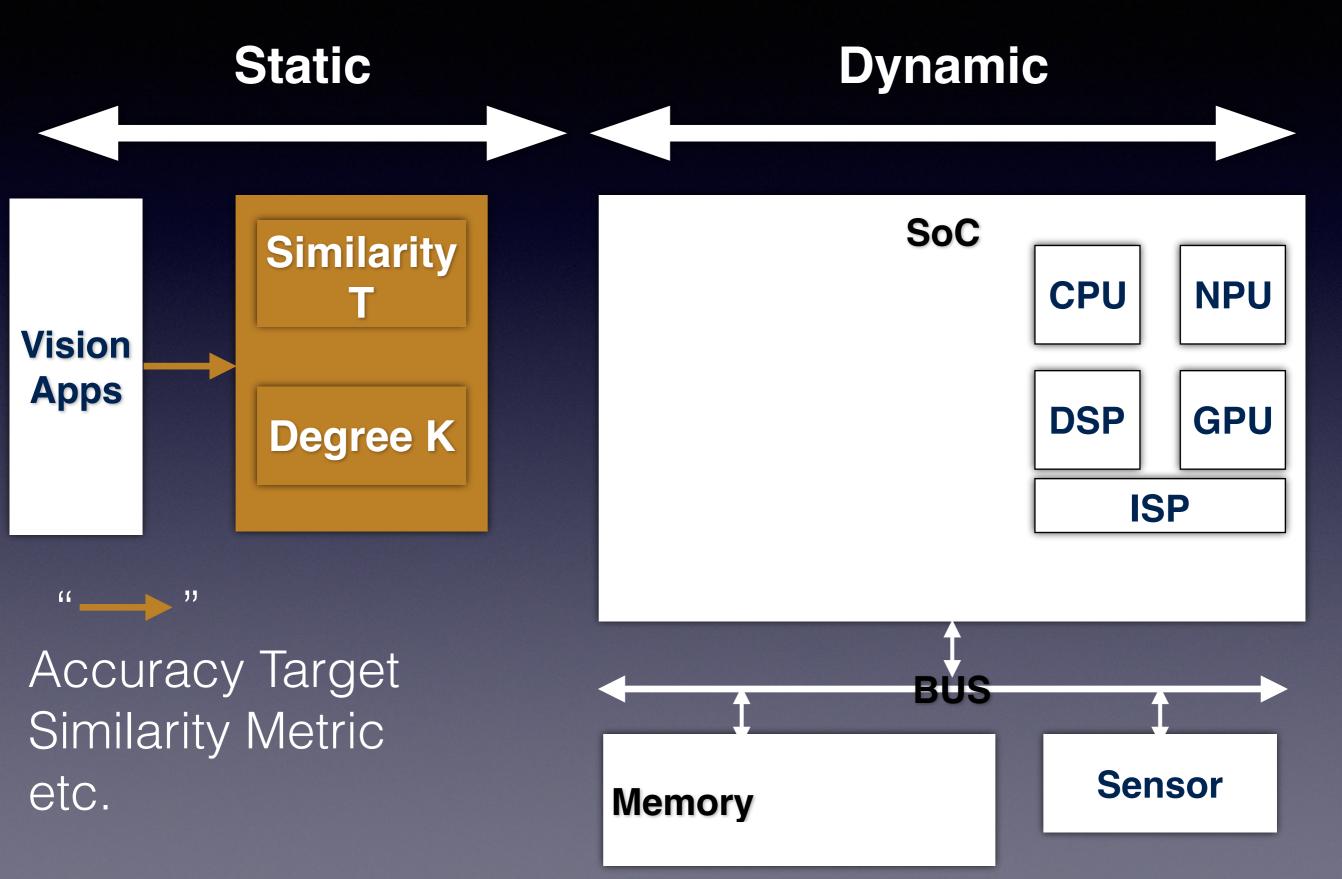

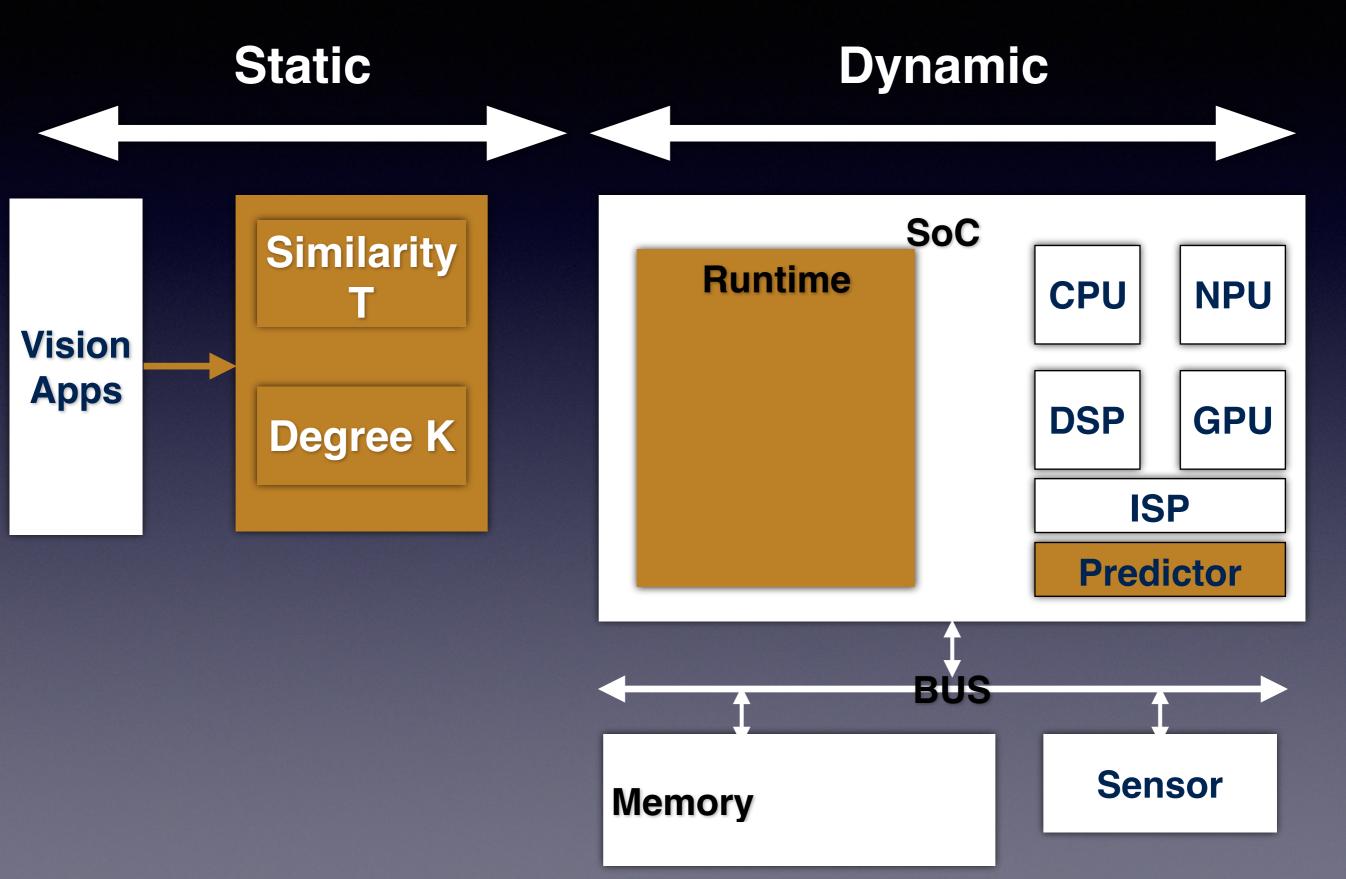

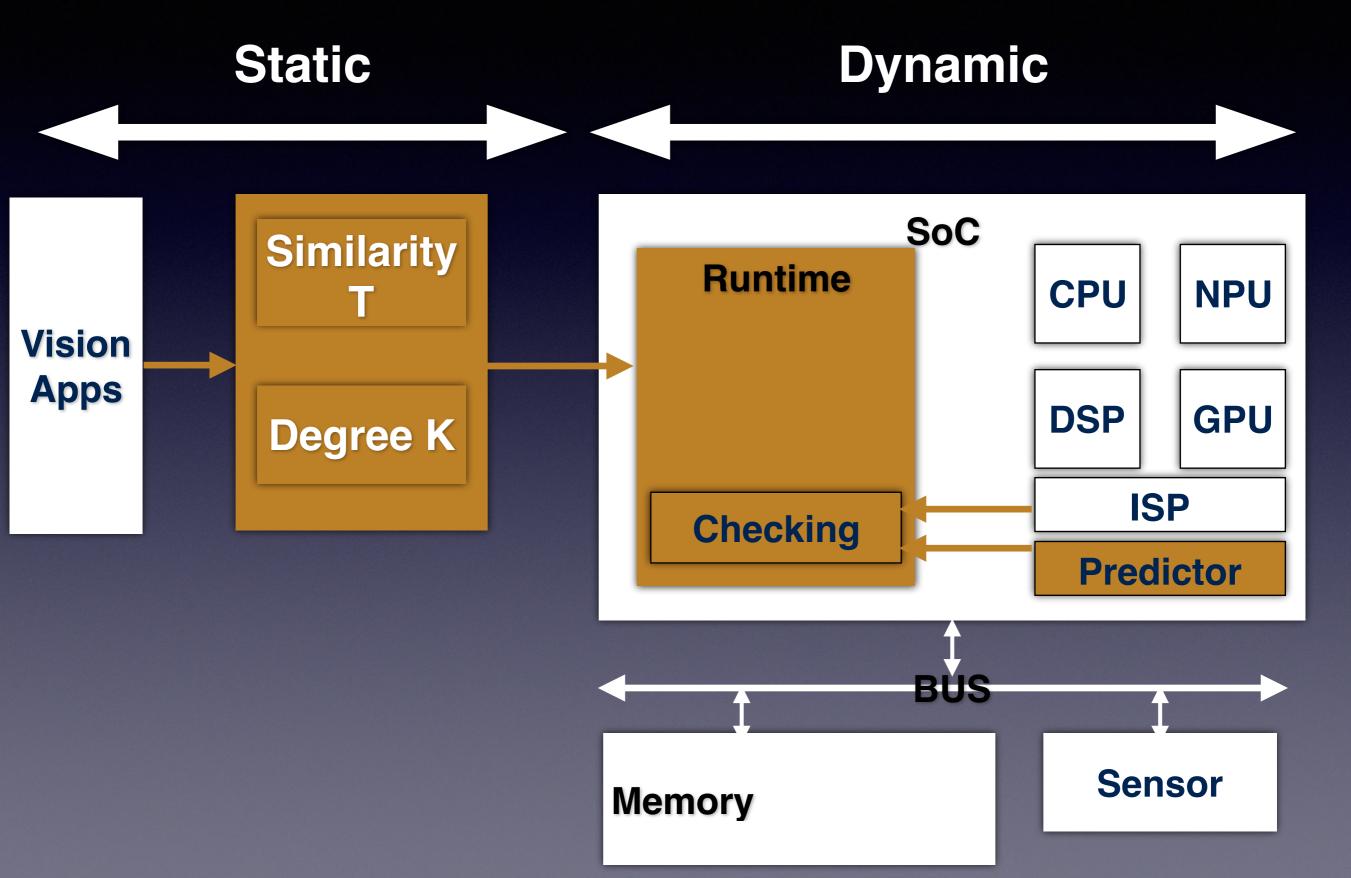

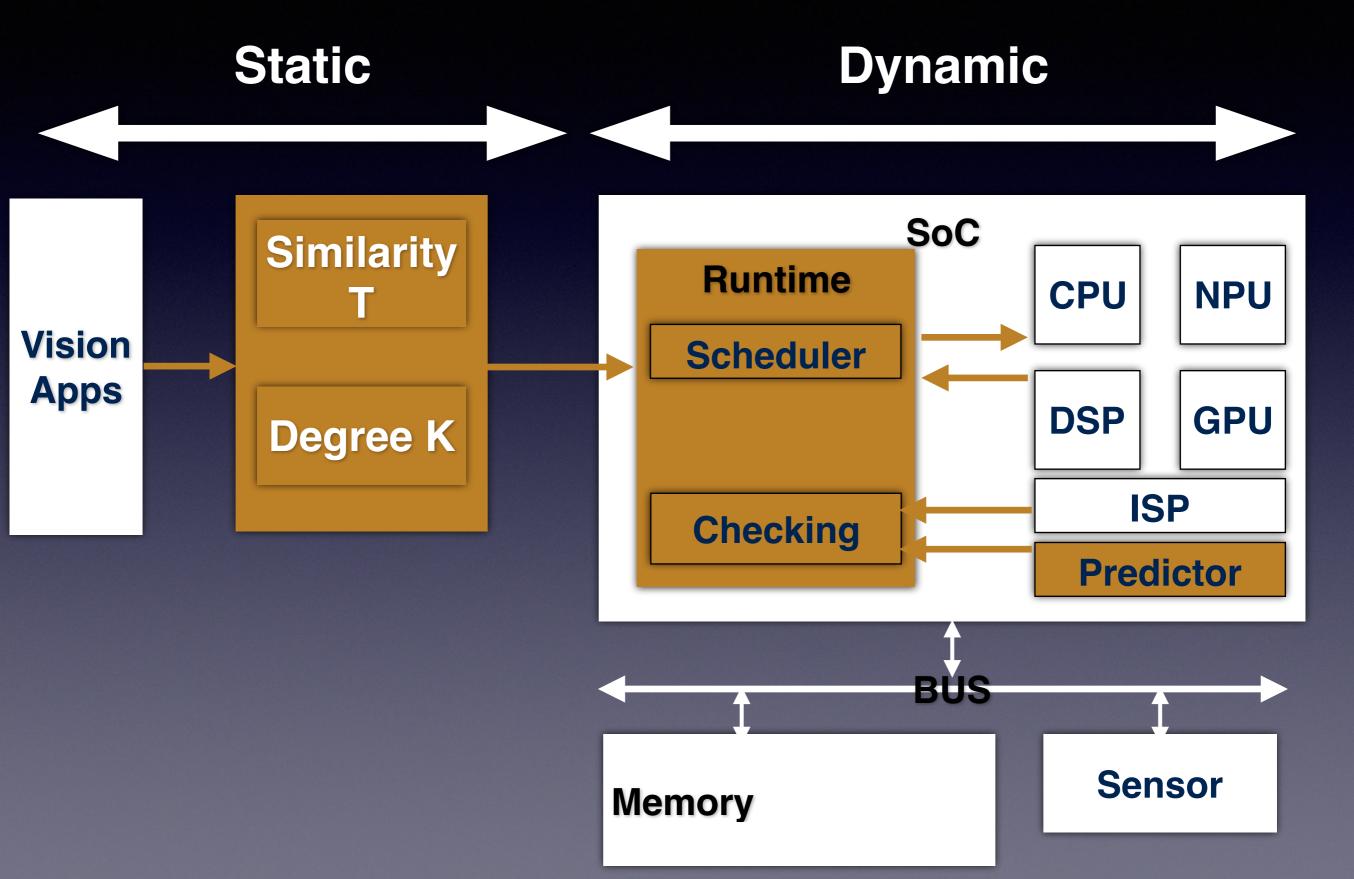

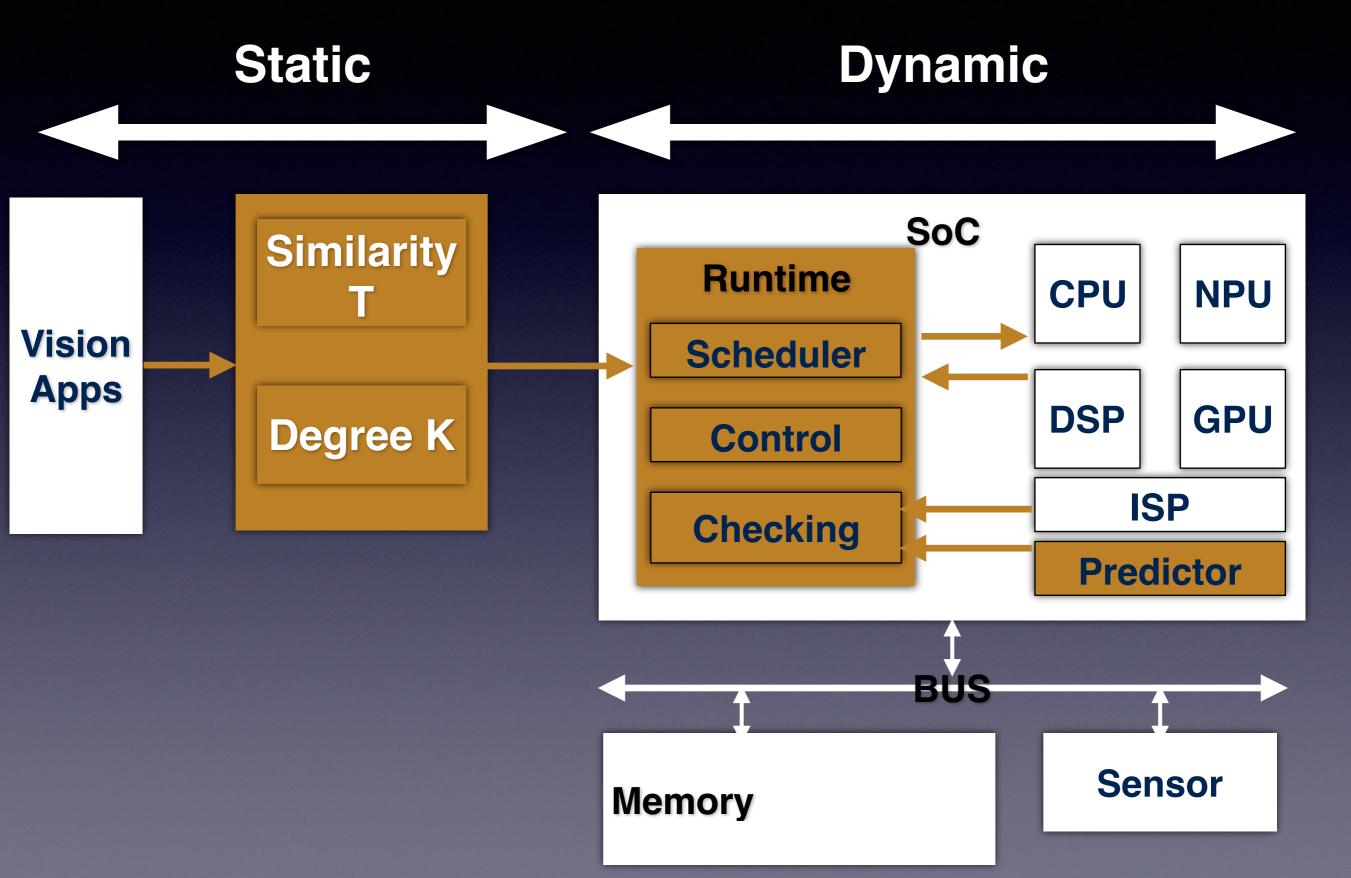

Relaxing Checking Criterion (Threshold T)

Relaxing Checking Criterion (Threshold T)

Relaxing Checking Frequency (Degree K)

# Frames Sequence

Precise Frames

UncheckedPredicted Frames

CheckedPredicted Frames

**Time**

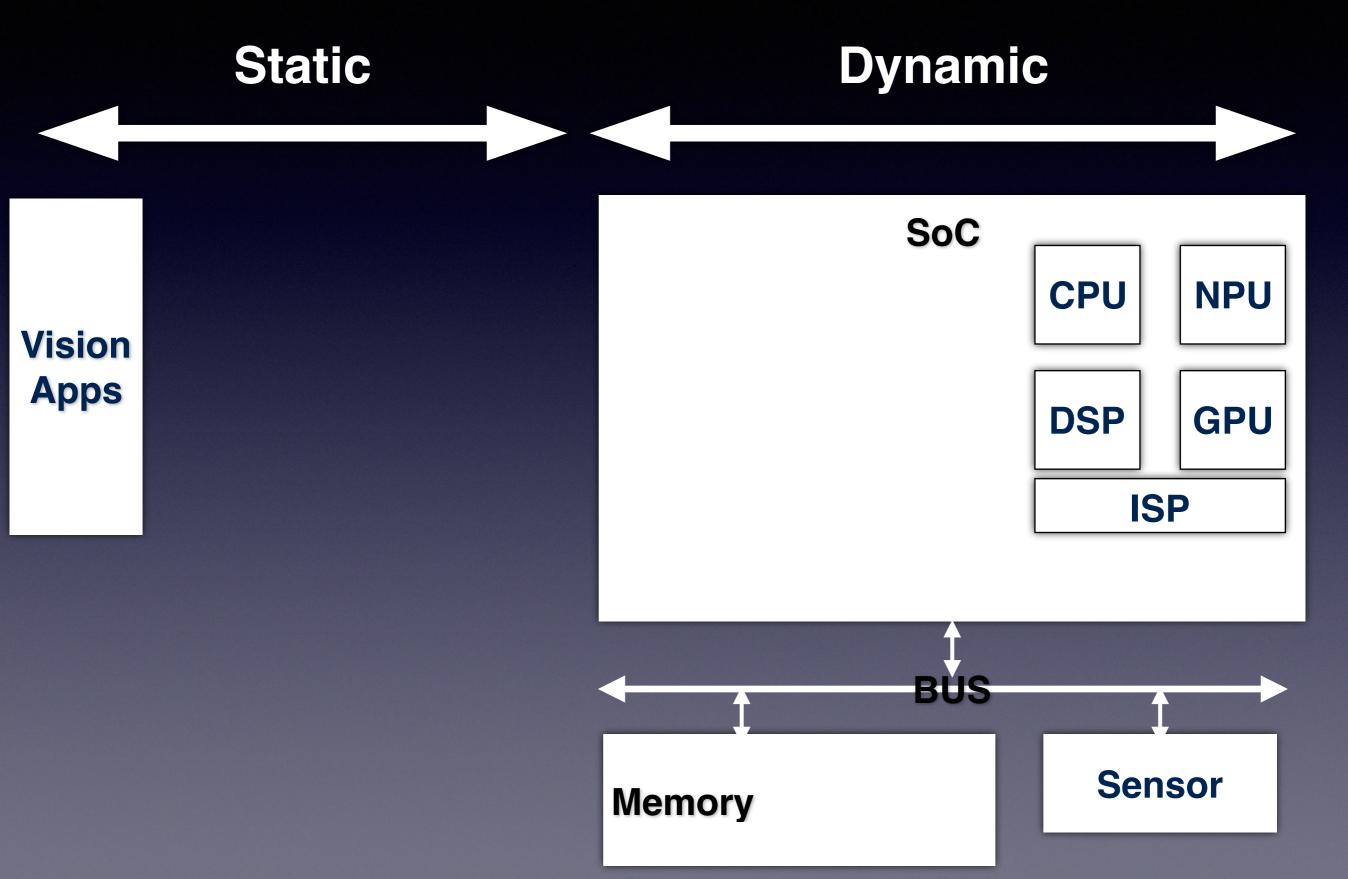

#### I. In house simulator modeling state-of-the art SoCs

Real measurement of latency and energy on different IPs.

#### I. In house simulator modeling state-of-the art SoCs

Real measurement of latency and energy on different IPs.

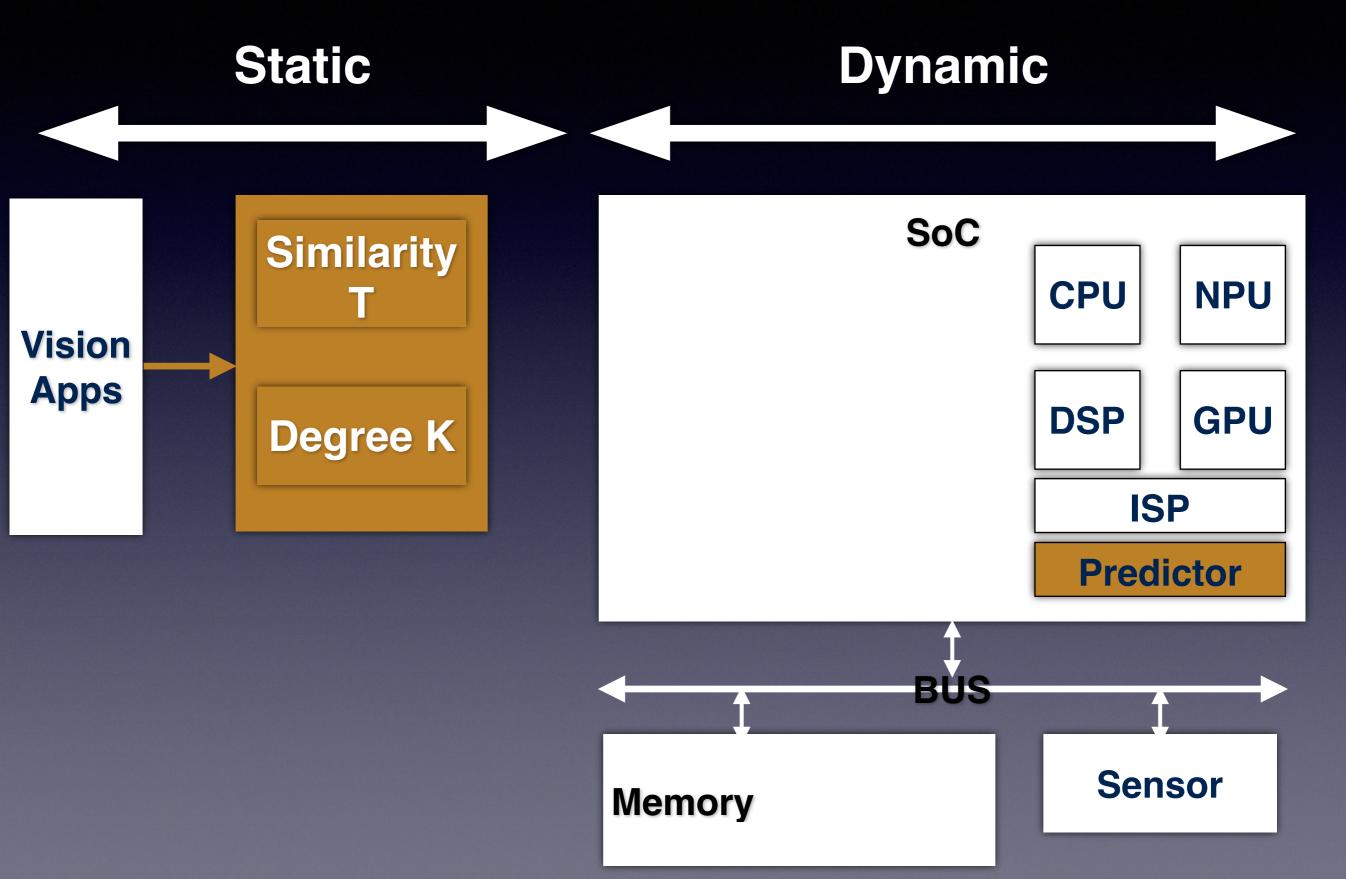

#### II. RTL Implementations for NPU and Predictor

20x20 Systolic Array for NPU, 10x10 Systolic Array for Predictor

#### I. In house simulator modeling state-of-the art SoCs

Real measurement of latency and energy on different IPs.

#### II. RTL Implementations for NPU and Predictor

20x20 Systolic Array for NPU, 10x10 Systolic Array for Predictor

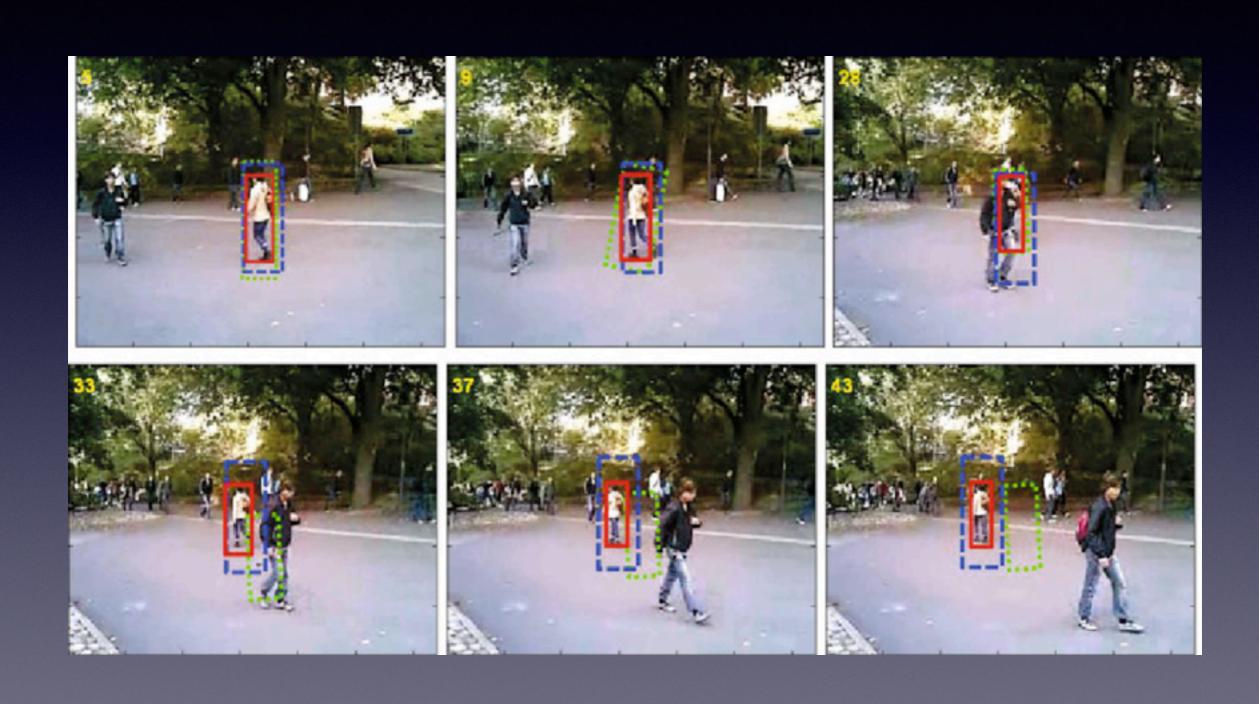

#### III. Evaluate on Object Detection and Tracking

KITTI dataset for object detection, VOT-challange for tracking.

#### I. In house simulator modeling state-of-the art SoCs

Real measurement of latency and energy on different IPs.

#### II. RTL Implementations for NPU and Predictor

20x20 Systolic Array for NPU, 10x10 Systolic Array for Predictor

#### III. Evaluate on Object Detection and Tracking

KITTI dataset for object detection, VOT-challange for tracking.

#### IV. Different Input Resolutions

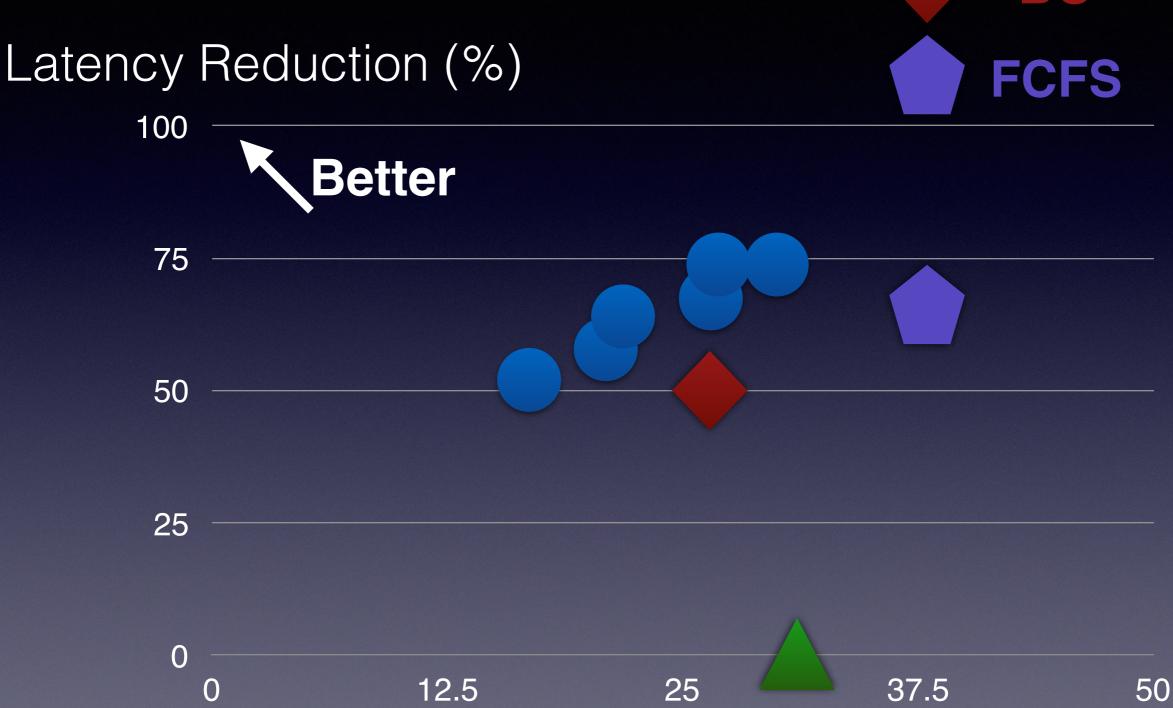

### Baselines

#### I. Base

Baseline with traditional execution pipeline

#### II. BO

Baseline with optimized back-end

#### III. FCFS

Traditional pipeline with multiple hardware IPs

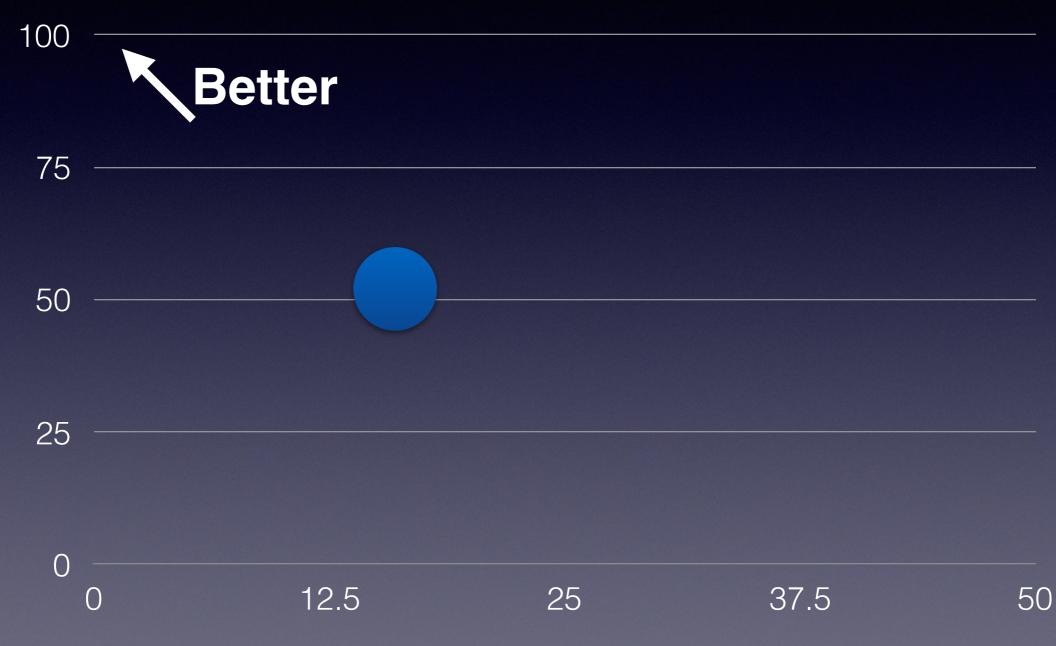

### Results

Latency Reduction (%)

Energy Budget (mJ)

# Results

Latency Reduction (%)

Energy Budget (mJ)

# Results

Energy Budget (mJ)

### Conclusion

#### I. Long Latency Bottleneck Continuous Vision

#### **II. Proactive Execution Pipeline**

- 1) Leveraging Heterogeneities in Mobile SoCs

- 2) Relaxed Checking

#### III. Non-mission-critical System

# Collaborators

Yuxian Qiu Jingwen Leng Lele Chen

Yuhao Zhu

# Questions